大家好,欢迎来到IT知识分享网。

基于Xilinx的数据手册pg007_SRIO的P1-55、P73-83得到以下SRIO接口知识:

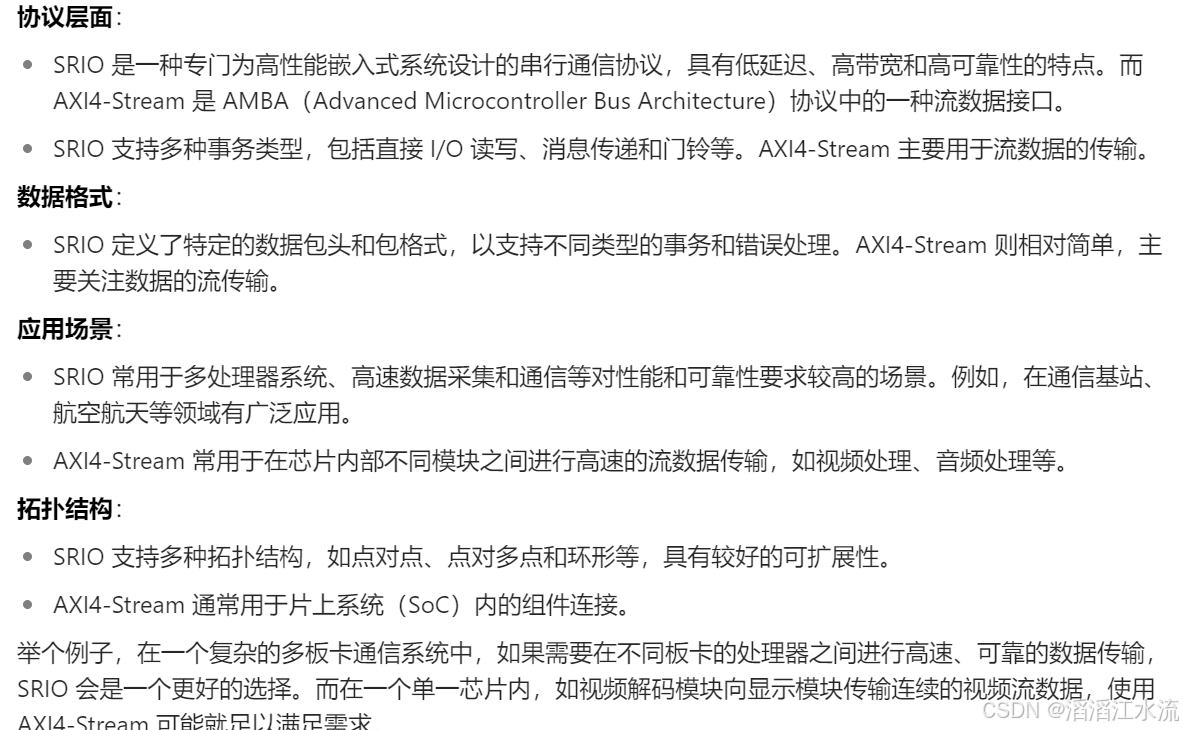

SRIO(Serial RapidIO,串行RapidIO)是一种用于高速差分串行通信协议。

(1)SRIO Gen2支持 1 路、2 路和 4 路(1x、2x、4x,“x”表示通道数,选择几lane,几组差分线,几个高速收发器通道)通道传输数据(选择lane的宽度,要考虑板子底层差分线数量是否支持)

(2)SRIO Gen2每个通道(per lane)传输速度支持 1.25、2.5、3.125、5.0 和 6.25 Gbaud

(3)SRIO Gen2使用简单的握手机制控制 AXI4-Stream接口进行高吞吐量数据传输,使用 AXI4-Lite接口进行配置、维护(联想到以太网的MAC核)

(4)SRIO Gen2兼容A7板卡,A7高速收发器是GTP,最大线速6.6Gbit/s,故SRIO Gen2通道最大速度是6.25Gbaud(木桶效应)

板间高速差分通信GTX—GTH,木桶效应,按照GTX(慢的)算

(5)SRIO(发数据和中断)用途:

1. FPGA与DSP进行通信

2. 含有高速收发器的俩板子//芯片(片间板间)进行通信,可以使用SRIO,但此方法并不是最优解

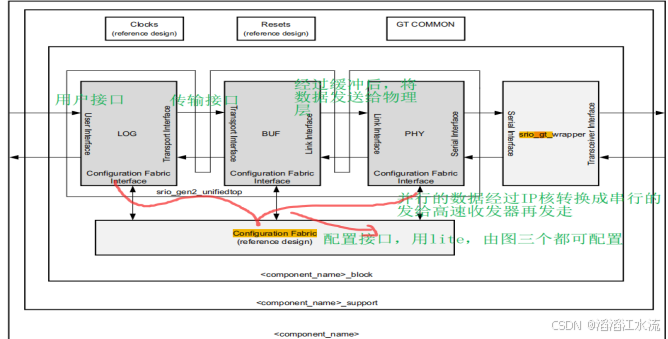

(6)SRIO Gen2 分三层:逻辑层、缓冲层、物理层

逻辑层:逻辑层定义整体协议和数据包格式。

缓冲层:接收发送缓存的包深度(8/16/32,通常默认或最大)

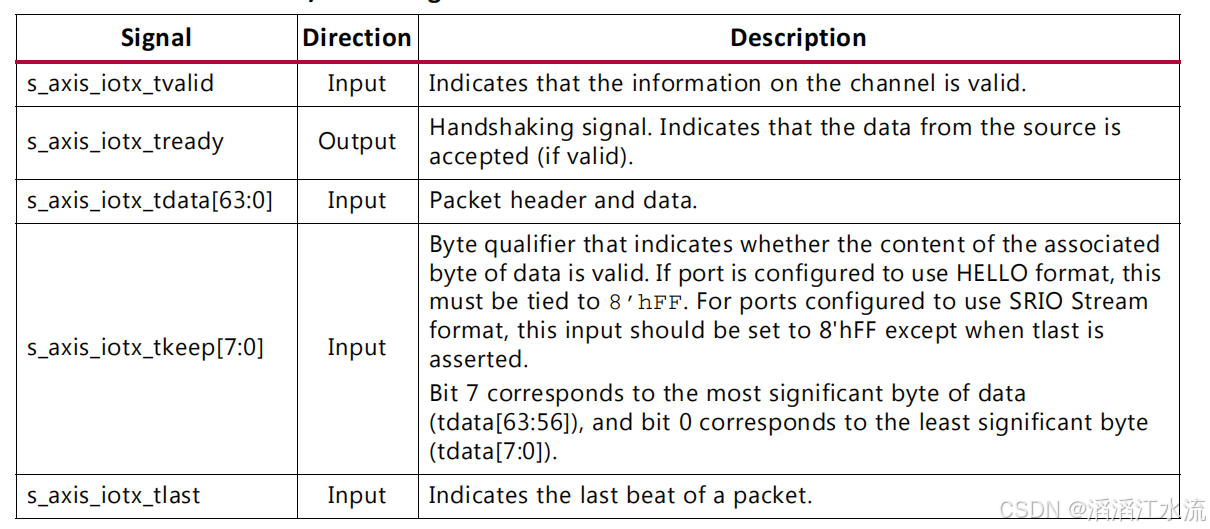

②接收引脚iorx:(同理)

• m_axis_iorx_tvalid(数据发送方SRIO IP核提供),m_axis_iorx_tready(数据接收方我提供)

(3)两种传输数据包格式:

• HELLO (精简包,不是一种包格式,里面还包含许多包格式)

• SRIO Stream(标准包,结构复杂)

SRIO使用AXI4-stream发送数据相比AXI4-stream接口区别:

其他的呢,在这儿呢

SRIO的板间远端回环和单板近端回环:

(1)1个板子近端回环,我们使用的是近端回环,1个板子调2个SRIO IP核自己和自己发

1个板子回环过程:数据生成模块APP使用AXI4-stream协议发送HELLO数据包到SRIO1 IP核,在SRIO1 IP核将数据包转化成高速收发器接口的形式发送到SRIO2 IP核,在SRIO2 IP核对包进行解析,以AXI4-stream接口形式发送到APP,形成回环

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/112256.html