大家好,欢迎来到IT知识分享网。

外部存储器接口(EMIF)

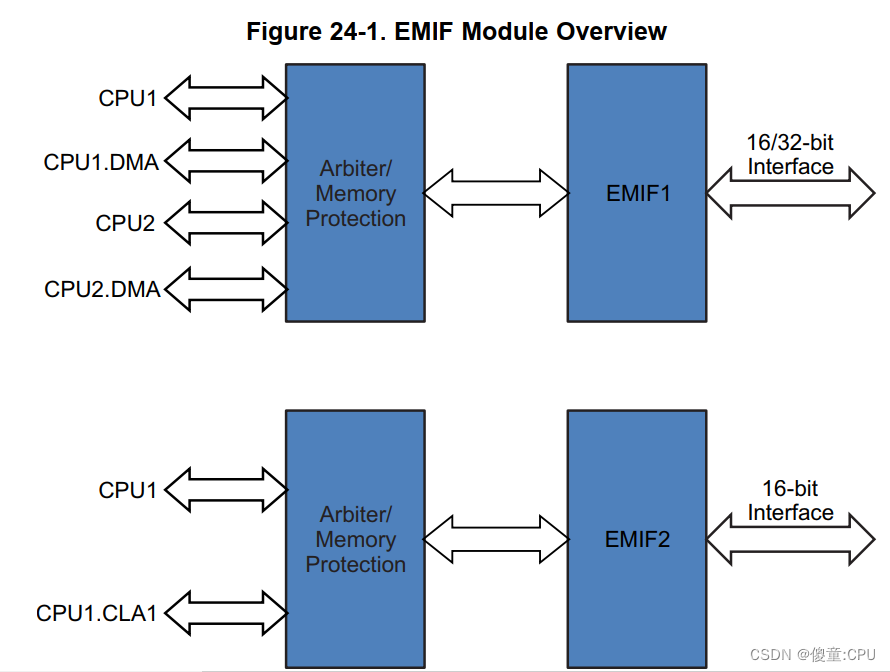

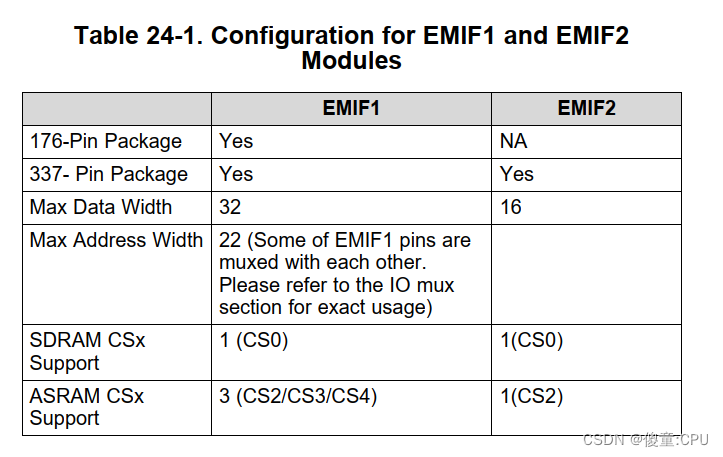

该设备支持双核架构;为了为每个CPU子系统提供一个专用的EMIF,该设备支持两个EMIF模块——EMIF1和EMIF2。两个模块完全相同,具有相同的功能集,但具有不同的地址/数据大小。EMIF1在CPU1和CPU2子系统之间共享,而EMIF2专用于CPU1子系统。

在该设备上,如果EMIF1被选择为具有32位数据宽度,则不能使用EMIF2,因为EMIF2数据引脚与EMIF1 MSB数据引脚复用。

外围设备的用途

特性

EMIF控制器包括许多功能,以增强连接到外部SDR SDRAM和异步设备的方便性和灵活性。

支持异步内存

支持同步DRAM内存

功能框图

配置设备引脚

GPIO多路复用器寄存器必须配置为将此外围设备连接到设备引脚。为了避免引脚出现故障,必须首先配置GPyGMUX位(同时将相应的GPyMUX位保持为默认值零),然后将GPyMUX寄存器写入所需值。某些IO功能是由GPIO寄存器设置定义的,与此外围设备无关。对于输入信号,应通过将适当的GPxQSELn寄存器位设置为11b,将GPIO输入资格设置为异步模式。内部上拉可以在GPyPUD寄存器中进行配置。有关GPIO多路复用器和设置的更多详细信息,请参阅GPIO章节。

EMIF模块体系结构

提供有关EMIF的体系结构和操作的详细信息。SDRAM和异步接口以及其他与系统相关的配置(如时钟控制)都包含在内。

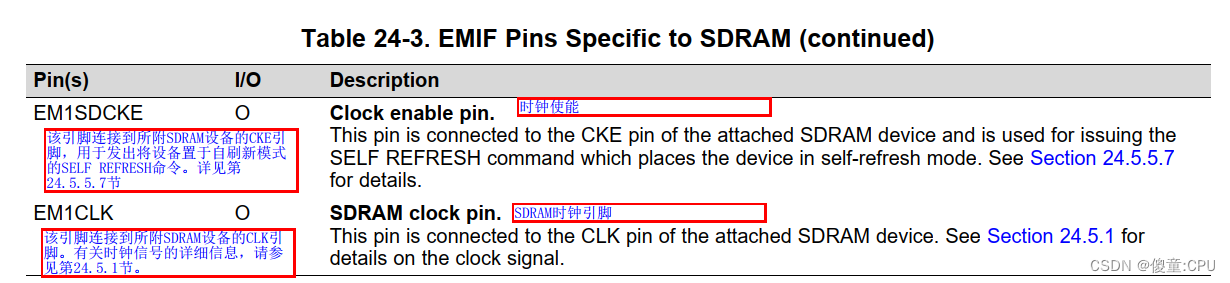

EMIF时钟控制

EMIF时钟在EM1CLK引脚上输出,应在与外部SDRAM设备接口时使用。EMIF模块获得PLLSYSCLK时钟域作为输入。用户可以通过配置时钟控制模块中PERCLKDIVSEL寄存器中的EMIF1CLKDIV字段,选择以PLLSYSCLK/1或PLLSYSCL K/2时钟频率运行EMIF。

EMIF请求

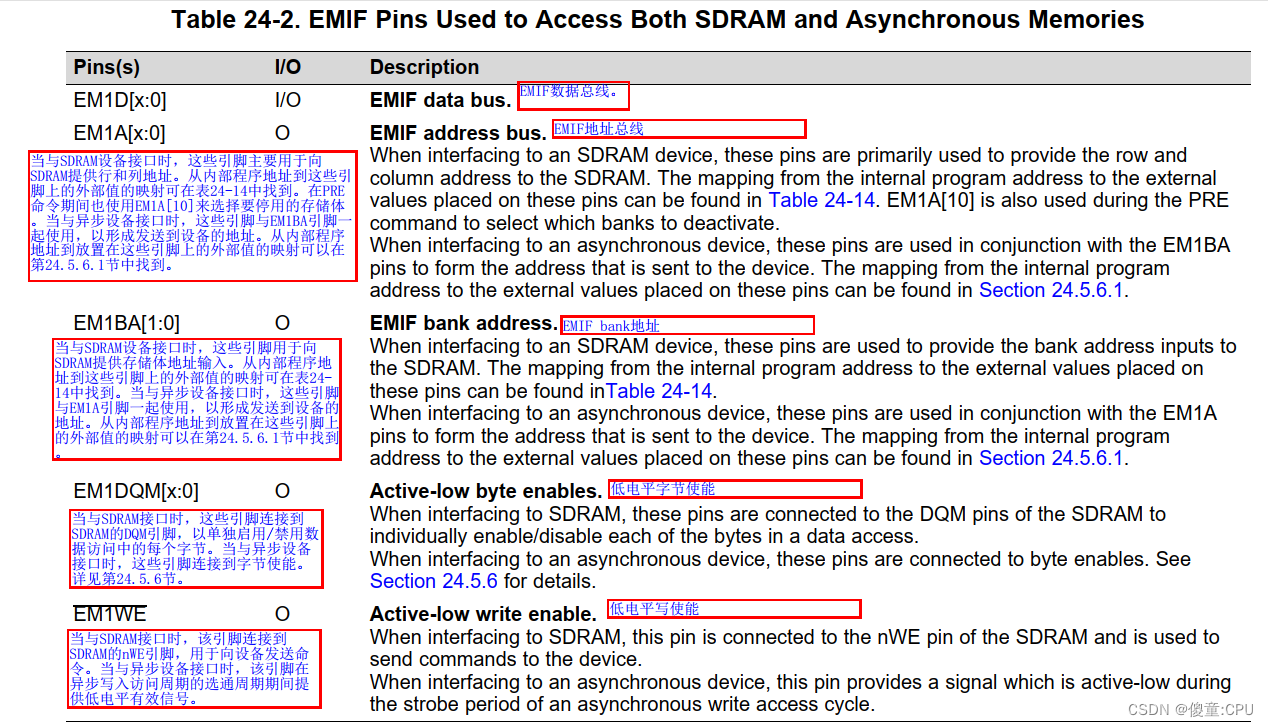

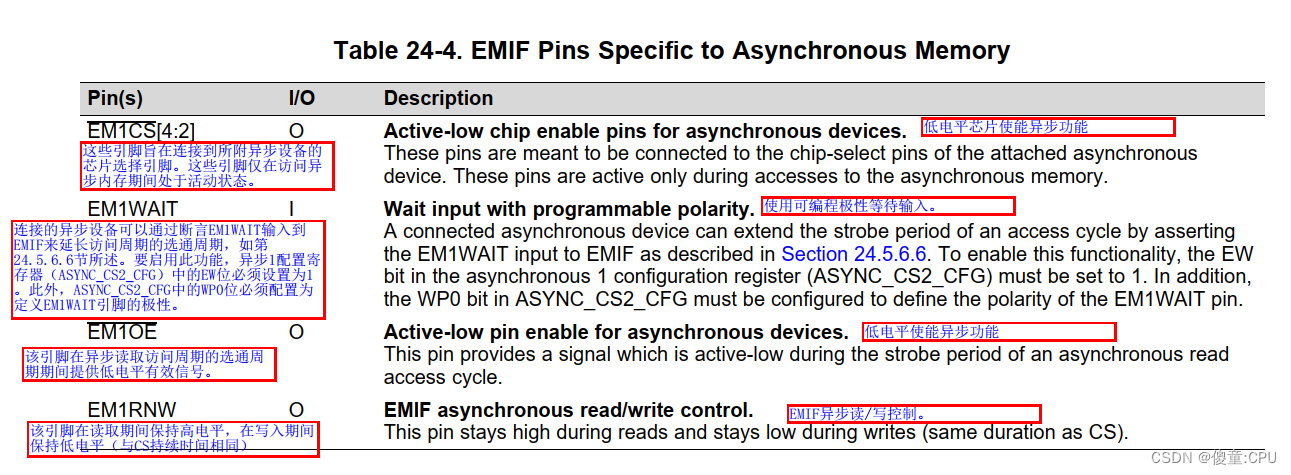

EMIF信号说明

SDRAM控制器和接口

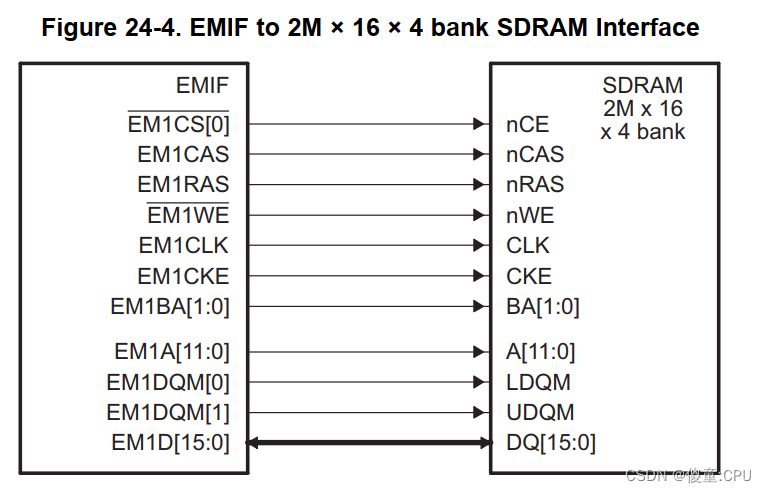

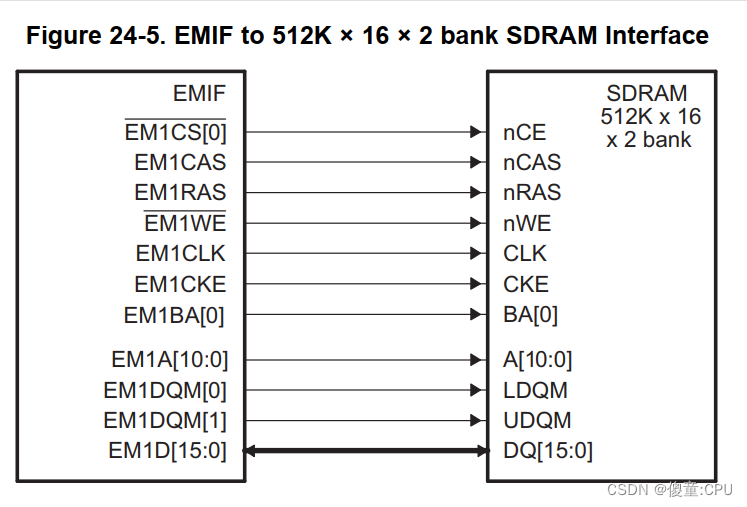

EMIF控制器为大多数标准SDR SDRAM设备提供无胶接口,并支持自刷新模式和优先刷新等功能。此外,它还通过可编程参数提供了灵活性,如刷新率、CAS延迟和许多SDRAM时序参数。以下部分详细介绍了如何接口和正确配置EMIF,以便对外部连接的SDR SDRAM设备执行读写操作。此外,提供了将EMIF与通用SDRAM设备接口的详细示例。

SDRAM命令

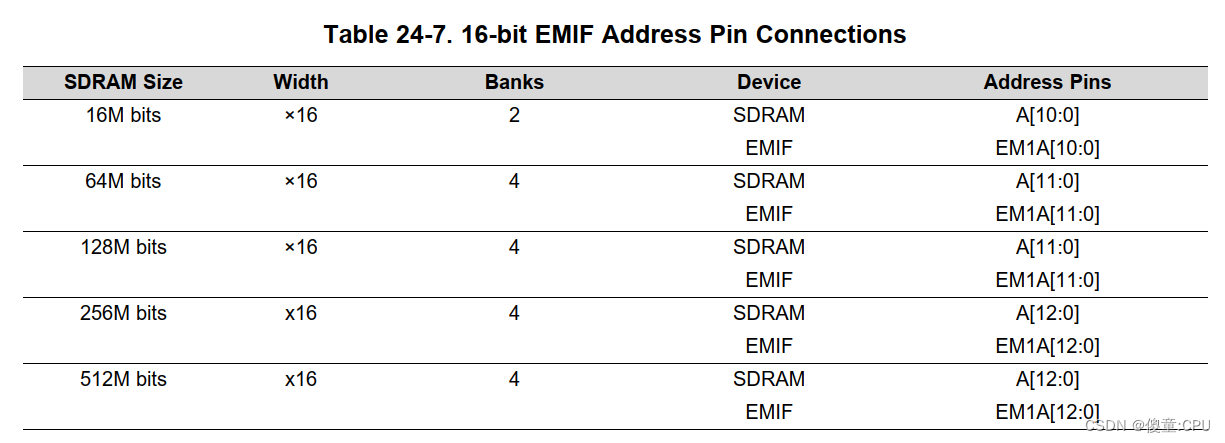

SDRAM的接口

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/112892.html