大家好,欢迎来到IT知识分享网。

CMOS基本电路

这一部分在教材上,不仅讲了各种门电路是怎么样的,还讲了很复杂的静态、动态工作状态分析,还有各个工作点电压电流的计算等,个人觉得没有必要写在这里。这下面就讲这么一些东西吧:

- 与或非以及与非、或非等基本逻辑门电路的CMOS实现

- 以非门为例,介绍逻辑电路中普遍存在的传输延时现象

- 学会使用TINA观察逻辑门电路的动态与静态特性

- 开漏和推挽输出

- 传输门、三态门

- 常见CMOS分立元件实物介绍、特点、选型推荐

CMOS逻辑门电路实现

CMOS逻辑门中,非门是最简单的一种,下面就从非门开始介绍,并且描述怎么去观察数字电路的动态和静态传输特性,数字电路需要关注的问题等。后面几种与非门、或非门什么的,只需要给出电路图,大家按照非门的方法自己就会分析他们的各项特性了。

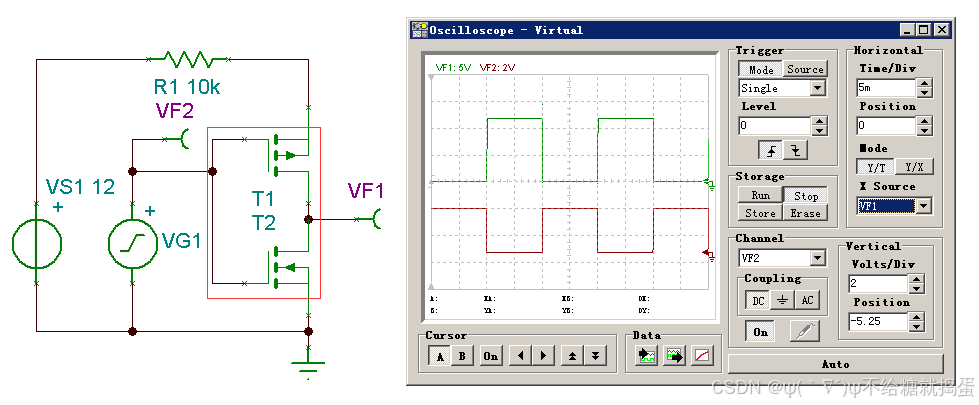

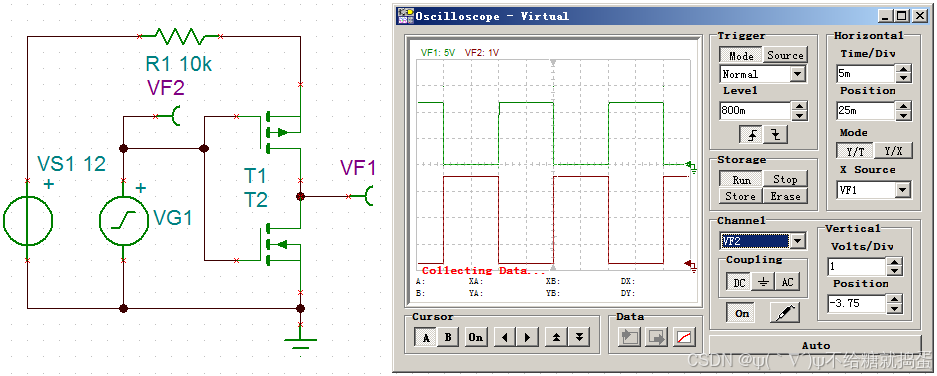

一个最简单的CMOS非门(反相器)的电路如下:

红框内是反相器,示波器中红色的是输入,绿色的是输出,输入输出正好是反过来的。反相器仅仅由一个NMOS和一个PMOS组成,当输入是高电平时,下面的NMOS导通而上面的PMOS不导通,所以输出通过NMOS接地为低电平。当输入为低时,下面的NMOS截止而上面的PMOS导通,输出接到高电平为高。

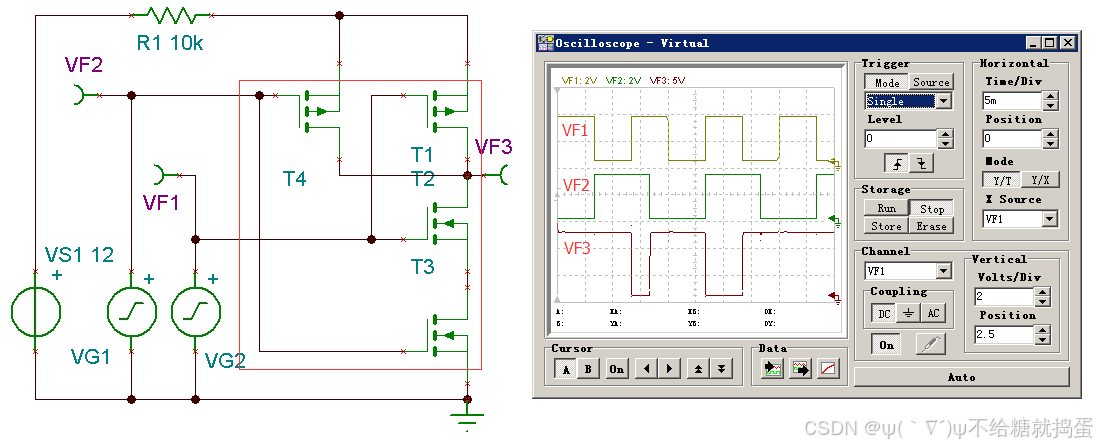

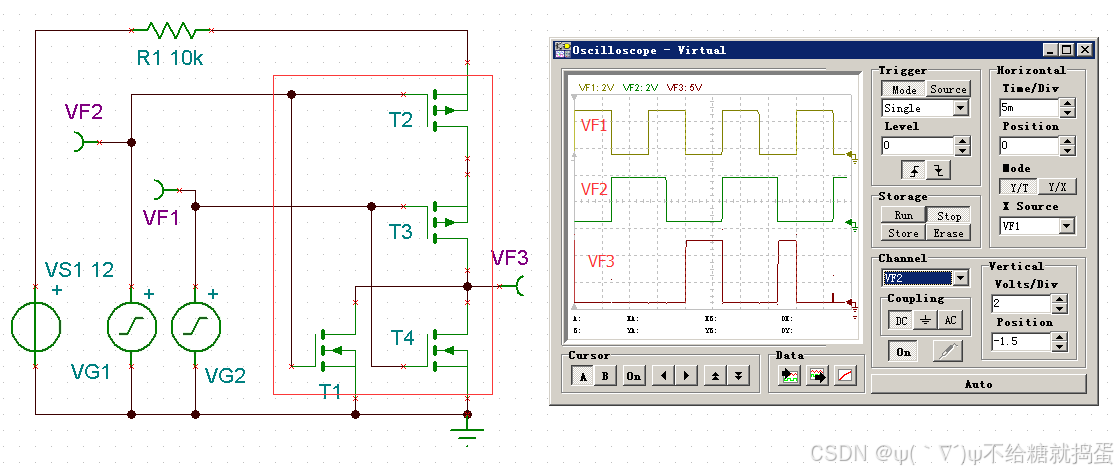

类似的,与非门的电路图如下:

红框里面的是与非门,看看示波器里面VF1 VF2输入和输出VF3的关系,是不是就是与非。

或非门的电路图如下:

CMOS逻辑门的传输特性

首先解释下传输特性是个啥意思,上面的电路图和示波器的波形图,描述的都是静态场景下的逻辑关系,比如给定一个输入,看这个电路的输出是什么。本来作为嵌入式软件的开发来讲,根据这个关系知道怎么写代码去驱动数字电路就够了。但是我们的电路就像CPU里面一样,是在不停运算不停变化的,在输入的信号极快速变化的时候,会因为CMOS的传输特性出现我们意料之外的情况导致电路无法正常工作。

传输延迟现象

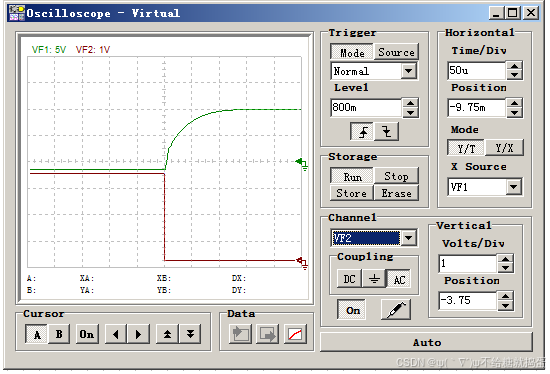

最常见的变化信号就是方波,我们给反相器电路输入一个方波试试。

可以看到输出并不是像我们想像的那样,随着输入的下落,立马就跃变到高电平,而是像爬坡一样缓慢上升到高电平,可以看到示波器我调的是50us一格,也就是说它花了大概100us爬升上去,这就是电路中存在的传输延迟现象,也就是指输出信号并不能严格跟随输入信号变化的现象。

传输延迟的影响

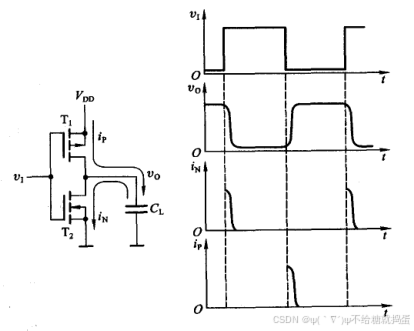

我们不先急着搞清楚为什么会有这个鬼问题,先看看他有什么影响,如果影响不严重其实也可以暂时不深究他是为什么。下图是引用自教材《数字电路技术基础》的图:

从上面的图中可以看到,因为传输延迟的存在,导致上下两个CMOS无法严格的一起进行切换,在输入跳变的瞬间产生从VDD到地的通路,电流从上到下流经两个CMOS产生功率消耗,这就是CMOS电路的动态功耗。

所以,我们就可以很容易的理解,为什么生活中电脑CPU工作频率越高,发热就越大,CPU超频需要使用液氮冷却就是这么来的。

传输延迟的原因

我们理解到传输延迟会造成动态功耗损耗(后面还会介绍会造成竞争-冒险现象,这里先不提),那这个问题的根本原因是什么呢?其实就是电路中的电容在作怪。

我们还是看上面的一张图,非门的输出画了一个电容,这个电容包含两部分:

- 负载的电容,包括后级CMOS电路或者其他容性负载的电容

- CMOS电路本身的分布电容和杂散电容

其中第二项我们知道电容的形成条件非常简单,只需要两个隔得足够近的金属就可以形成,CMOS内部也是通过金属走线的,导线之间就会形成微小的分布电容和杂散电容,所以即使CMOS后面的电路没有电容,内部也会有容性存在。即使第二部分的电容一般非常小,但是在CMOS工作频率越高的时候,上述的影响就越明显。

后续大家如果学习自己画PCB,也会碰到这种问题,在高频PCB(一般超过几十兆赫兹就会体现出来了)上一般要非常注意走线,防止分布与杂散电容对电路产生不利影响。

传输延迟影响的避免

- 减少高频率工作状态

- 使用传输延迟更低的CMOS芯片

- 合理PCB布局,减少负载电容

实际使用有些时候不可避免的要使用更高的频率,我们着手更多的是第二点和第三点,比如74HC04芯片传输延迟一般在9ns,而74AHC04只有5ns。合理的PCB布局也是一种很重要的方法,特别是在高频的时候。虽然高频的时候,更多的考虑的是信号完整性的东西,减少杂散电容也是一个考虑之一,有些要求比较高的板子,从两层板切换到4层板也有这个原因。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/127636.html