大家好,欢迎来到IT知识分享网。

EPWM总体介绍

感兴趣的可以去看原文:

【玻尔电子DSP28335基础视频教程】https://www.bilibili.com/video/BV1hs411T7Ft?p=6&vd_source=5cc408d7c45546e0092d7d6d6d2f26bb

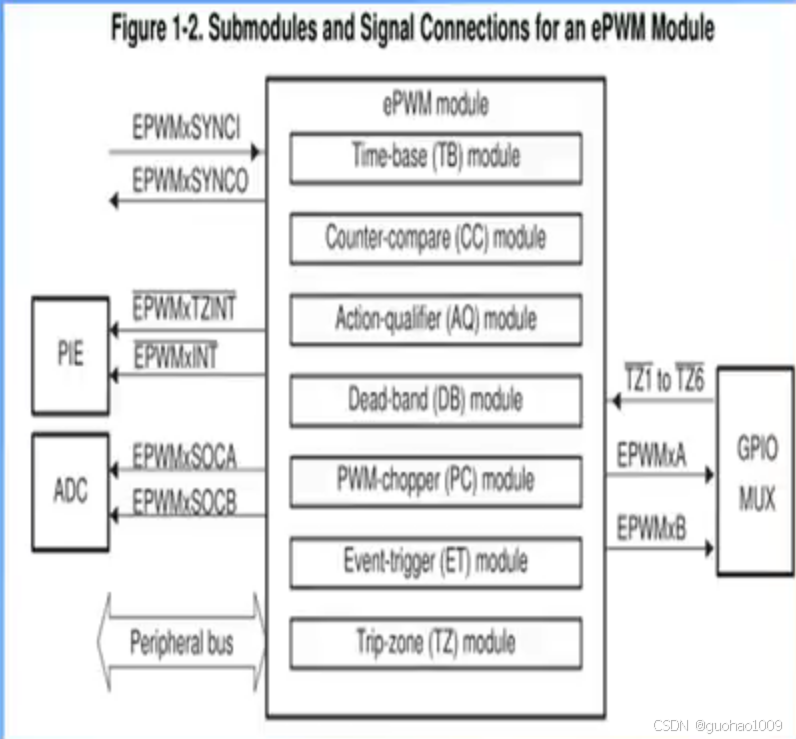

EPWM结构框图:

上承PIE,下接GPIO

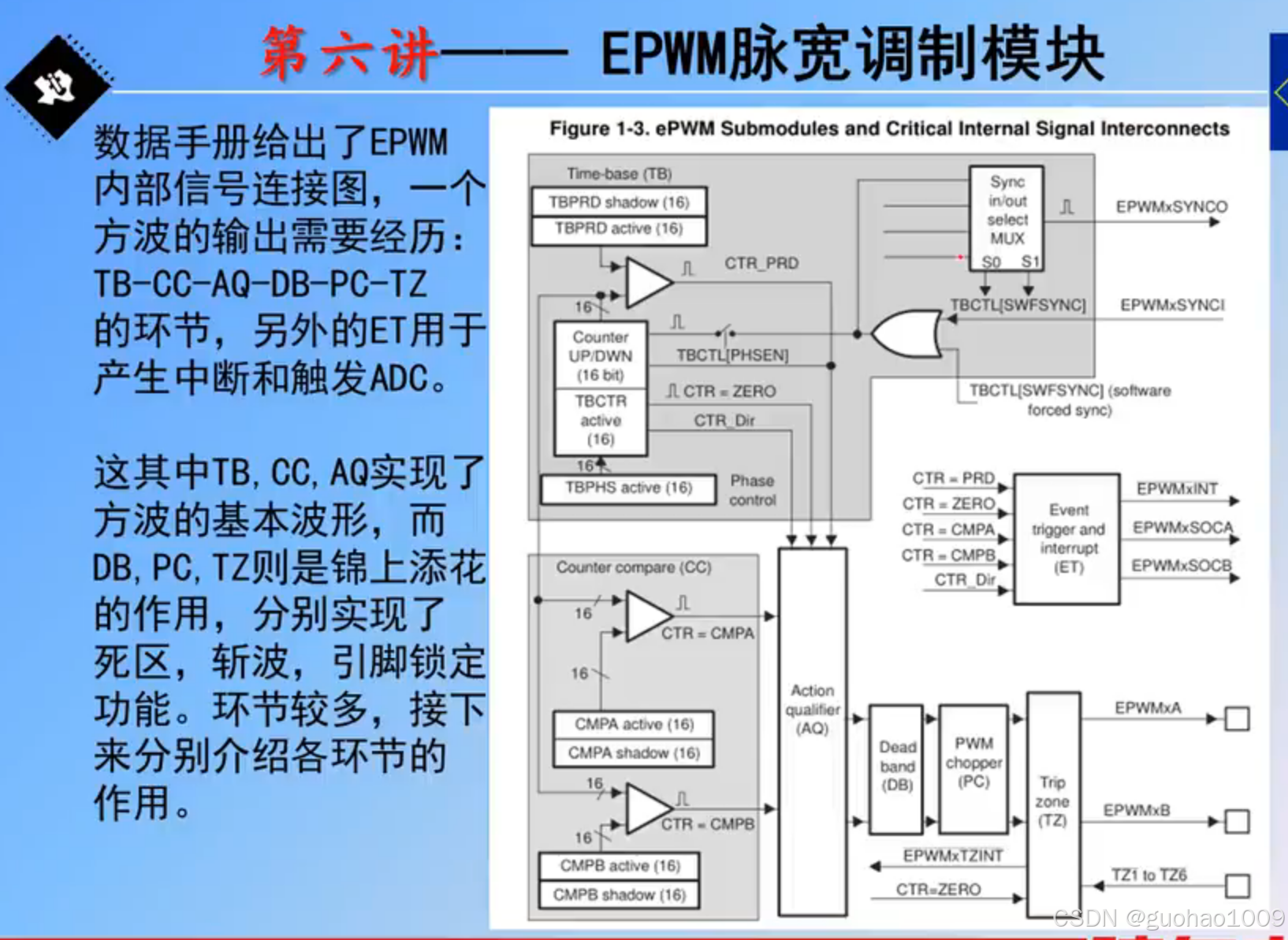

EPWM的子模块:TB-时间基准子模块、CC-比较子模块、AQ-动作子模块、DB-死区子模块、PC-斩波子模块、ET-事件触发子模块、TZ-故障子模块

方波输出需要经历:TB-CC-AQ-DB-PC-TZ,另外ET用于触发ADC中断

下面重点介绍 TB时间基准子模块、CC比较子模块、AQ动作子模块

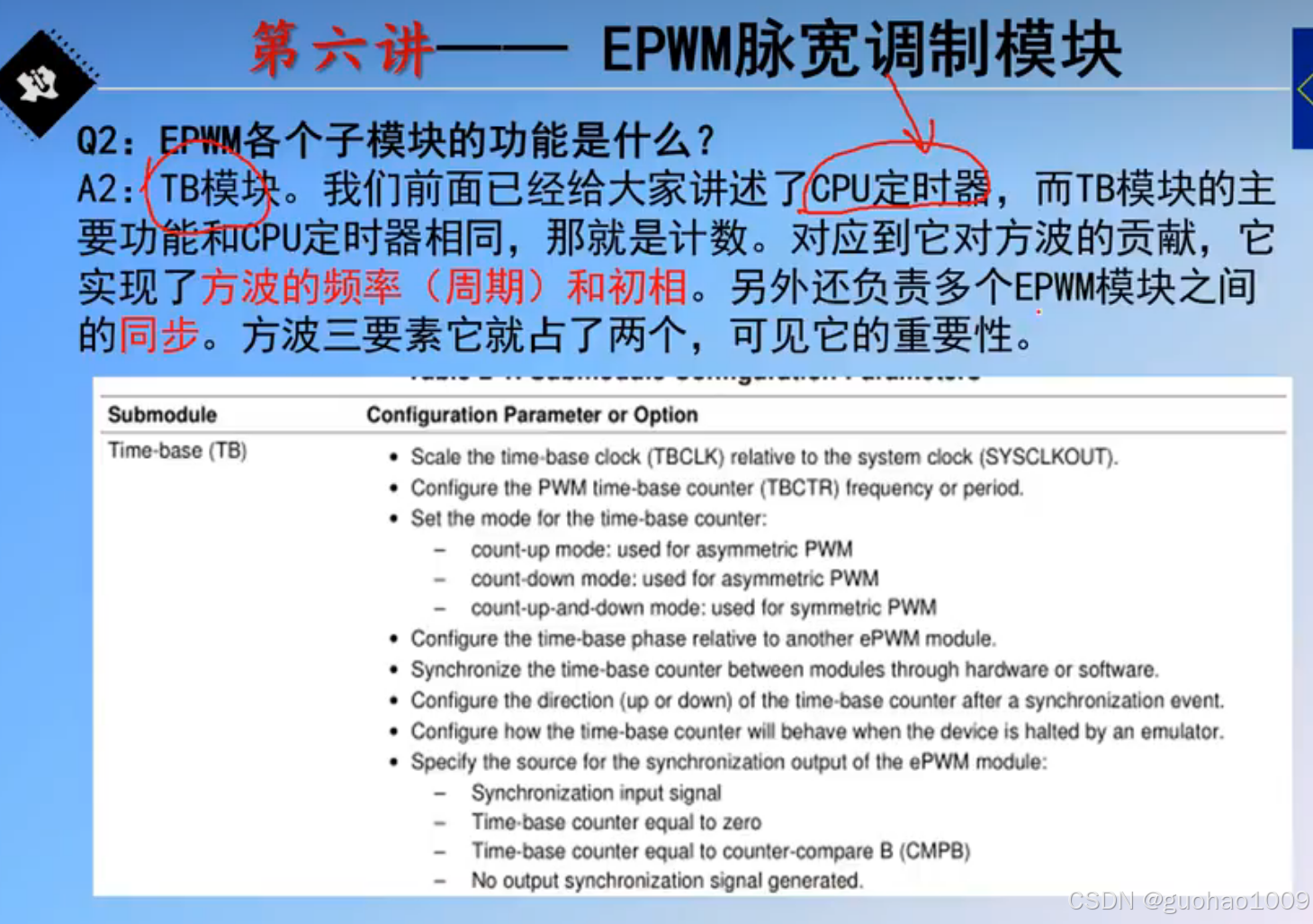

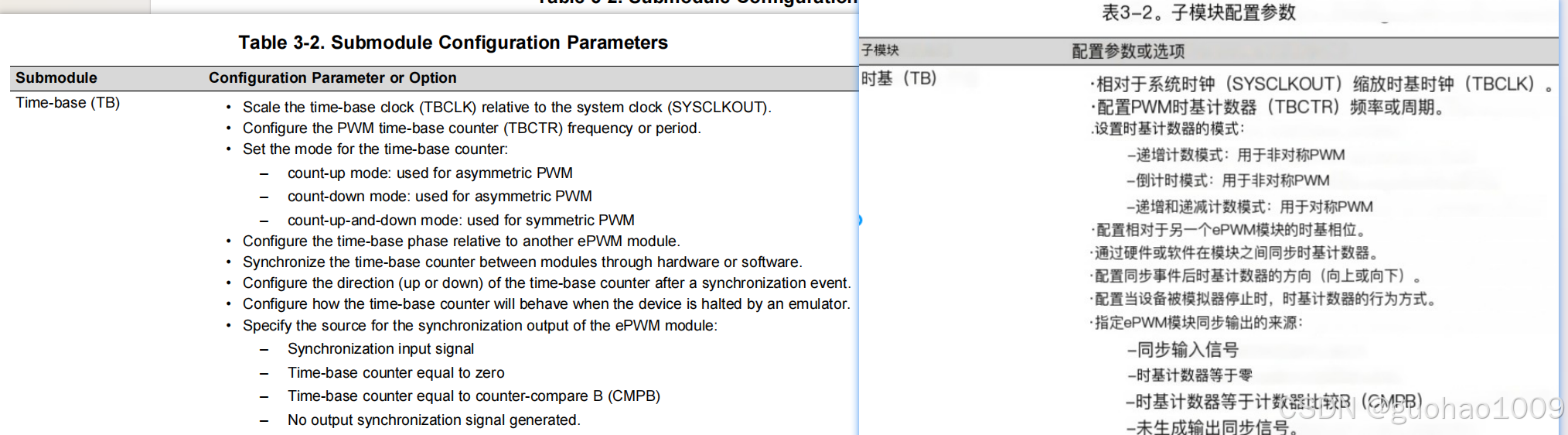

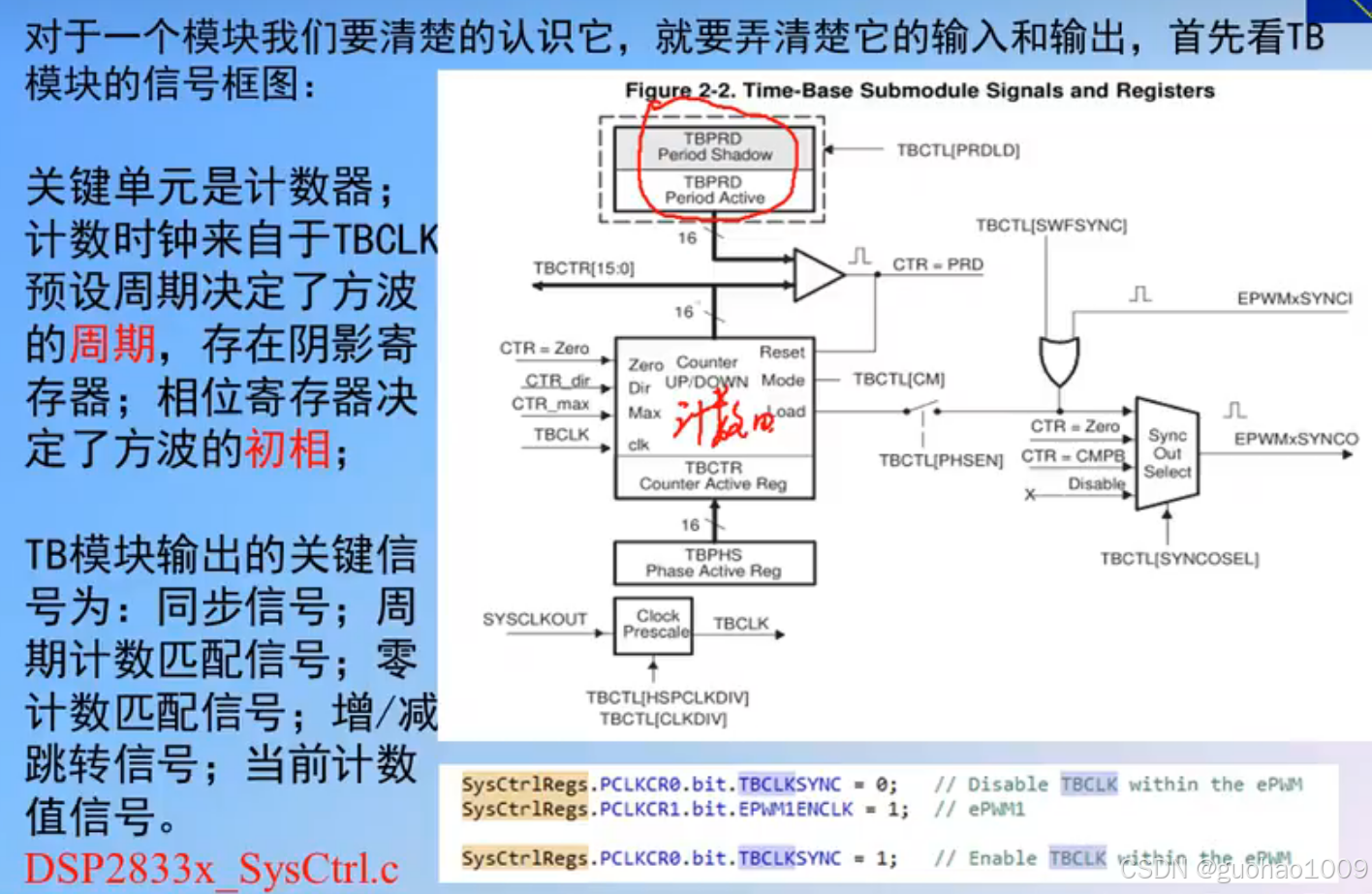

TB时间基准子模块

类似于 CPU的定时器模块;但CPU-Tim的计数方式仅为减计数,而TB模块有 增、减、增减(中心)3种计数模式

TB模块定义了方波的

(1)频率(周期)(2)初始相位 (3)负责多EPWM的同步功能

数据手册相关介绍

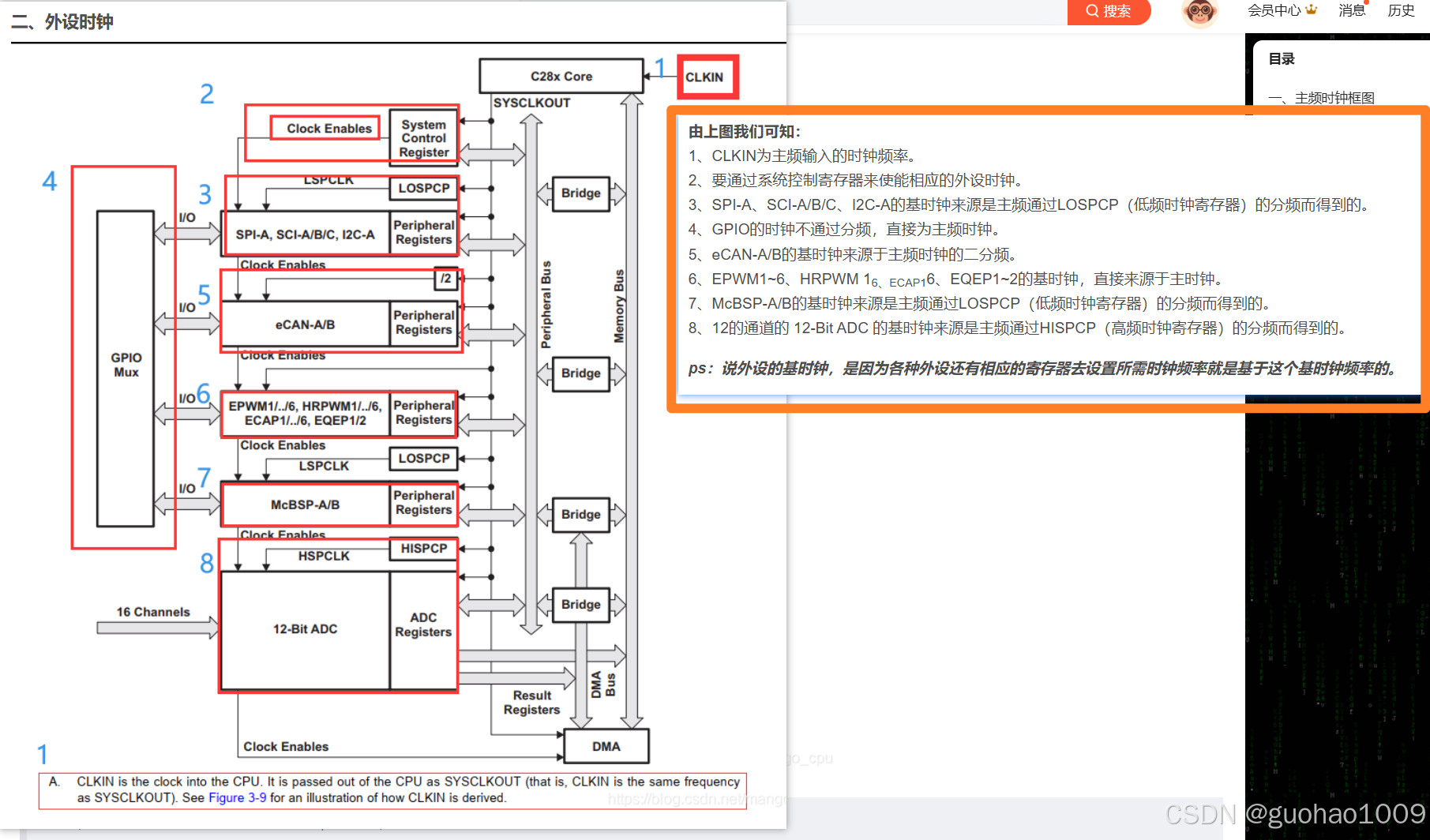

EPWM的时钟源:参考

一、DSP_TMS320F28335_时钟系统详细说明_tms320f28335 主频设置-CSDN博客

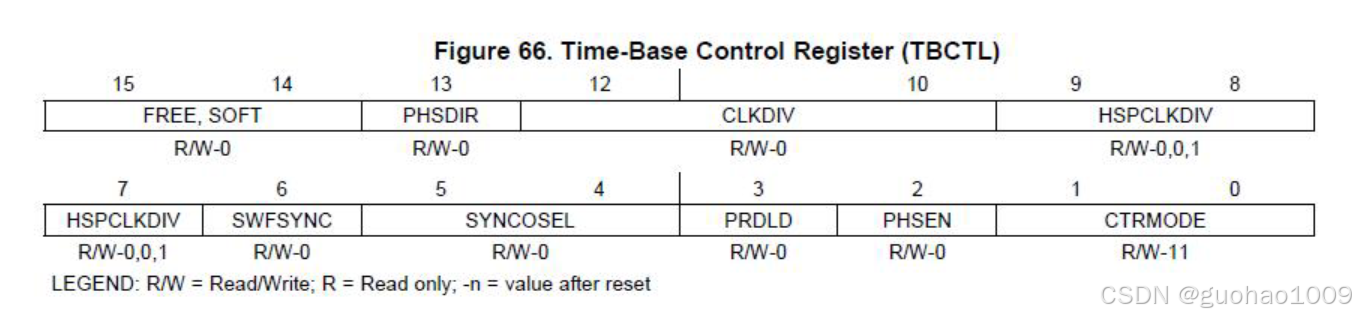

其时钟由 SYSCLKOUT(150Mhz默认)经过 时钟分频器TBCTL的HSPCLKDIV和CLKDIV

得到 TBCLK

TB时间基准子模块结构

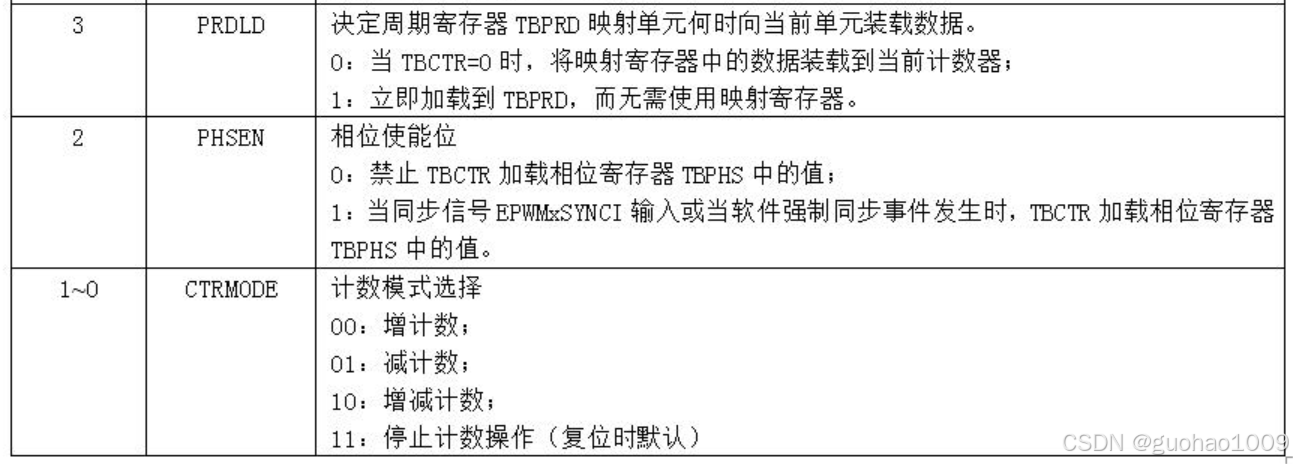

TB时间基准子模块相关寄存器

TB的操作步骤

1、在 PLL中配置 外设时钟源

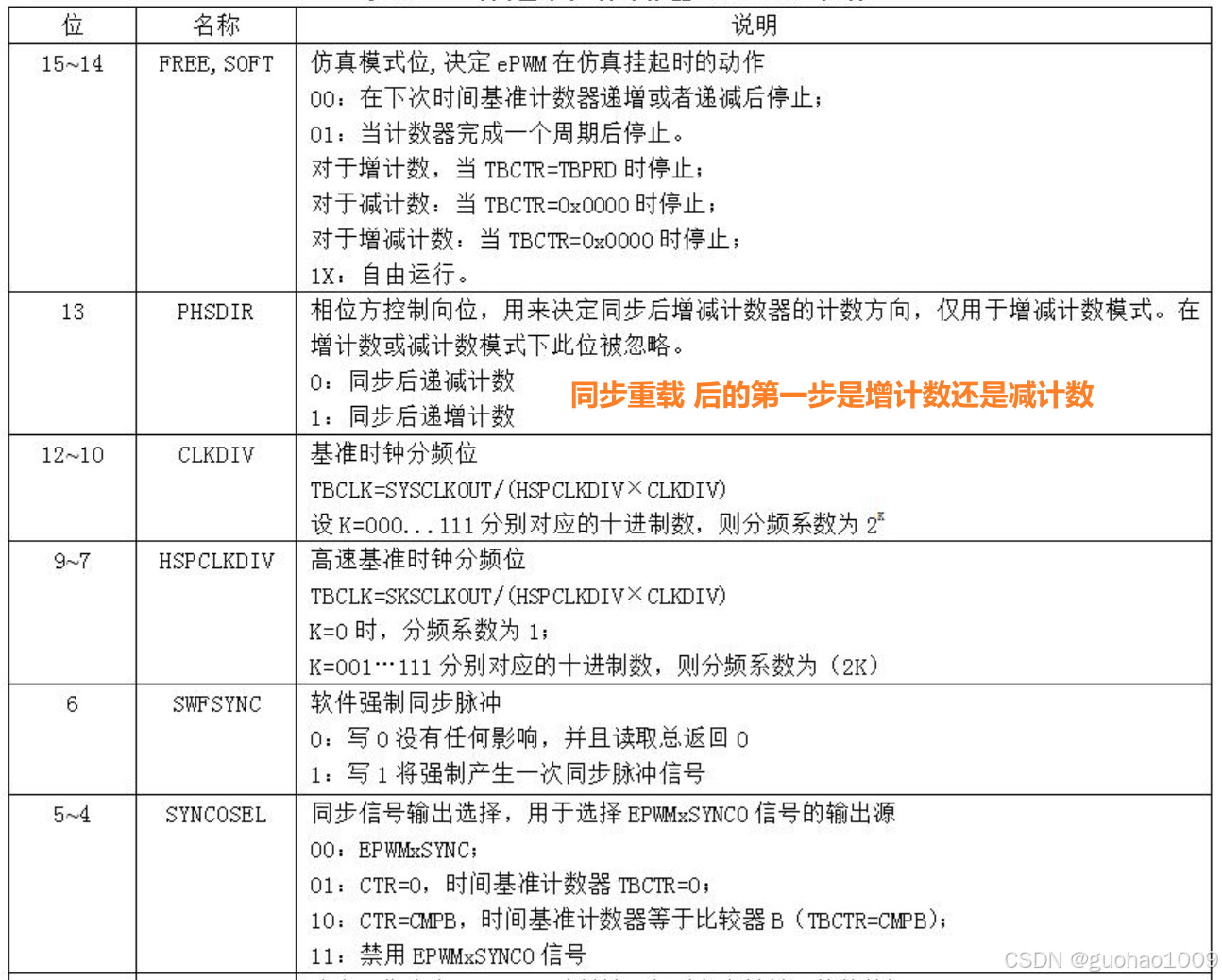

//在PCLKCR1寄存器中启用ePWM模块时钟 EALLOW; SysCtrlRegs.PCLKCR1.bit.EPWM1ENCLK = 1; EDIS; //将TBCLKSYNC设置为0 EALLOW; SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0; EDIS;2、配置TB计数器参数

//配置预分频器值和ePWM模式 EALLOW; EPwm1Regs.TBCTR = 0; //计数器清零 // Period = 1600 TBCLKcounts Tpwm=2*TBPRD*Ttbclk,100表示10k EPwm1Regs.TBPRD= /100; //周期 T1Period=EPwm1Regs.TBPRD; // Set Phaseregister to zero 将相位寄存器设置为零 EPwm1Regs.TBPHS.half.TBPHS = 0; //相位 EPwm1Regs.TBCTL.bit.FREE_SOFT=0; //自由运行 EPwm1Regs.TBCTL.bit.PHSDIR=1; //同步后 递增计数 EPwm1Regs.TBCTL.bit.CLKDIV=CLKDIV_EPWM1Val; //分频器 EPwm1Regs.TBCTL.bit.HSPCLKDIV=HSPCLKDIV_EPWM1Val; //高速时钟分频器 EPwm1Regs.TBCTL.bit.SYNCOSEL=0x3; //禁用EpwmxSYNC信号 EPwm1Regs.TBCTL.bit.PRDLD=0; //影子模式 EPwm1Regs.TBCTL.bit.PHSEN=0; //master //禁止相位功能 EPwm1Regs.TBCTL.bit.CTRMODE=2; //增减 中心计数3、使能时钟

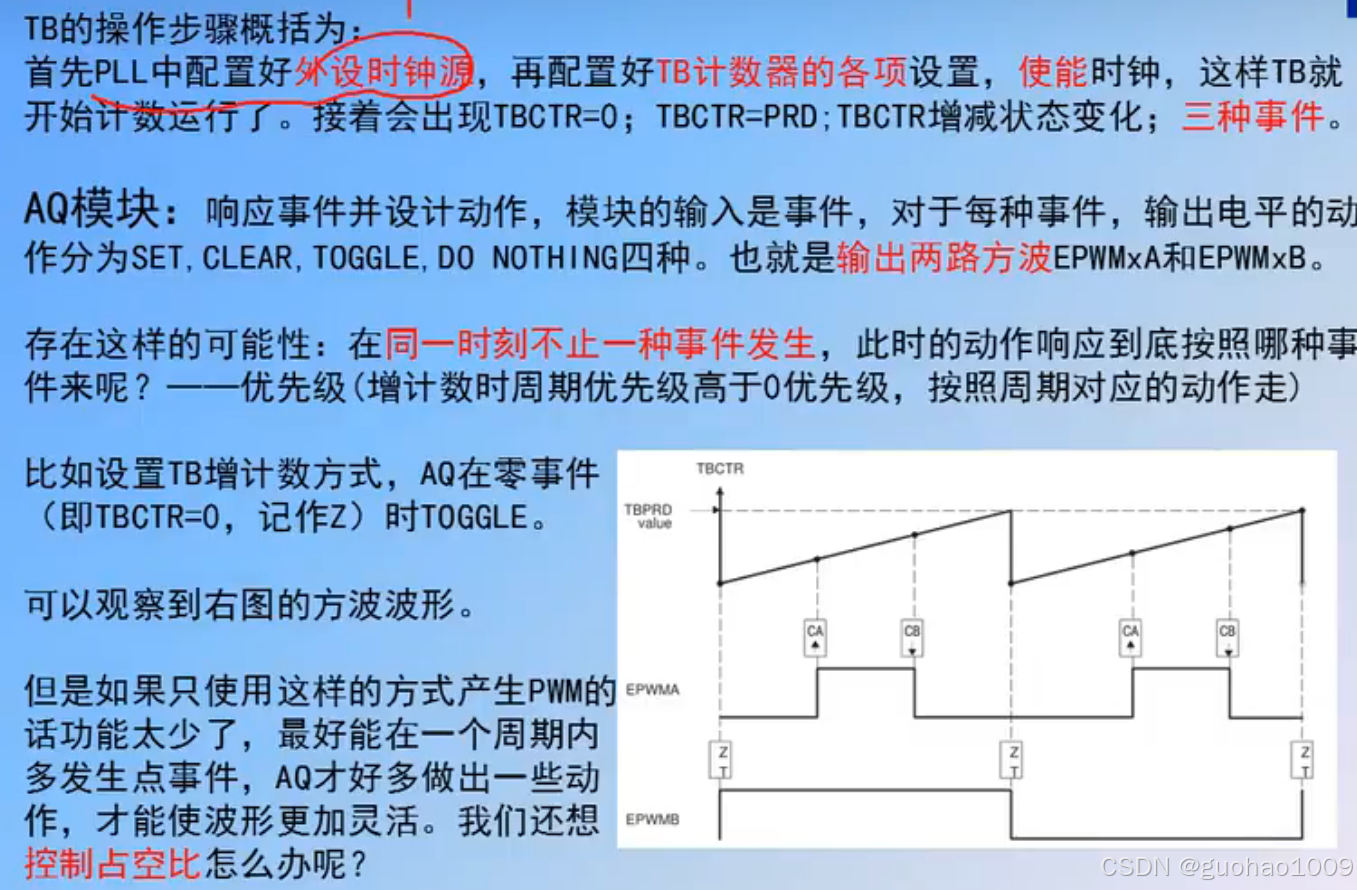

EALLOW; SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; EDIS;AQ-动作子模块

TBCTR = 0,TBCTR = PRD,TBCTR增减状态变化时;这三种情况均会产生事件

对于上述3种事件进行响应并设计动作;对于每种事件可分为4种动作:

SET、CLEAR、TOGGLE、DO NOTHING

但是在同一个时刻下,可能出现多种事件 在3种计数模式下均不同

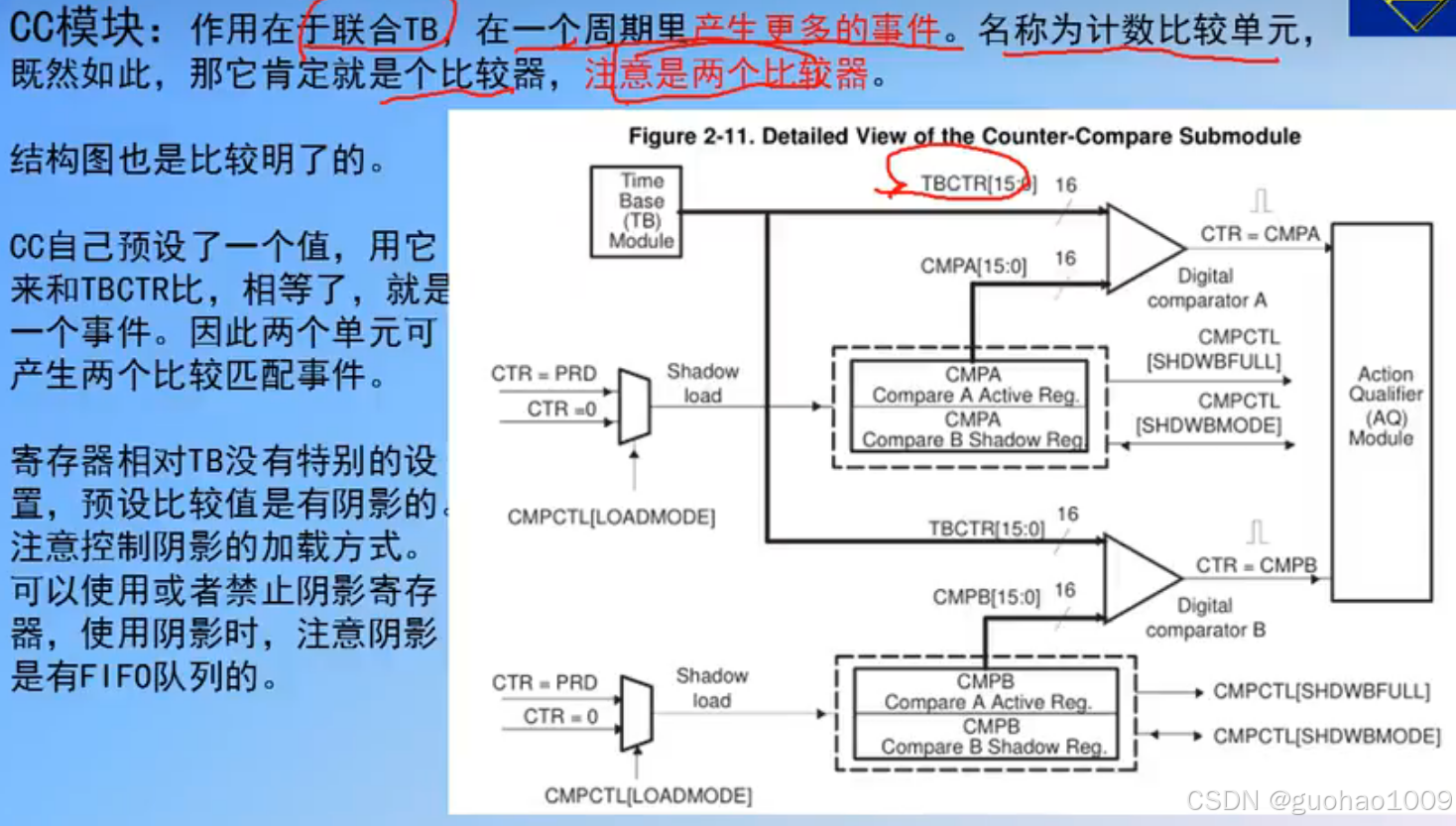

EPwm1Regs.AQCTLA.bit.CAU = Epwn1CAU; //向上计数 且=CMPA时 EpwmA 输出低电平 EPwm1Regs.AQCTLA.bit.CAD = Epwn1CAD; //向下计数 且=CMPA时 EpwmA 输出高电平CC-比较功能子模块

//cmpb影子装载,cmpa影子装载,均是过0装载 EPwm1Regs.CMPCTL.all=0x0000; //占空比 50% EPwm1Regs.CMPA.half.CMPA = /100/2; 由此处,PWM波形 的基本形状确立 ,下面是对于 DB-死区子模块,PC-斩波子模块,TZ-故障子模块进行修饰性设计

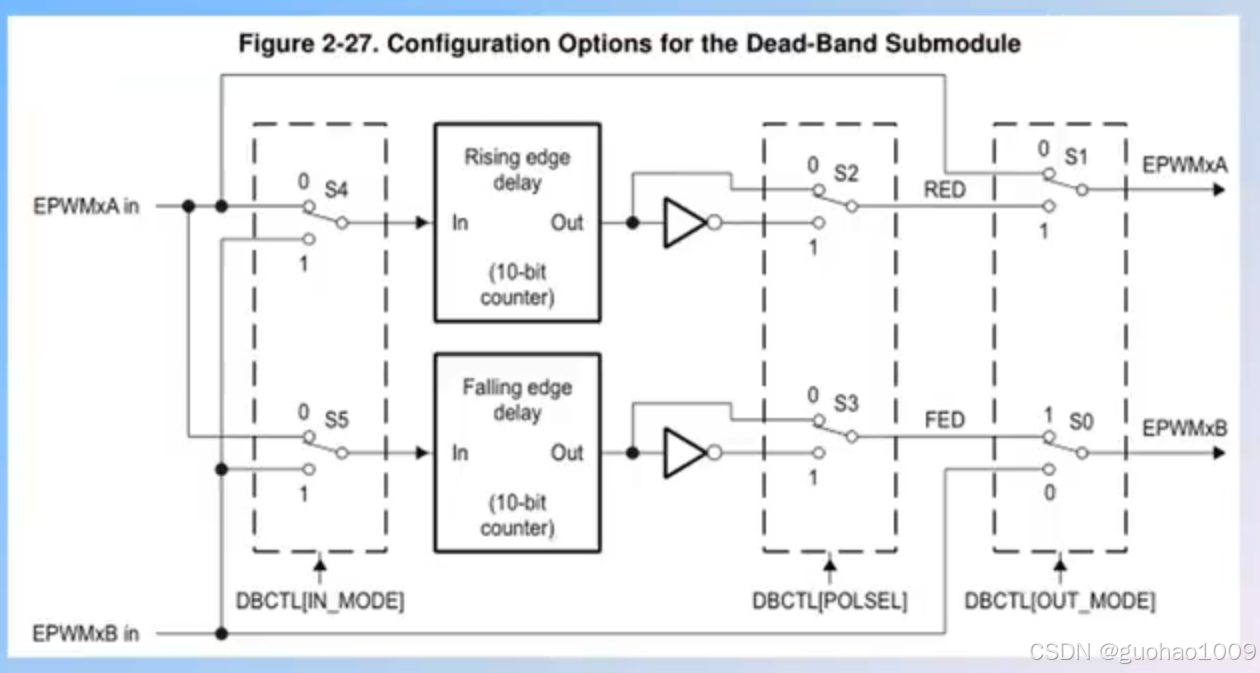

4、DB-死区子模块

DB子模块的作用在桥式电路中十分常见且重要,避免了单桥的直通,提高了后续电路的可靠性

实现死区的方式 就是延时开通:上升沿延时,下降沿延时;输出可以选择是否取反,也可以选择跳过DB环节

//死区控制 //ePWMa的上升沿和下降沿都加死区 EPwm1Regs.DBCTL.bit.IN_MODE = 0; //使能上升沿和下降沿的延时信号 EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //EPWMA反转极性 //EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_LOC; EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; //下降沿死区时间 max = 1023 EPwm1Regs.DBFED = deadtime; //上升沿死区时间 EPwm1Regs.DBRED = deadtime;5、PC-斩波子模块

6、TZ-故障子模块

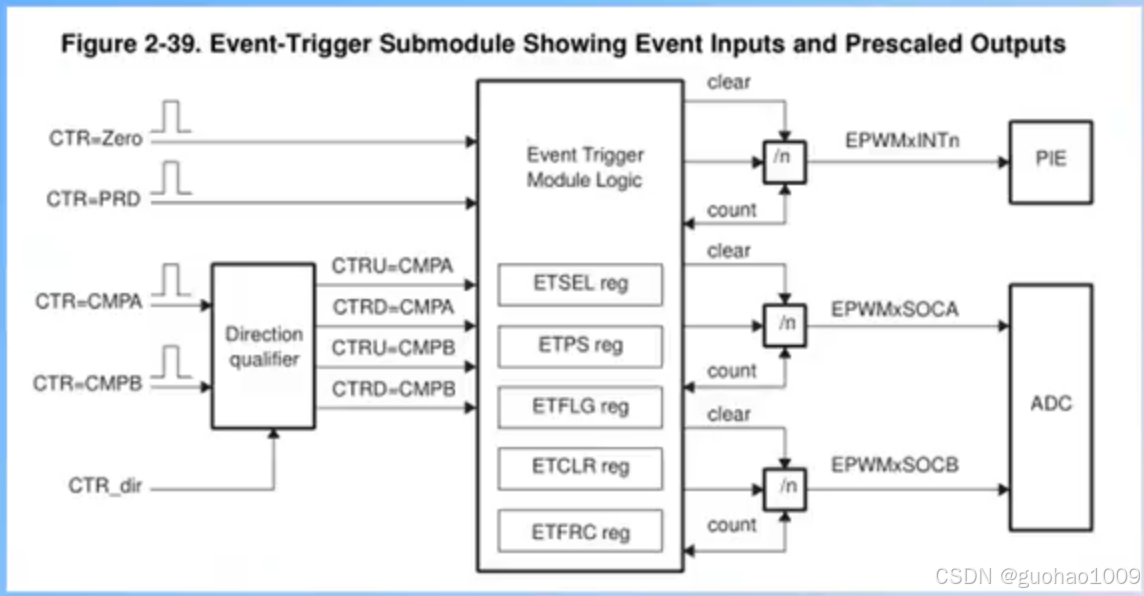

7、ET-事件触发子模块

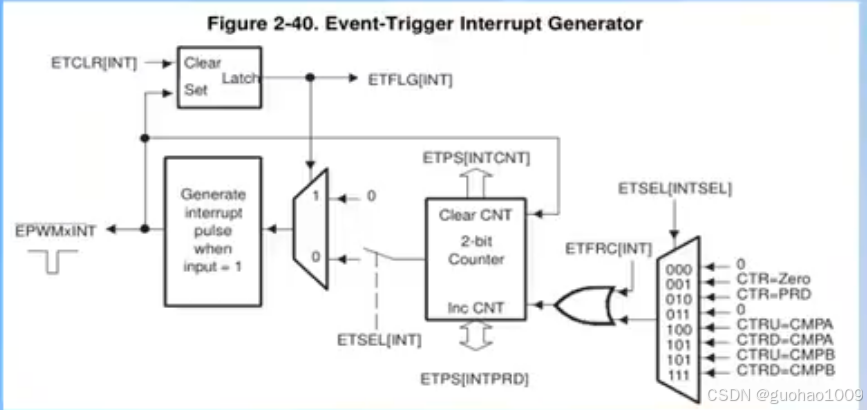

ET模块的作用是产生中断和触发ADC

一个特殊的地方在于ET可以对上述 输入事件进行计数,每n次输入事件 产生一次 输出事件 的触发。

ET事件触发的过程

//事件触发选择寄存器 EPwm1Regs.ETSEL.bit.INTSEL = 1; //使能 EPWM1_INT中断 EPwm1Regs.ETSEL.bit.INTEN = 1; //每次都产生事件 EPwm1Regs.ETPS.bit.INTPRD = ET_1ST; //清除中断标志位 EPwm1Regs.ETCLR.bit.INT = 1;后续将更新为EPWM周期计数触发ADC

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/131193.html