大家好,欢迎来到IT知识分享网。

SAR_ADC的电路原理

1 SAR ADC

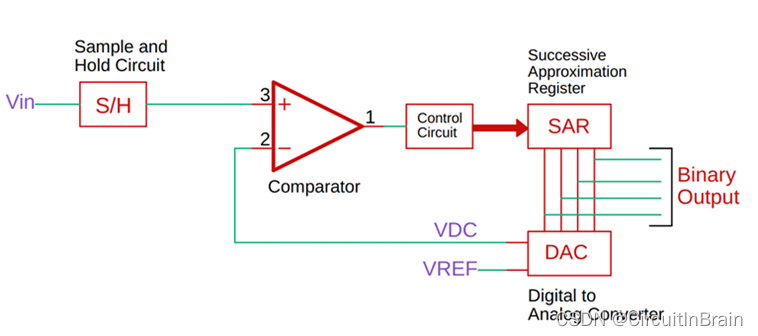

SAR(Successive Approximation ADC)是一种常用的ADC,SAR ADC的转换速度通常比闪存(Flash)ADC慢,但比积分型ADC快,由于其工作原理,SAR ADC的功耗通常介于闪存ADC和积分型ADC之间。SAR ADC通过逐个位地确定模拟信号的数字表示,从最高有效位(MSB)开始,然后向下进行。转换过程开始时,SAR ADC假设信号的最大可能值,然后通过比较器与实际信号进行比较,逐步调整其估计值,每次逼近步骤的结果都被存储在寄存器中,这些寄存器通常被称为SAR寄存器。SAR ADC可以设计成具有不同的分辨率,常见的有8位、10位、12位等,电路结构如下图所示,主要由采样保持电路,DAC,逻辑控制电路,逐次逼近寄存器组成。

图:SAR ADC原理图

2 工作过程

以输入信号5.2v为例

图:SAR ADC输入5.2v

Step1:

寄存器输出1000,VDC=0.625*8=5v,5.2v > 5v 比较器输出为1,数据寄存器D3=1

Step2:

寄存器输出1100,VDC=0.625*12=7.5v,5.2v<7.5v 比较器输出为0,数据寄存器D2=0

Step3:

寄存器输出1010,VDC=0.625*10=6.25v,5.2v<6.25v 比较器输出为0,数据寄存器D1=0

Step4:

寄存器输出1001,VDC=0.625*9=5.625v,5.2v<5.625v 比较器输出为0,数据寄存器D0=0

3 电路仿真

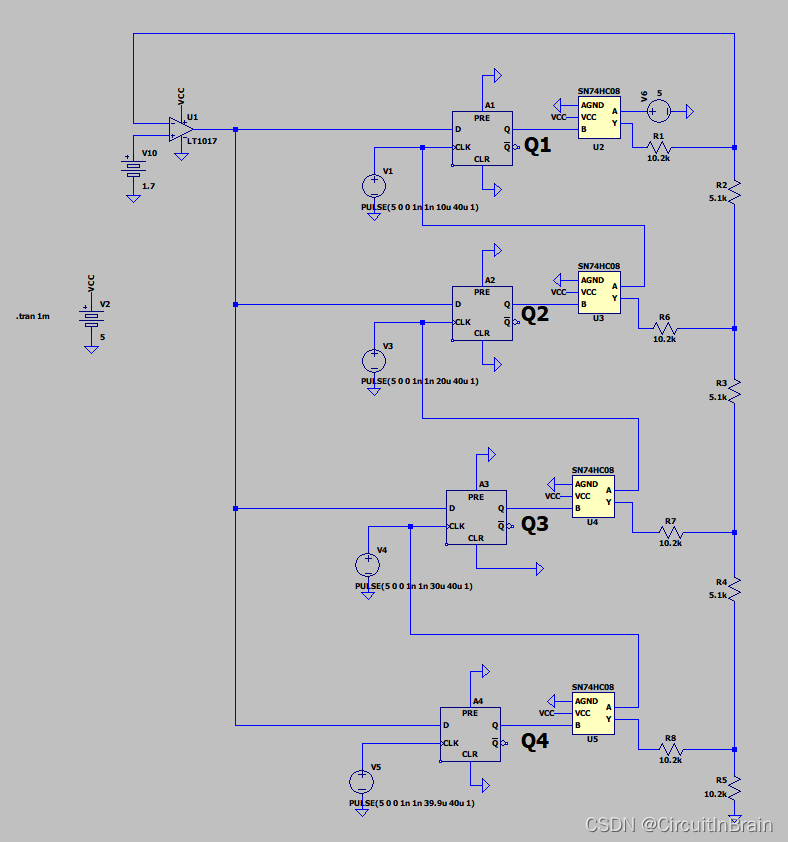

图:SAR ADC仿真原理图

当输入电压为1.7v时的工作过程:

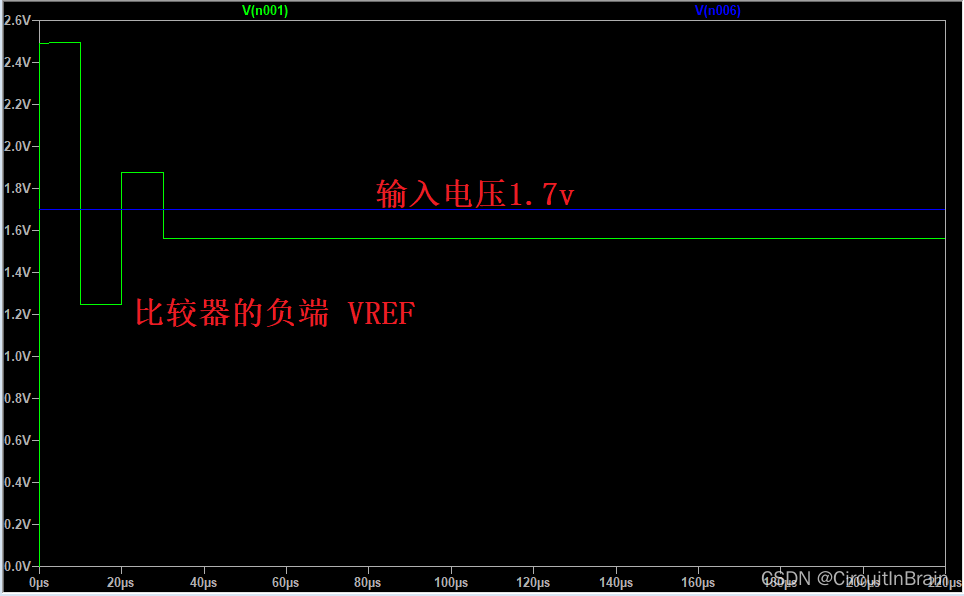

4 仿真输出波形

图:SAR ADC 的输出波形

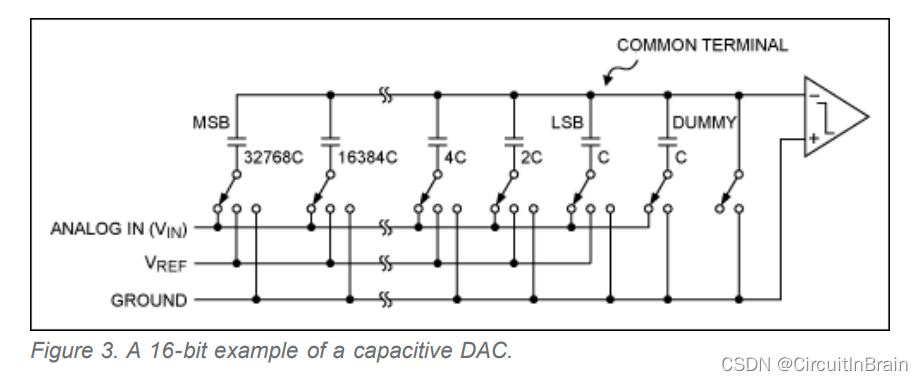

5 SAR ADC的电容式DAC原理

下图为一个16bit的电容式DAC,首先MSB先接到VREF上,此时公共端的电压就是-Vin + 1/2 *VREF,高于地输出1,低于地输出0,依次类推。

VCOMMON = -VIN + BN-1 × VREF/2 + BN-2 × VREF/4 + BN-1 × VREF/8 + … + B0 × VREF/2N-1 (B_为比较器输出/ADC输出位)。

图:电容式DAC原理

相关:

Σ-Δ_ADC的电路原理_∑-△型adc-CSDN博客

ADC学习总结_folding-flash adc-CSDN博客

Flash_ADC的电路原理_flash adc-CSDN博客

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/131345.html