大家好,欢迎来到IT知识分享网。

本文主要介绍了嵌入式系统的时钟是什么,由什么组成,如何通过时钟树看系统和外设的时钟频率,如何用仿真查看芯片的时钟频率(SYSCLK、HCLK、PCLK1、PCLK2等),再简单介绍一下外设定时器的时钟配置。

一、时钟的概念

1.引言

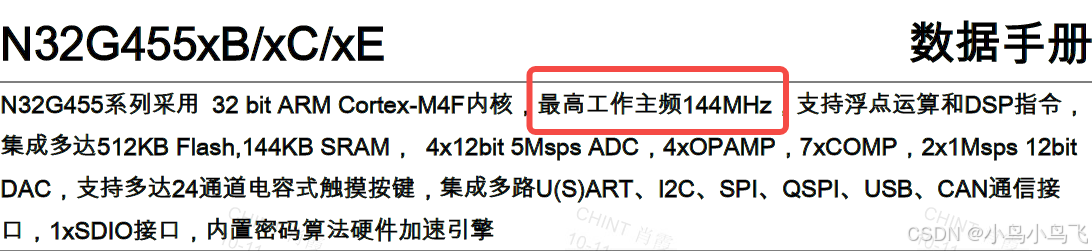

几乎每款芯片的数据手册的第一段话都如上图所示,其中提到的“最高工作主频144MHz”是什么意思呢?虽然不知道什么意思,但是能确定的是这个值肯定越大越好,其实它指的就是芯片内核在正常工作时能达到的最高时钟频率,它决定了芯片每秒能执行的指令数,主频越高,芯片的运算速度就越快。

时钟频率越高,芯片运算速度越快,这又是为什么呢?这就不得不提及嵌入式的时钟系统了。

2.时钟的概念

在网上搜索嵌入式的时钟,都会形容嵌入式的时钟就像人的心脏脉搏一样,极其重要。人没了心跳,会离开世间;芯片没了时钟,系统会崩溃瘫痪。总之,时钟可以让整个芯片正常工作。它的比较正式定义如下:

嵌入式芯片的时钟是指为系统提供时间基准的信号源,确保系统的各种操作和计算能够同步进行。时钟是嵌入式系统的脉搏,处理器内核在时钟驱动下完成指令执行,状态变换等动作,外设部件在时钟的驱动下完成各种工作,例如:串口数据的发送、AD转换、定时器计数等。因此时钟对于计算机系统是至关重要的,通常时钟系统出现问题也是致命的,比如振荡器不起振、振荡不稳、停振等。 时钟信号推动单片机内各个部分执行相应的指令。

二、时钟系统的组成

1.时钟系统组成

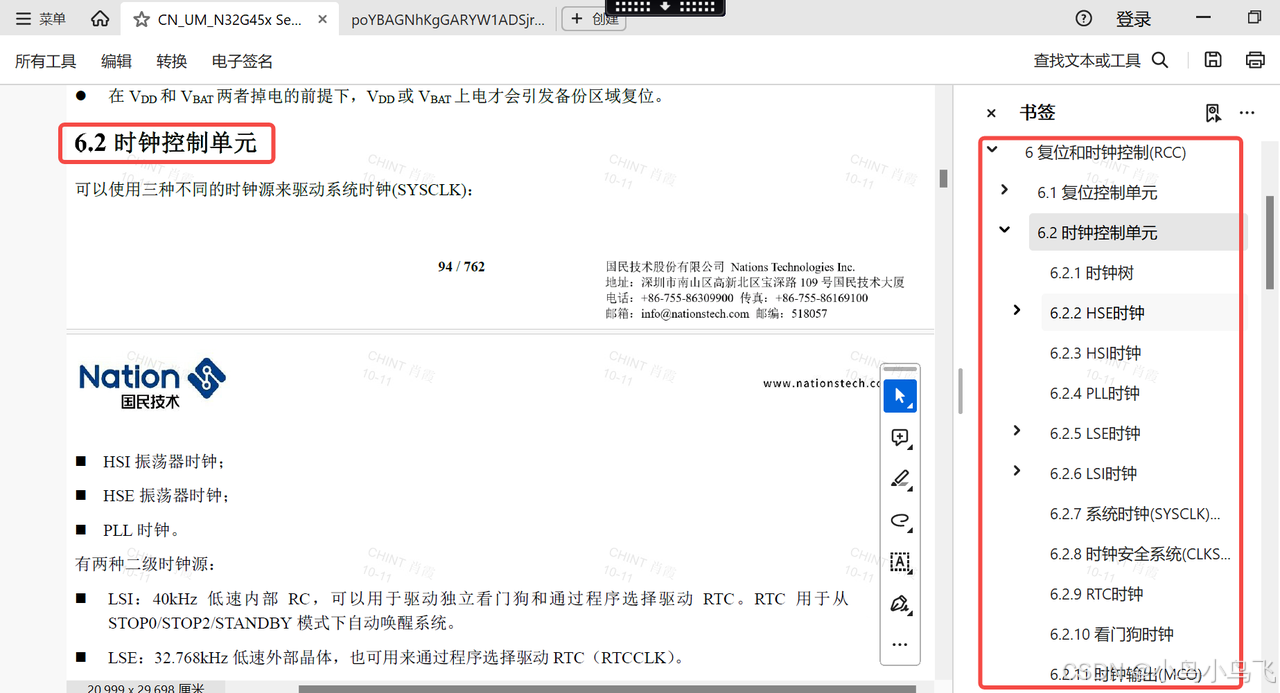

系统时钟主要是由时钟发生器(时钟源HSE、HSI、LSE、LSI)、分频器(AHB、APB)和倍频器(PLL)组成(当然还有其他部分,但是我觉得一般使用没必要了解那么深哈,可自行CSDN)。关于芯片这部分的具体配置可在用户手册的“复位和时钟控制(RCC)—>时钟控制单元”(类似目录)找到。

- 时钟源:系统中能够主动发出时钟信号的元器件,一般由振荡器或振荡电路组成。

HSE 外部高速时钟

时钟信号由外部晶振提供,时钟频率一般在4-16MHz,是经常会用到的时钟源;这里的外部晶振可以是有源晶振,也可以是无源晶振,它们的区别在于与STM32的连接方式,以及需不需要谐振电容。一般系统的主频就是在HSE外部高速时钟的基础上进行倍频得到的。

HSI 内部高速时钟

时钟信号由内部RC震荡电路提供,时钟频率为8MHz,但是这个时钟频率会随着温度产生漂移,很不稳定,所以一般不使用此时钟信号。一般来说,当HSE损坏的时候,会调用HSI,但是此时系统的时钟频率也很不稳定,近乎瘫痪。

LSE 外部低速时钟

时钟信号由外部晶振提供,时钟频率一般为32.768KHz,这个信号一般用于RTC实时时钟。

LSI 内部低速时钟

时钟信号由内部RC振荡电路提供,时钟频率一般为40KHz,这个信号一般用于独立看门狗时钟。

- 分频器:分频器用于将输入时钟信号分频为较低频率的时钟信号,分频器有很多哈,以下只列举较常见的AHB和APB。

AHB:高速总线(一般最大可以达到SYSCLK[144MHz])。

APB:低速总线,一般分为APB1(一般最大36MHz,低速)和APB2(一般最大72MHz,高速)。

Tips:这里有个小坑,见时钟树,APB1最大36MHz,但是挂载在APB1上的TIM时钟怎么是72MHz呢?

- 倍频器:用于将输入的时钟信号倍频为更高频率的时钟信号。

倍频器又叫锁相环PLL,PLL是一种反馈环路系统,用于将输入的时钟信号倍频为更高频率的时钟信号。

比如HSE=8MHz,PLL=18,则系统主频SYSCLK=8MHzX18=144MHz。系统主频会有最大值限制,所以在HSE频率固定的情况下,PLL不会无限大。

2.时钟树

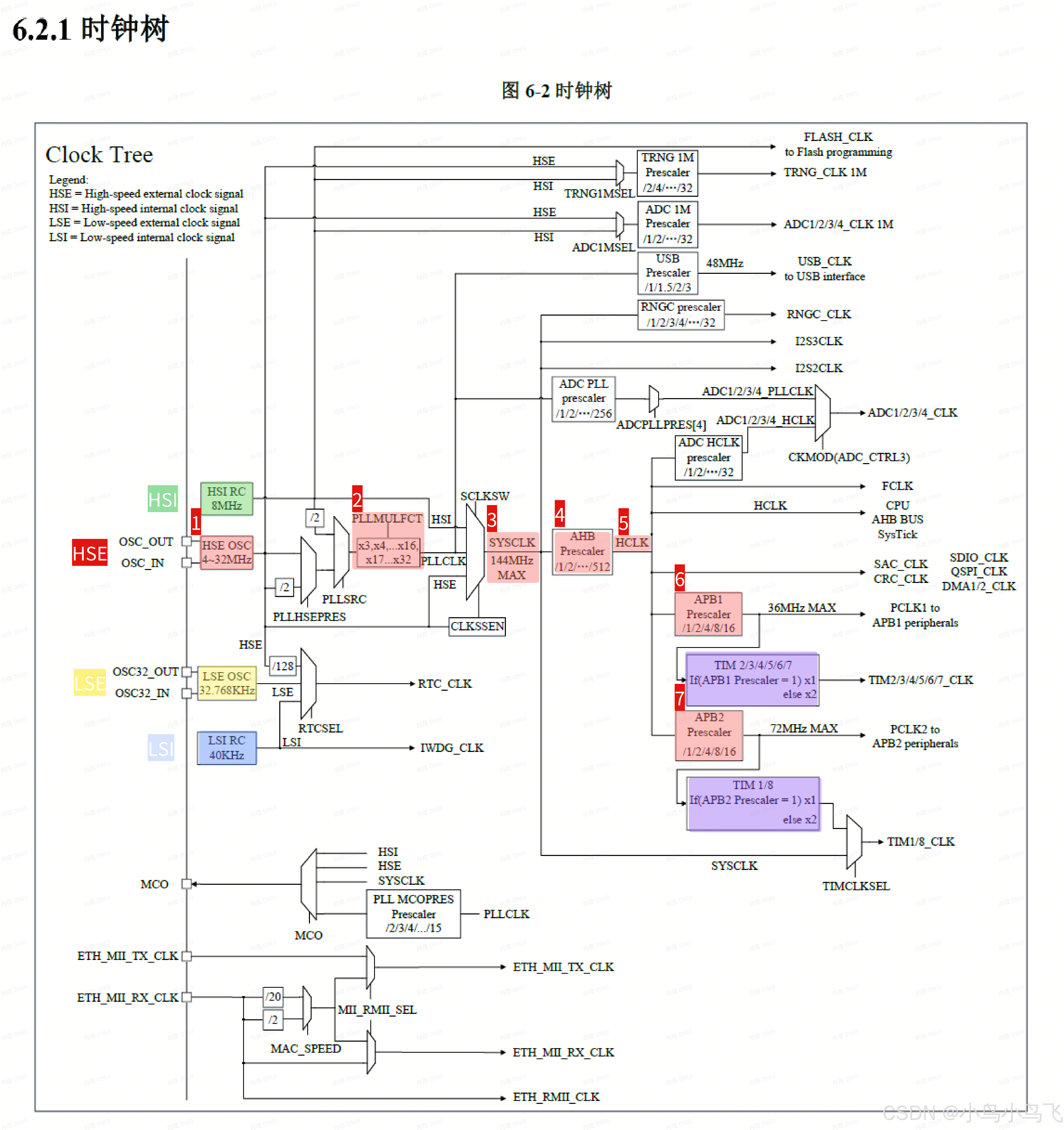

要想了解时钟系统的各个部分是如何工作的还得看看时钟树。时钟树展示了时钟信号源的时钟信号传递的过程,也展示了该如何去配置我们的主频(SYSCLK),HCLK(AHB),PCLK1(APB1),PCLK2(APB2)等。接下来简单解释一下时钟树的信号流转,详细的还是查阅用户手册。

如图所示,绿色HSI,蓝色LSI它们都是芯片的内部时钟,所以是嵌在系统里的,红色HSE,黄色LSE它们都是外部时钟,需要外接晶振,所以它们在由系统外的晶振提供。由于系统的运行一般都是靠HSE,所以重点讲一下HSE的时钟信号路径。

- HSE:外接晶振提供外部高速时钟,一般频率范围为4-32MHz,常用的为8MHz。

- PLLMULFCT(PLL):倍频器,将外部高速时钟经过倍频得到PLLCLK。

- SYSCLK:系统时钟,也就是主频,由图上可知,SYSCLK的来源是可选的,一是HSI(一般不用,当HSE崩掉的时候可能会用);一是PLLCLK,也就是经过倍频后的HSE(用得最多,毕竟谁不希望自己的芯片运算速度越快越好呢);一是HSE,也就是我们外接的晶振频率(一般也不用)。

- AHB:高速总线,也是分频器,由图上可知,它由系统主频(SYSCLK)提供,经过Prescaler(分频),可以得到HCLK。

- HCLK:由AHB分频得来,一般就等于/1,也就是等于系统主频。

- APB1:低速总线,最大36MHz,由HCLK提供,也是经过Prescaler(分频),可以得到PCLK1。

- APB2:低速总线,最大72MHz,由HCLK提供,也是经过Prescaler(分频),可以得到PCLK2。

注意看紫色部分,一般来说,外设挂载在相应的总线上,时钟频率不会超过总线频率,外设一般是通过分频得到需要的频率,但是N32G455系列的TIM定时器不同,如下图所示,当APB预分频为1,则相同,不为1,则为2倍,也就是倍频了,所以APB1最大为36MHz,但是挂载在APB1上的TIM时钟却是72MHz,所以看时钟树图很重要!!!!

-

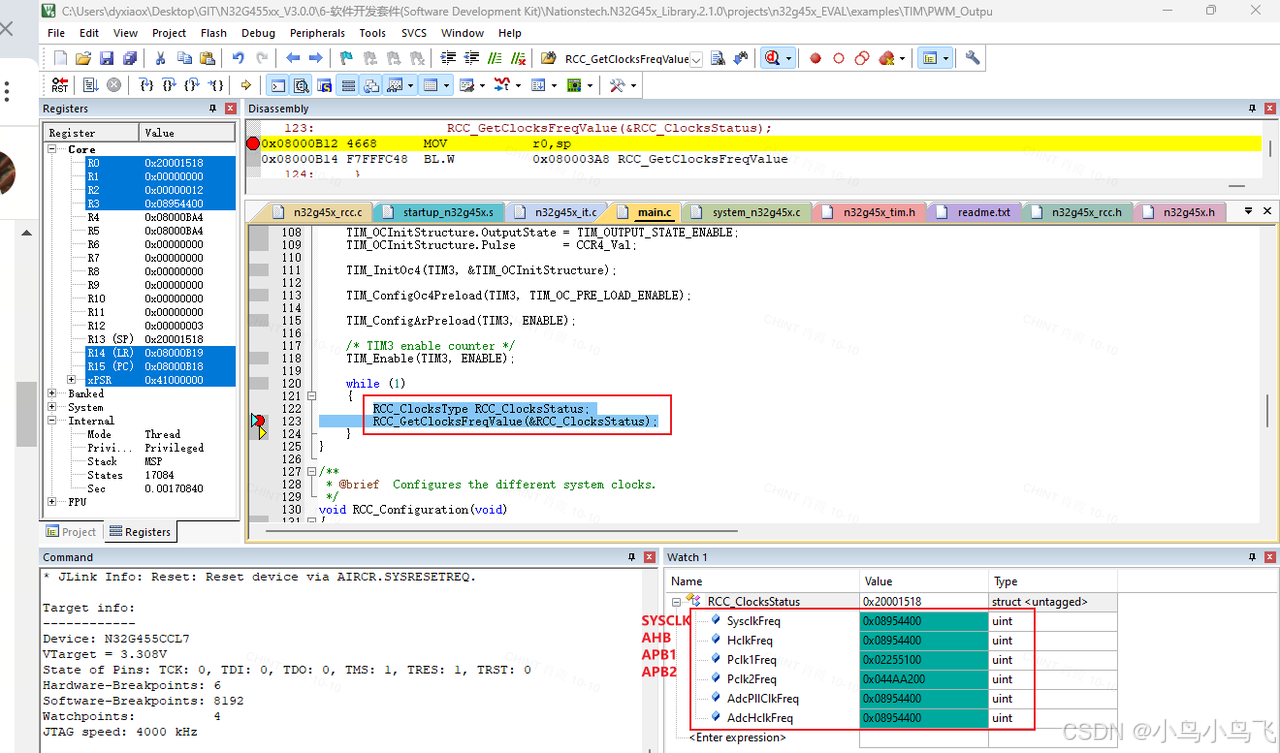

仿真查看各时钟的配置频率

如果要查看芯片配置后的时钟频率,可以keil仿真查看各时钟的配置频率。

RCC_ClocksType RCC_ClocksStatus; RCC_GetClocksFreqValue(&RCC_ClocksStatus);三、定时器的时钟配置

为什么要介绍定时器的时钟配置呢?这其实也是我学时钟的原因,在使用N32G455的时候,发现APB1的频率最大为36MHz,但是通过示波器抓取波形,发现挂载在它上面的TIM3输出的PWM波的时钟源频率为72MHz,感到疑惑找原因,最后发现是硬件预分频导致TIM3的时钟在APB1的基础上倍频了。

所以简单介绍一下要输出PWM波时,定时器的时钟配置,只讲时钟配置,其他基础知识自行CSDN哦,好,开始正文:

因为我要调试PWM,所以我用到定时器3(TIM3),通过查看用户手册可以知道它是通用定时器。

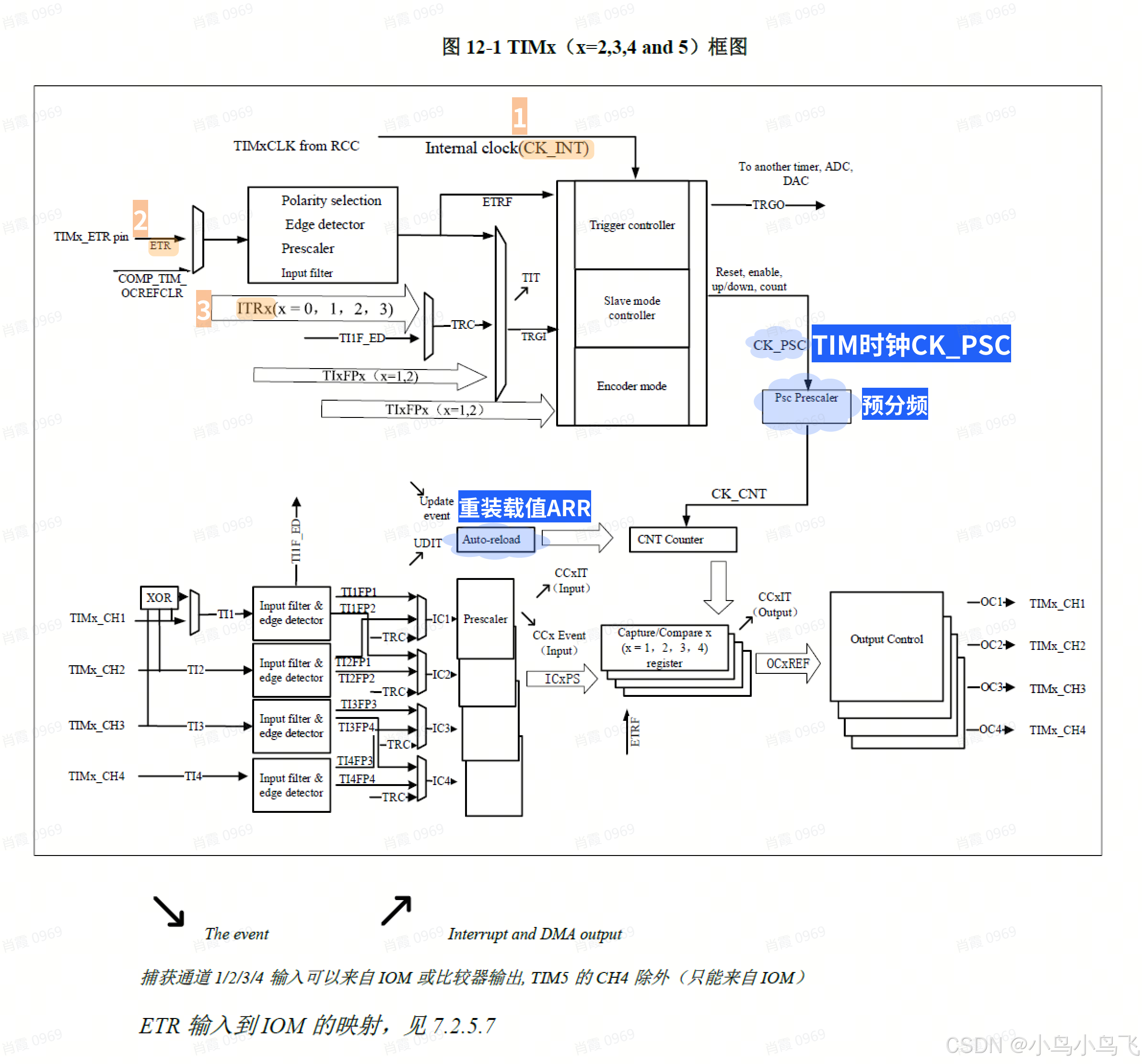

TIM框图

前景提要:

一般可以在如下图所示的路径找到TIM框图。

PWM波频率计算公式。

CK_PSC:计数单元时钟源频率

PSC:分频因子

那么:

Freq=CK_PSC/(PSC+1)/(ARR+1)

PWM波的时钟频率为计数单元的时钟频率,即TIM3的时钟频率,也就来源于上图所示CK_PSC,CK_PSC的来源有三种,分别是如图所示1通用定时器的内部时钟CK_INT,2两种外部模式,3内部触发输入。

因为我要输出PWM波,所以要选择内部时钟CK_INT,这与芯片引脚的复用功能有关。具体可参考这篇文章:

https://www.cnblogs.com/qianxiaohan/p/

以上内容仅为个人学习分享,若有错误,敬请指正。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/134178.html