大家好,欢迎来到IT知识分享网。

目录

概述

本文主要介绍ARM最新内核Cortex-M85的相关技术,重点介绍了Armv8.1-M内核和最新的Helium技术。笔者研读了ARM官方网站上关于Cortex-M85的相关技术的内容,以及Helium技术的内容,将这些内容总结成本篇文字。

1 认识Cortex-M85

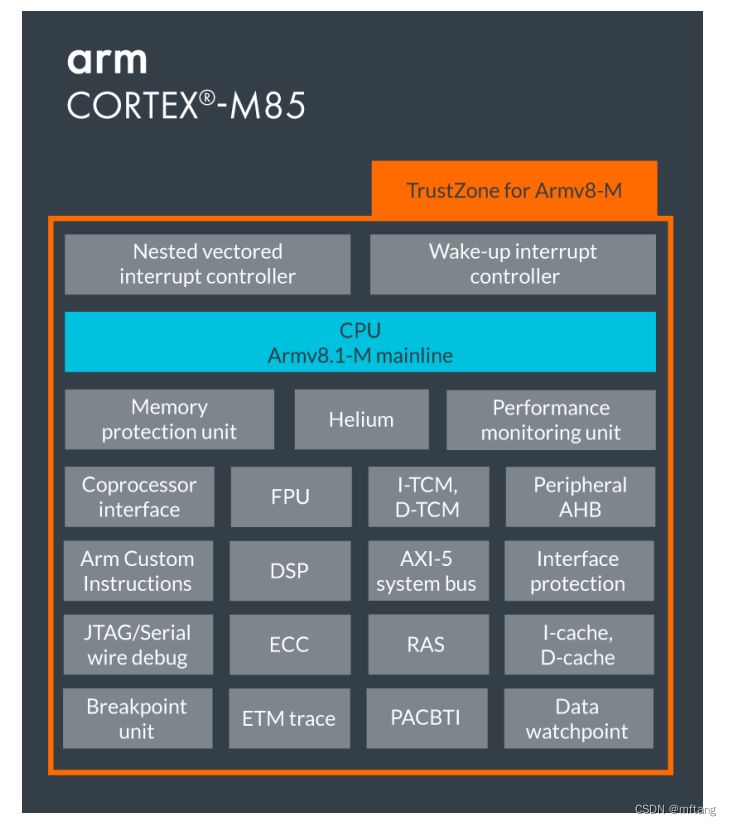

Arm Cortex-M85是采用Arm Helium技术的性能最高的Cortex-M处理器,为需要更高性能和更高安全性的基于Cortex-M的应用提供了自然升级路径。除了Arm TrustZone技术外,Cortex-M85还带来了新的安全和安全功能,为Cortex-M提供了迄今为止最高级别的保护。这使其成为连接和安全关键应用的理想选择。

2 Cortex-M85的特点

1)最高标量,DSP和ML性能

Cortex-M85集成了Arm Helium技术,提供Cortex-M系列处理器的最高标量、DSP和ML性能。

2)简化软件开发

Cortex-M85无需使用复杂的多核或异构平台,简化了软件架构、开发、测试和调试。

3)更快的安全认证路径

PACBTI提供了增强的软件攻击威胁缓解,简化了实现PSA认证2级的过程,这正在成为物联网部署的基准。

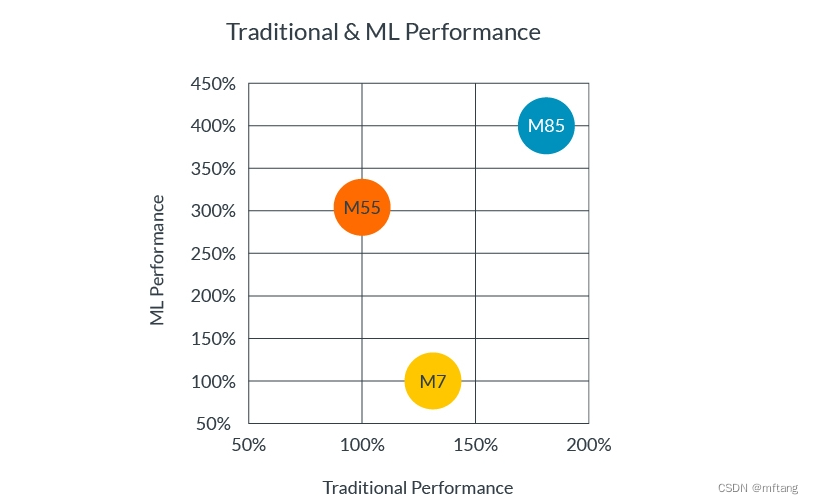

Cortex-M85是性能最高的Cortex-M处理器,全面提供前所未有的性能水平。它是第一个提供超过6 cocomments /MHz和超过3 DMIPS/MHz的Cortex-M。这种级别的标量性能的实现要归功于微架构级别的许多创新功能,包括优化的双问题和选择性三重问题能力,改进的分支预测以及包括数据预取在内的增强内存系统等。

通过集成Arm Helium技术,与之前的Cortex-M7相比,Cortex-M85提供了多倍(x4)的DSP和ML处理提升。与其他支持氦的处理器Cortex-M55相比,它还带来了大约20%的矢量处理性能提升。再一次,微架构创新将Cortex-M85提升到了前所未有的性能水平。

3 技术参数

Arm Cortex-M85处理器通过集成的安全功能实现了新的本地处理水平。Cortex-M85基于Armv8.1-M架构,提供了Cortex-M系列中最高的标量和信号处理性能。Cortex-M85使合作伙伴能够为需要增强数字信号处理(DSP)和机器学习(ML)功能的物联网和嵌入式应用构建最复杂的各种mcu和嵌入式soc。

用例包括智能家居设备、机器人和无人机控制、安全系统控制器和传感器集线器。合作伙伴将能够通过单个Cortex-M处理器降低高性能系统的成本和系统复杂性。

| 类型 | 说明 |

|---|---|

| Architecture | Armv8.1-M |

| Bus interfaces |

1)AMBA 5 AXI 64-bit Main system bus (compatible to AXI4 IPs) 2)AMBA 5 AHB 32-bit Peripheral bus 3)AMBA 5 AHB 64-bit TCM Access bus (subordinate port) |

| Pipeline | 7-stage (for main integer pipeline) |

| Security | Arm TrustZone technology, with optional Security Attribution Unit (SAU) of up to 8 regions. Stack limit checking. PACBTI extension (Pointer Authentication, Branch Target Identification) |

| Memory Protection | Optional Memory Protection Units (MPU) for process isolation with up to 16 MPU regions and a background region – if TrustZone is implemented, there can be a Secure and a Non-secure MPUs. |

| DSP extension | 32-bit DSP/SIMD extension |

| Vector extension |

Optional Helium technology (M-profile Vector Extension) supporting up to: 2 x 32-bit MACs/cycle 4 x 16-bit MACs/cycle 8 x 8-bit MACs/cycle |

| Floating-point Unit (FPU) | Optional FPU with support for half precision (fp16), single precision (fp32) and double precision (fp64) floating-point operations. |

| Accelerator support | Optional coprocessor interface (64-bit) supporting up to 8 coprocessor units for custom compute accelerators. Optional Arm Custom Instructions. |

| Instruction cache | Up to 64kB with ECC (optional) |

| Data cache | Up to 64kB with ECC (optional) |

| Instruction TCM (ITCM) | Up to 16MB with ECC (optional) |

| Data TCM (DTCM) | Up to 16MB with ECC (optional) |

| Interrupts | Integrated Nested Vectored Interrupt Controller (NVIC) supporting up to 480 interrupts, and Non-maskable interrupt (NMI). Number of priority levels configurable from 8 to 256. |

| Wake-up Interrupt Controller (WIC) | Internal and/or external (optional) WIC for waking up the processor from state retention power gating or when all clocks are stopped |

| Low power support |

1)Architecturally defined Sleep and Deep Sleep modes. 2)Integrated wait for event (WFE) and wait for interrupt (WFI) instructions with Sleep On Exit functionality 3)Sleep and Deep Sleep indication signals 4)Multiple power domains with optional retention support for memories and logic |

| Debug |

1)Hardware and software breakpoints 2)Performance Monitoring Unit (PMU) |

| Trace | Optional Instruction trace with Embedded Trace Macrocell (ETM), Data Trace (DWT) (selective data trace), and Instrumentation Trace (ITM) (software trace) |

| Robustness |

1)ECC on instruction cache, data cache, instruction TCM, data TCM (optional) 2)Dual core lock step (optional) 3)Bus interface protection (optional) 4)PMC-100 (Programmable MBIST Controller, optional) Reliability, availability and serviceability (RAS) extension |

4 Armv8.1-M

4.1 认识Armv8.1-M

Armv8.1-M将Armv8-M架构提升到新的性能水平,而不会 影响软件开发的便利性和Arm第三方生态系统的丰富性。新架构包括 M-Profile Vector Extension (MVE),可大幅提升机器学习(ML)和数字信号处理(DSP)性能。它实现了M-profile处理器的简化 程序员模型 , 为数百万开发人员带来了先进的计算能力。在Arm Cortex-M处理器中,MVE被命名为 Arm Helium技术。该架构还通过Arm TrustZone增强了系统范围的安全性。

4.2 Armv8.1-M体系结构的主要特性

Armv8.1-M架构包括以下特性:

1)一个有效的矢量处理能力,加速信号处理和ML算法称为MVE。

2)向量扩展中支持的其他数据类型:半精度浮点数(FP16)和8位整数(INT8)。

3)低架空回路。

4)集合负载,分散存储内存访问。

5)额外的调试功能,包括性能监控单元,为DSP软件开发量身定制,以及调试扩展,以支持调试中的多个安全域。

4.3 Armv8.1-M架构的扩展

Armv8.1-M有几个可选的新体系结构扩展。其主要有如下这些:

1)指针身份验证和分支目标标识(PACBTI)扩展,通过为软件开发人员提供的新工具增强了安全性。

2)Helium – M-Profile Vector Extension (MVE)用于当前基于Armv8.1-M的处理器和未来的Arm Cortex-M处理器。

3)低架空分支扩展。

4)内存保护单元(MPU)的特权执行永远(PXN)扩展。

5)可靠性、可用性和可服务性(RAS)扩展。

6)调试特性的附加扩展。

5 Arm Helium技术

5.1 传统DSP/Contex-M的问题

创建一个具有良好DSP性能的处理器的一半工作是为它提供足够的数据。在Cortex‑A处理器上,128位Neon负载可以很容易地直接从数据缓存中提取。但是,Cortex‑M处理器通常没有缓存,而是使用低延迟SRAM作为主存储器。由于将通往SRAM(通常只有32位)的路径扩展到128位对于许多系统来说是不可接受的,因此我们面临着内存操作停滞长达四个周期的可能性。类似地,乘法和累加(MAC)指令中使用的乘数器占用了大量面积,在小型Cortex‑M处理器上使用4个32位乘数器是行不通的。从面积限制的角度来看,最小的Cortex- m处理器和功能强大的失序Cortex- a处理器在尺寸上可能有数量级的差异。因此,当创建M – profile架构时,我们真的必须考虑到每一个最后的门。为了最大限度地利用可用的硬件,我们需要让昂贵的资源(比如通往内存的路径和乘数器)在每个周期内同时处于繁忙状态。在像Cortex – M7这样的高性能处理器上,这可以通过双重发布矢量加载和矢量MAC来实现。但是一个重要的目标是在一系列不同的性能点上提高DSP的性能,而不仅仅是在高端。采用一些已有几十年历史的矢量链技术有助于解决这些问题。

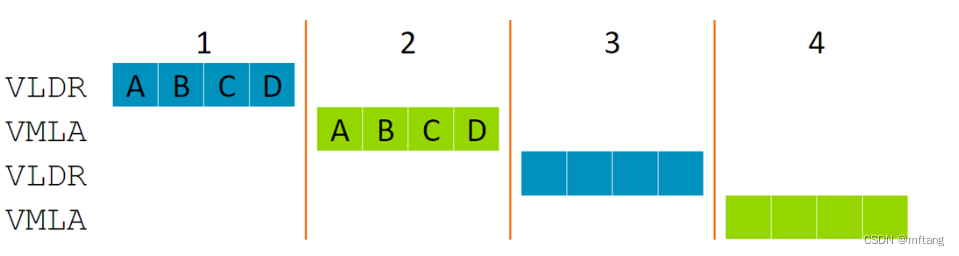

下图显示了在四个时钟周期内执行矢量负载(VLDR)和矢量MAC (VMLA)指令的交替序列。这将需要一条128位宽的内存路径,以及四个MAC块,这两个块在一半的时间里都是空闲的。你可以看到每个128位宽的指令被分成四个大小相等的块,MVE架构称之为“节拍”(标记为A到D)。这些节拍总是32位的计算值,无论元素大小如何,所以一个节拍可以包含1个32位MAC,或4个8位MAC。由于加载和MAC硬件是分开的,所以

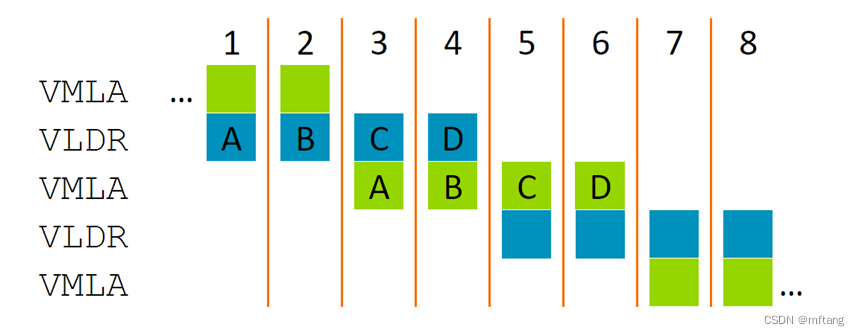

即使VLDR加载的值被后续的VMLA使用,指令仍然可以重叠。这是因为VMLA的节拍A只依赖于VLDR的节拍A,它发生在前一个周期,所以节拍A和B与节拍C和D重叠不需要时间旅行。在本例中,我们获得了与128位数据路径处理器相同的性能,但硬件只有前者的一半。“比优”执行的概念支持高效地实现多个性能点。例如,下图显示了只有32位数据路径的处理器如何处理相同的指令。这是非常吸引人的,因为它使单发出标量处理器的性能翻倍(在8个周期内以8 x 32位值加载和执行mac),但没有双发出标量指令的面积和功耗损失。

5.2 Arm Helium解决并行处理问题的方法

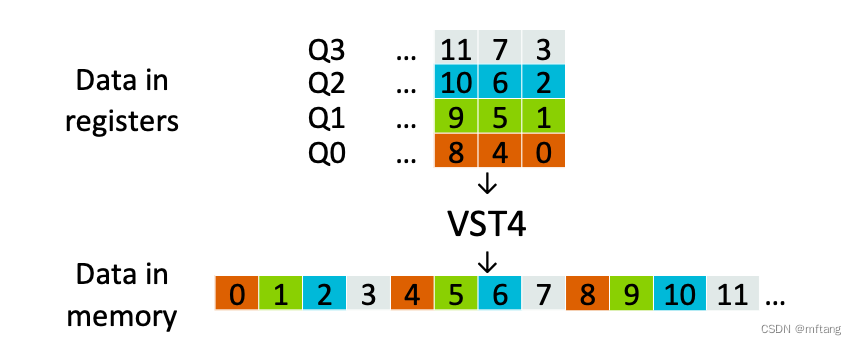

DSP处理的一个重要部分是有效地处理不同的数据格式,这些格式往往需要转换成不同的格式进行计算。这方面的一个很好的例子是图像数据,它通常存储为红色、绿色、蓝色和alpha像素值的交错流。然而,为了向量化计算,你可能需要一个向量中的所有红色像素,另一个向量中的所有绿色像素等等。在Neon架构中,VLD4 / VST4指令可以执行这种转换,如下所示。

VST4交错使用4个128位寄存器,总共存储512位数据。Neon架构有多种交错/反交错操作来支持不同的格式。例如,提供了一个VST2,可以用来交错立体声音频的左右通道。这些指令还支持从8位到32位的不同元素大小。

MVE的“优于”执行的主要好处之一是,它允许内存和ALU操作重叠,即使在单问题处理器上也是如此。如下所示,要实现这种技术所支持的性能加倍,所有指令必须执行相同数量的工作。

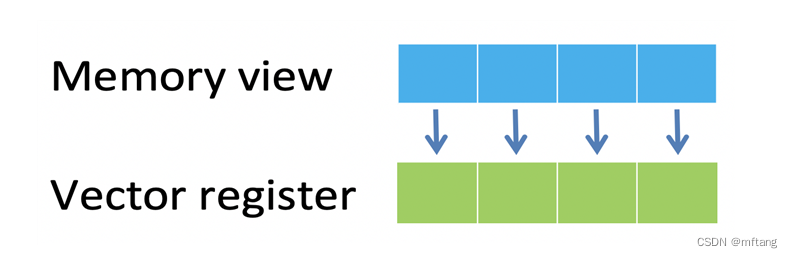

Helium是一个四拍矢量架构。将数据加载到向量中最直接的方法是连续加载操作(见图1)。对于每个节拍,从标量寄存器中指定的基址开始依次访问内存。不管目标数据类型是8位、16位还是32位,这都可以通过充分利用总线宽度的访问来有效地执行,因为数据元素在内存和向量中都是相邻的。对于存储操作也是如此。

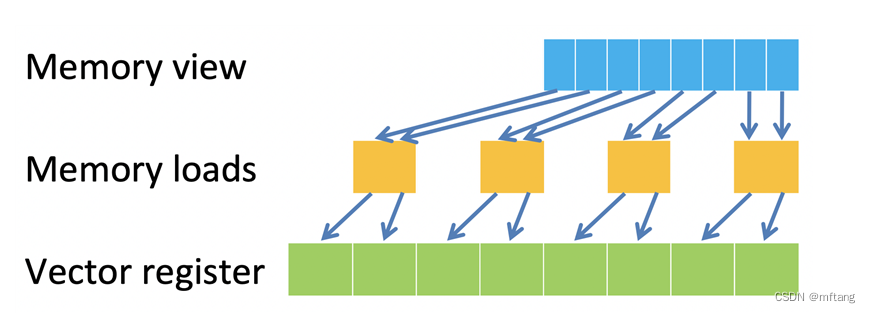

由于内存是一种稀缺资源,因此通常尽可能紧密地打包数据,使用能够容纳它的最小数据类型。然而,在处理数据时,可能需要更多的余量,以避免在计算的中间阶段出现溢出。这可以作为一个独立的扩展指令来执行,但正如本系列的第一篇文章所解释的那样,这需要时间旅行。(对于8位到32位的扩展,将数据扩展到最后一个拍需要来自第一个拍的数据,而第一个拍不再可用。)因此,扩展指令不能与任何其他指令重叠,这将对性能产生不利影响。相反,Helium引入了大小变化的内存操作。在这里,数据可以高效地加载为每个节拍的单个8位、16位或32位访问,并且可以零扩展或符号扩展以匹配所需的数据类型。在下面的示例中(参见图2),我们希望对每个矢量通道执行8位加载扩展到16位。两个8位数据样本作为单个16位加载操作加载,每个8位数据样本在写入矢量通道之前被扩展到16位。类似地,对于存储,可以将数据截断到所需的大小并有效地存储。

Helium的加载和存储指令与M – Profile架构的其他部分具有相同的丰富寻址模式集,具有前置或后递增和指针回写支持等功能。这在大多数情况下消除了单独的指针操作操作的需要。

DSP应用程序通常对数据结构而不是单个元素进行操作。例如,立体声音频数据通常存储为左值和右值的交错流。类似地,图像数据通常存储为交错的红-绿-蓝-阿尔法值。这是上一篇文章的主题,其中描述了结构化的加载/存储指令,可以有效地做到这一点。

有时,存储在内存中的数据不能以方便的方式进行结构化,从而使连续访问成为可能。在某些体系结构中,这实际上可以防止代码被向量化。Helium通过分散-聚集操作解决了这个问题。它们指向一个偏移量向量到内存中,这样就可以用一条指令访问多个不连续的地址。它们还可以扩展或截断正在访问的数据。

6 参看文献

https://community.arm.com/arm-research/b/articles/posts/making-helium-going-around-in-circles免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/139430.html