大家好,欢迎来到IT知识分享网。

一.同步时钟与异步时钟

1.同步时钟

当两个时钟的相位关系是固定关系,则可以称这两个时钟为同步时钟(synchronous clock),经过一个PLL产生相位不同,但是相位固定的两个时钟,他们依旧是同步时钟。

2.异步时钟

而如果是两个晶振产生的时钟,因为两个晶振在上电时相位差是随机的,而且不同晶振时钟漂移抖动也不一样,所以相位是不固定的。当无法判断两个时钟间的相位时,则可以称这两个时钟为异步时钟(asynchronous clocks)。

二.同步/异步电路

1.同步电路

同步时序逻辑特点:各触发器时钟端全部连接在一起,并接在系统的时钟端,只有当时钟脉冲到来时,电路的状态才改变,改变后的状态会一直保持到下一个时钟脉冲的到来。

a) 电路核心逻辑是用各种触发器实现;

b) 电路主要信号、输出信号等都是在某个时钟沿驱动触发器产生的;

c) 同步时序电路可以很好的避免毛刺;

d) 利于器件移植;

e) 利于静态时序分析(STA)、验证设计时序性能。

2.异步电路

异步时序逻辑特点: 电路没有统一的时钟,电路中除了可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件。电路状态的改变是由外部输入的变化直接引起的。

a) 电路核心逻辑是用组合电路实现;

b) 异步时序电路的最大缺点是容易产生毛刺;

c) 不利于器件移植;

d) 不利于静态时序分析(STA)、验证设计时序性能。

三. 同步复位和异步复位

1.同步复位

同步复位只有在时钟沿到来时复位信号才起作用,则复位信号持续的时间应该超过一个时钟周期才能保持系统复位。

1.1. 同步复位代码:

//同步复位 module top ( input clk, input rst_n, input a, output reg b ); always@(posedge clk) begin if(!rst_n) b <= 1'b0; else b <= a; end endmodule 1.2. 同步复位特点

同步复位优点: 一般能够保证电路百分百同步。确保复位只发生在有效沿,可以作为过滤掉毛刺的手段。

同步复位的缺点: 复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位。同时还要考虑如:时钟偏斜、组合逻辑路径延时、复位延时等因素。(由于大多数的厂商目标库内的触发器都只有异步复位端口,采用同步复位的话,就会耗费较多的逻辑资源。)

同步复位虽然解决了当时钟的有效沿来临的时候 rst_n 的边沿也正好来临所出现的冒险与竞争。 但是从综合的电路上可以看出,多了一个组合逻辑 MUX。

2. 异步复位

只要有复位信号系统马上复位,因此异步复位抗干扰能力差,有些噪声也能使系统复位,因此有时候闲的不够稳定,要想设计一个好的复位最好使用异步复位同步释放。(后续进行细化【参考】)

2.1. 异步复位代码:

module top ( input clk, input rst_n, input a, output reg b ); always@(posedge clk or negedge rst_n) begin if(!rst_n) b <= 1'b0; else b <= a; end endmodule 2.2. 异步复位的特点

异步复位优点:异步复位信号识别方便,而且可以很方便的使用全局复位。由于大多数的厂商目标库内的触发器都有异步复位端口(CLR)(在这个端口一般接低电平有效的复位信号rst_n,即使设计中是高电平复位,实际综合后也会把异步复位信号反向后接到CLR端)可以节约逻辑资源。

异步复位缺点:

a、最大的问题在于它属于异步逻辑,问题出现在复位释放时,而不是有效时,如果复位释放接近时钟有效沿,则触发器的输出可能进入亚稳态(此时 clk 检测到的 rst_n 的状态就会是一个亚稳态,即是0是1是不确定的),从而导致复位失败。

b、可能因为噪声或者毛刺造成虚假复位信号(比如以前的游戏机玩到一半突然复位)(注意:时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题)。

c、静态定时分析比较困难。

d、对于 DFT (Design For Test可测性设计)设计,如果复位信号不是直接来自于 I/O 引脚,在 DFT 扫描和测试时,复位信号必须被禁止,因此需要额外的同步电路。

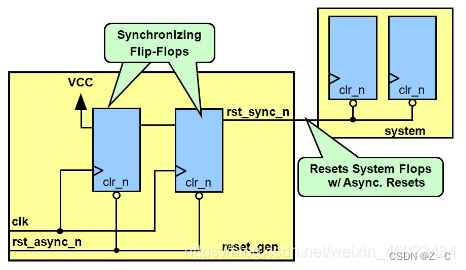

3. 异步复位同步释放

使用异步复位同步释放就可以很好的平衡上述复位方式的优缺点。所谓异步复位,同步释放就是在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步,为了消除亚稳态的产生,利用两个同一时钟沿触发的层叠寄存器,将异步信号同步化。

3.1.代码实现

//异步复位、同步释放 module top ( input clk, input rst_n, input a, output reg b ); reg rst_n_r; reg rst_n_rr; always@(posedge clk or negedge rst_n) begin if(!rst_n) {rst_n_rr,rst_n_r} <= 2'b00; else {rst_n_rr,rst_n_r} <= {rst_n_r,rst_n}; end always@(posedge clk or negedge rst_n_rr) begin if(!rst_n_rr) b <= 1'b0; else b <= a; end endmodule 3.2.电路视图

那它在电路上怎么体现的呢,在笔试中可能会让画出来,一定要掌握

这里推荐一个帖子:

同步复位和异步复位二者各自的优缺点

关于同步与异步的内容先记录到这里,后续进行补充

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/153381.html