大家好,欢迎来到IT知识分享网。

1 PLL IP核简介

注意: PLL的时钟输入可以来自于时钟专用输入引脚,FPGA内部产生的信号不能驱动PLL。

2 实际工程

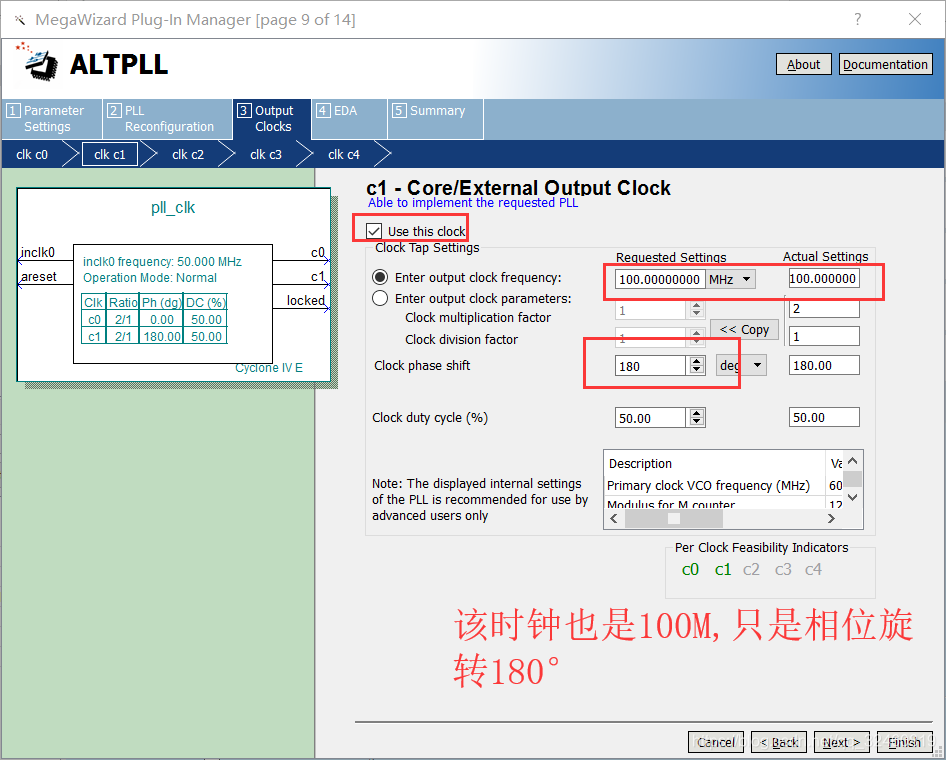

配置第2个时钟

module ip_pll( input sys_clk, input sys_rst_n, output clk_100m, output clk_100m_180deg, output clk_50m, output clk_25m ); wire locked; wire rst_n; assign rst_n = sys_rst_n & locked; pll_clk u_pll_clk ( .areset (!sys_rst_n), .inclk0 (sys_clk), .c0 (clk_100m), .c1 (clk_100m_180deg), .c2 (clk_50m), .c3 (clk_25m), .locked (locked) ); 进行自动仿真设置,

仿真文件配置

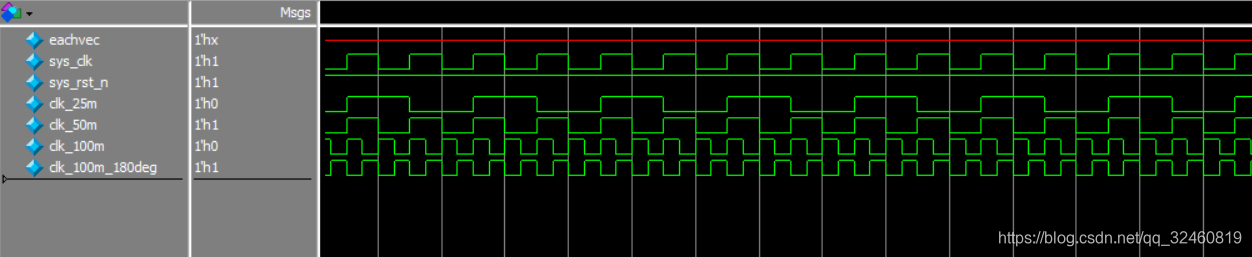

`timescale 1 ns/ 1 ns module ip_pll_vlg_tst(); // constants // general purpose registers reg eachvec; // test vector input registers reg sys_clk; reg sys_rst_n; // wires wire clk_25m; wire clk_50m; wire clk_100m; wire clk_100m_180deg; // assign statements (if any) ip_pll i1 ( // port map - connection between master ports and signals/registers .clk_25m(clk_25m), .clk_50m(clk_50m), .clk_100m(clk_100m), .clk_100m_180deg(clk_100m_180deg), .sys_clk(sys_clk), .sys_rst_n(sys_rst_n) ); initial begin sys_clk = 1'b0; sys_rst_n = 1'b0; #20 sys_rst_n = 1'b1; //延时100ns 复位信号拉高 #2000 $stop; end always #10 sys_clk = ~sys_clk; //延时10ns反转 endmodule 最终仿真图

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/112157.html