大家好,欢迎来到IT知识分享网。

一、PCIe 5.0概述

(1)什么是PCIe 5.0

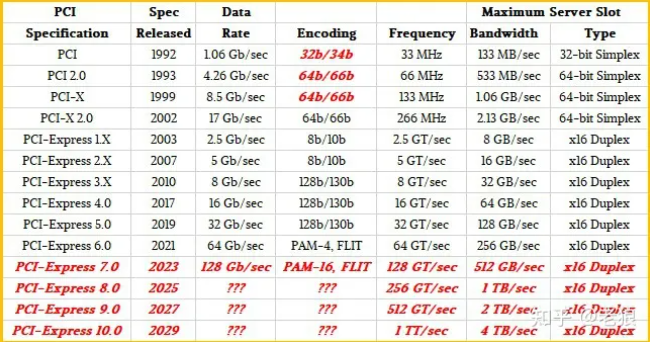

第五代快速周边组件互连称为PCI Express 5.0(Peripheral Component Interconnect Express 5.0),也称为第五代PCIe、PCIe 5、PCI v5或简称为PCIe 5.0。PCIe技术于2003年首次推出,现已成为使用点对点访问总线将高速组件连接到主板的标准接口。

PCIe 5.0速度是 PCIe 4.0的两倍,并具有向下兼容性。PCIe 5.0协议分析仪能够支持 32GT/秒的数据链路速度操作,同时具有卓越的内存、存储容量和分段功能,可捕获更大容量的上行和下行流量。

(2)PCIe 5.0高带宽的挑战

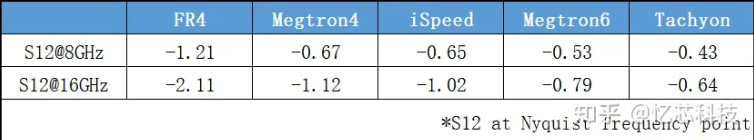

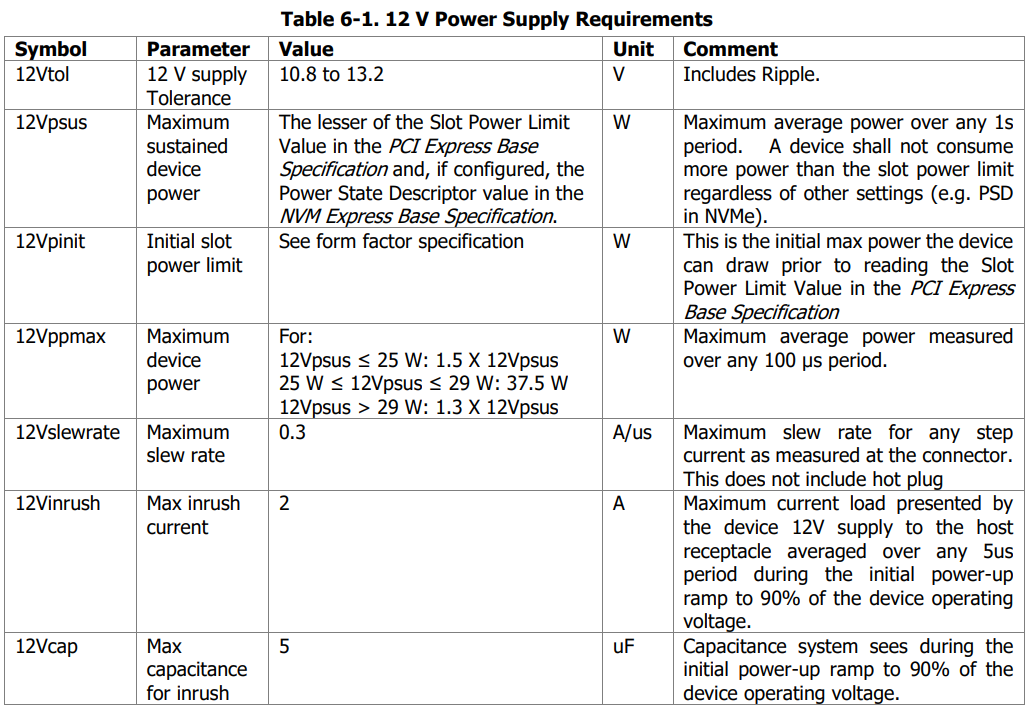

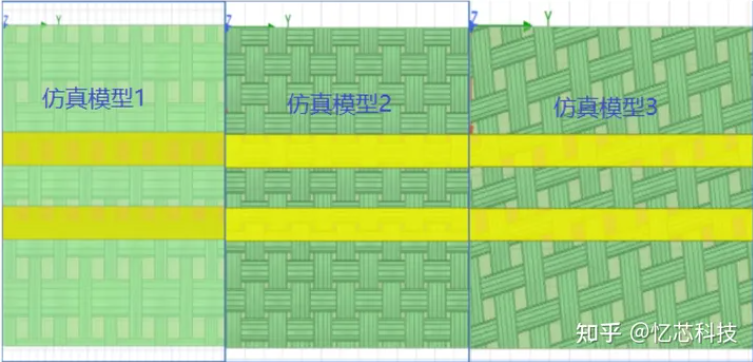

速率到达32Gb/s后走线的趋肤效应、耦合效应、表面粗糙度效应等越来越明显,使得互联链路的损耗、串扰问题愈加严重,除此之外PCB材料的选择会对插入损耗产生极大的影响。表1通过仿真模拟了在16 GT/s(8 GHz 奈奎斯特)和 32 GT/s(16 GHz 奈奎斯特)数据速率下PCB上1inch走线长度插入损耗的情况:

表 1 奈奎斯特频点处不同PCB材料的S12

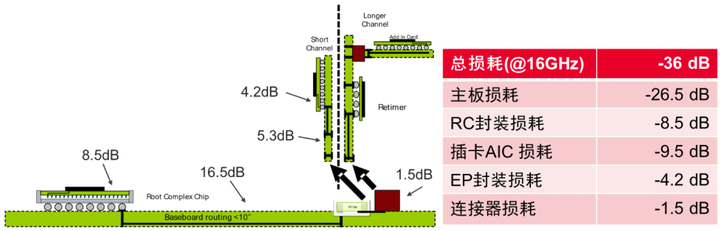

在PCIe协议规范中,规定了链路的总损耗,其中PCIe 4.0和PCIe 5.0的总损耗要求如表2所示。协议限制了PCIe 4.0/5.0 AIC在奈奎斯特频点的总损耗分布是-8dB和-9.5dB(包括从金手指边缘经过PCB,过孔,隔直电容,芯片封装等),综合表1可见在PCIe 5.0系统中需要使用比FR4更好的板材来降低信号走线的损耗,因为电路板走线的损耗只是总信道损耗的一小部分<5.3dB

表 2 PCIe 4.0和PCIe 5.0链路损耗总体规划和分配

PCIe 5.0链路损耗示意图

PCI Express 5.0 的信道要求也要求为发射器(发射)和接收器(接收)设计新的均衡电路,并且电压和定时的接收通道裕度已成为强制要求。

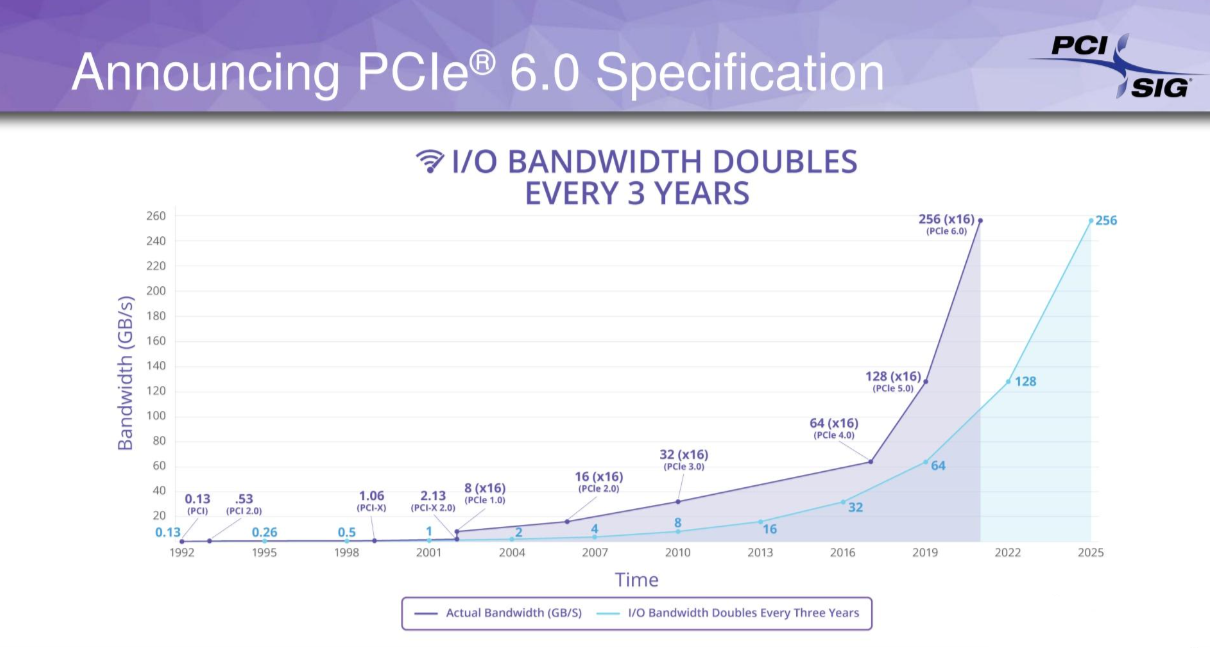

(3)PCIe 5.0的未来

2022年发布PCIe 6.0的最终规范版本,这一新的迭代将继续传统的带宽加倍和向后兼容,这意味着 PCIe 标准这一次达到了令人震惊的256GB/秒的双向带宽。这将有效地将 PCIe 与低端 GPU 的 vRAM 带宽相媲美。PCIe 6.0硬件概述将在后续相关文章更新……

二、PCIe引脚介绍

(1)引脚概述

①总体功能

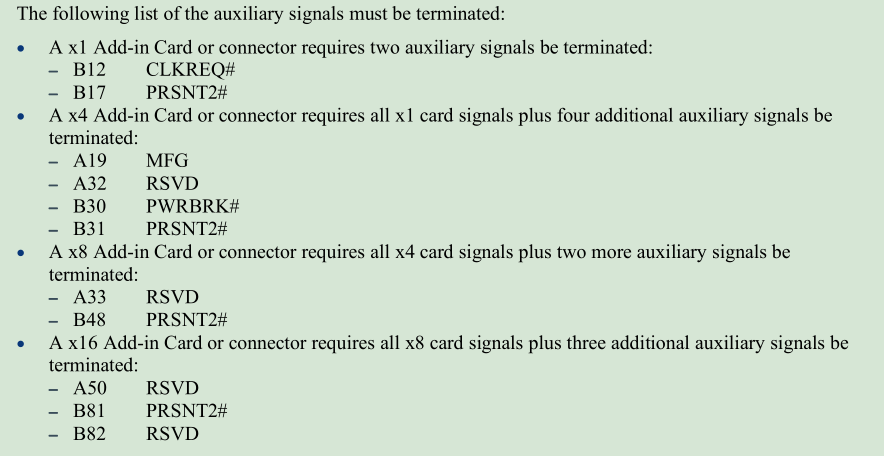

注意在下表格中:

a. AIC是Add-in-Card的缩写,PCIe 5.0 CEM规范已明确定义其具体电气和结构参数。

b. EDSFF是Enterprise and Datacenter Standard Form Factor的缩写,主要应用场景为企业和数据中心,其规格和标准AIC不同。

| 引脚名称 | 引脚作用 |

|---|---|

| SMBCLK | SMBUS(AIC Optional/EDSFF Required) |

| SMBDAT | SMBUS(AIC Optional/EDSFF Required) |

| SMBRST | SMBUS(AIC Optional/EDSFF Required) |

| CLKREQ# | 参考时钟请求信号(AIC Optional/EDSFF Optional) |

| PRSNT# | 插入检测(AIC Required/EDSFF Required) |

| PER | PCIe Rx差分信号(AIC Required/EDSFF Required) |

| PET | PCIe Tx差分信号(AIC Required/EDSFF Required) |

| RFU | 不悬空,增加AC端接电路 |

| 12V | 12V电源(AIC Required/EDSFF Required) |

| 3.3V | 3.3V电源(AIC Required/EDSFF Required) |

| 3.3 VAUX | 3.3V辅助电源(AIC Required/EDSFF Required) |

| MFG | 卡厂商自定义信号(AIC Optional/EDSFF Optional) |

| PERST0# | 复位信号(AIC Required/EDSFF Required) |

| PERST1# | dual port才使用的复位信号(AIC Required/EDSFF Required) |

| REFCLK#0 | 参考时钟(AIC Required/EDSFF Required) |

| REFCLK#1 | dual port才使用的参考时钟(AIC Required/EDSFF Required) |

| DUALPORTEN# | 主机输出给卡,是否支持dual-port mode(EDSFF Required) |

| PWRDIS | 主机输出给卡,允许主机对卡断电(EDSFF Required) |

②AIC DC Spec

③AIC AC Timing

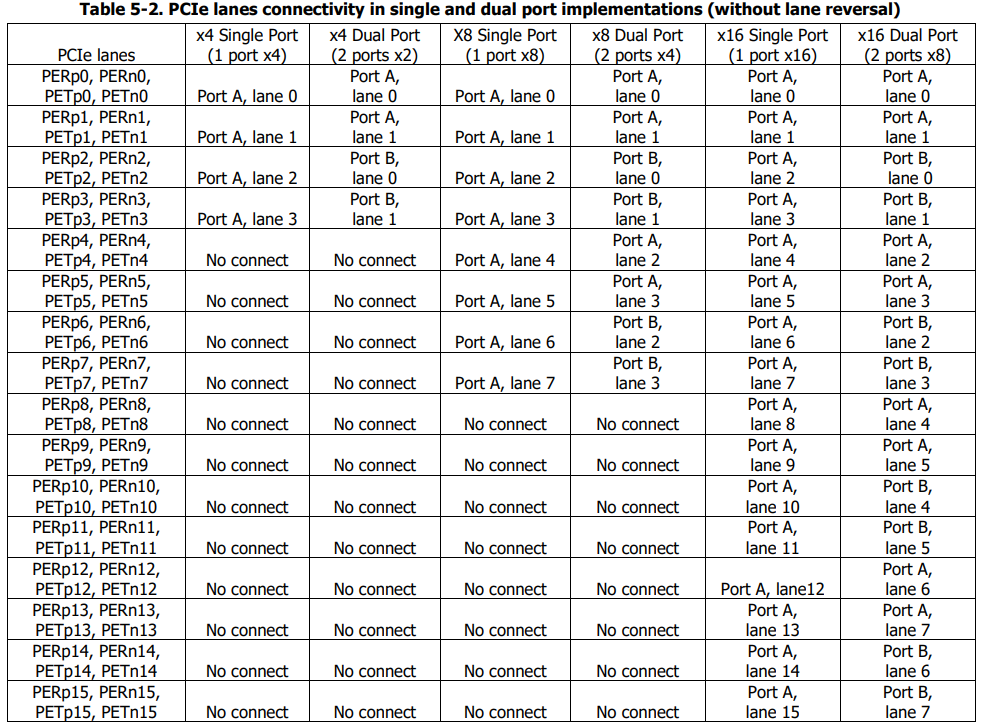

④EDSFF Single和Dual Port差异:

(2)PRSNT#(AIC Required/EDSFF Required)

前提:某些特殊的应用场合可能要求PCIe设备能够以高可靠性持续不间断运行。为此,PCIe总线采用热插拔(Hot Plug)和热切换(Hot Swap)技术,来实现不关闭系统电源的情况下更换PCIe卡设备。

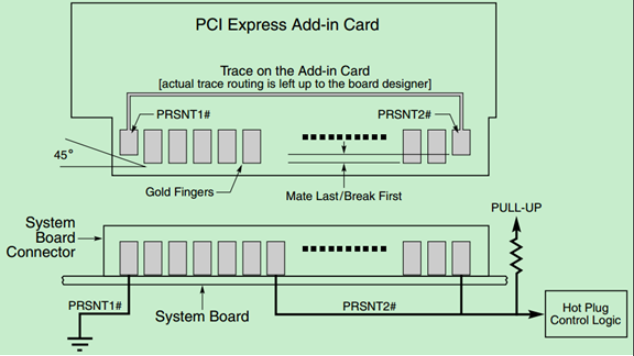

PCIe总线的热插拔主要指的是PCIe卡设备的热插拔,以及相关的实现机制等。PCIe卡有两个用于热插拔机制的引脚——PRSNT1#和PRSNT2#。PCIe卡设备上的这两个信号之间是短路的,PCIe插槽的PRSNT1#被固定地连接到地,PRSNT2#则被上拉。且PCIe卡上的这两个信号的金手指长度要比其他的信号的金手指长度要短一点。如下图所示,当PCIe卡设备未被完全插入插槽时,插槽的PRSNT2#信号由于上拉的作用,将一直处于高点平状态。当PCIe卡设备被完全插入插槽后,插槽上的PRSNT2#信号则会被PCIe卡设备的短路线连接到地,从而使得其变为低电平。换句话说,从插槽的角度看,当PRSNT2#位高电平时,则认为PCIe卡设备未能正确插入或者无PCIe卡设备;当PRSNT2#位低电平时,表明PCIe卡设备被正确地插入插槽中

当PCIe需要支持热插拔时,PRSNT1#、PRSNT2#引脚必须按照规范连接,如果不支持热插拔,则必须将PRSNT2#接地,如果悬空会导致背板插槽PRSNT2#无法被拉低,导致板卡无法正常工作。

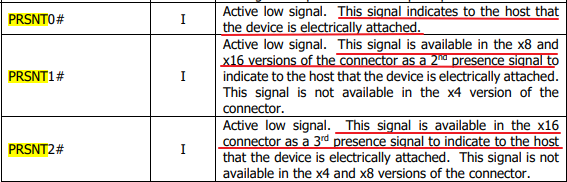

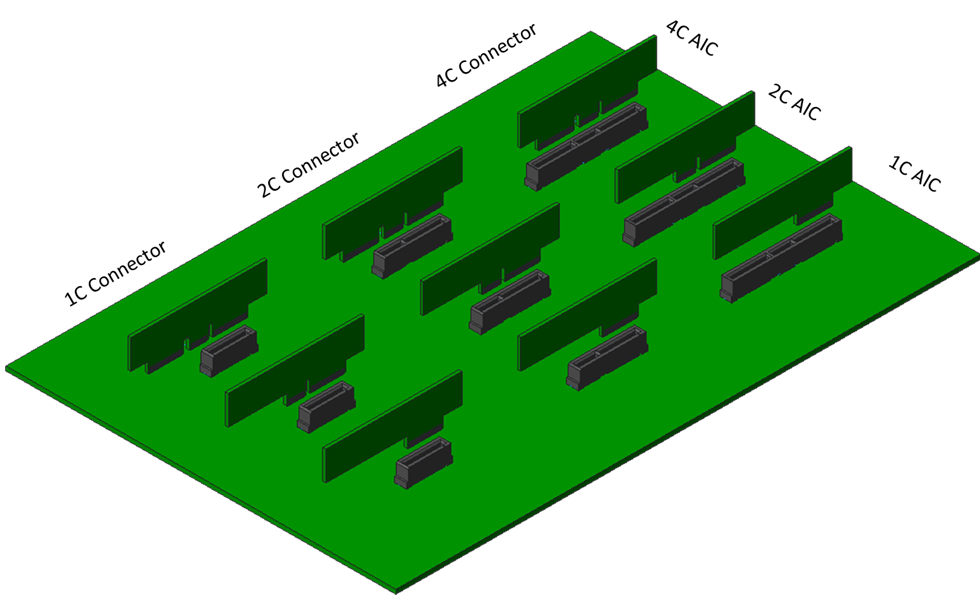

在EDSFF 4C槽位中,PRSNT分为0#,1#,2#,分别对应1C,2C,4C槽位的插入检测:

(3)REFCLK#(AIC Required/EDSFF Required)

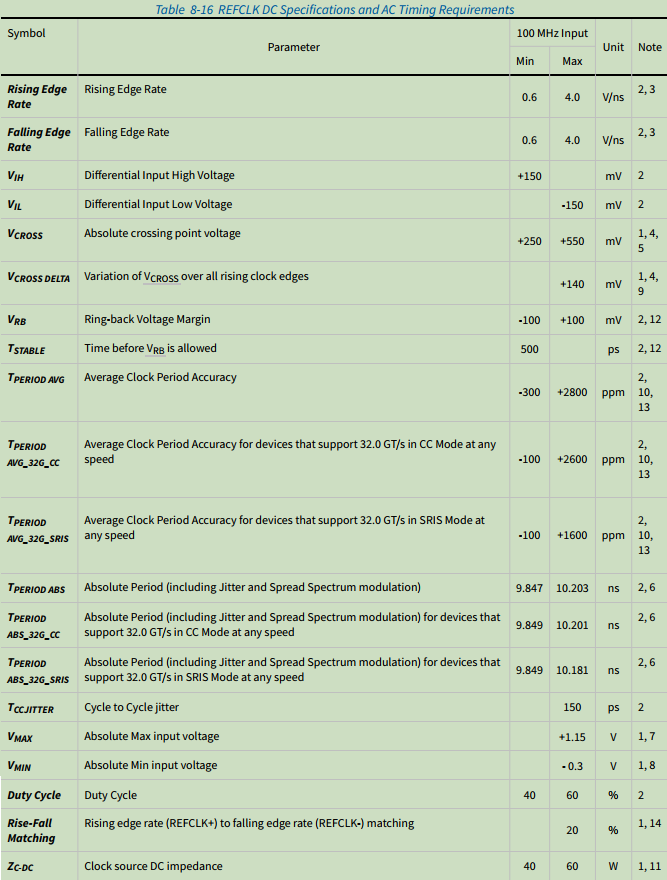

REFCLK#是一种类LVDS信号(Low Voltage Swing,Differential Clocks),其时钟频率为100MHz,精度为±300ppm。对于支持扩频时钟(Spread Spectrum Clocking,一种降低系统EMI的手段)的系统,正向综合精度为300ppm+2500ppm=2800ppm。即-300ppm~2800ppm。

REFCLK的详细DC Spec和AC Timing要求如下表所示:

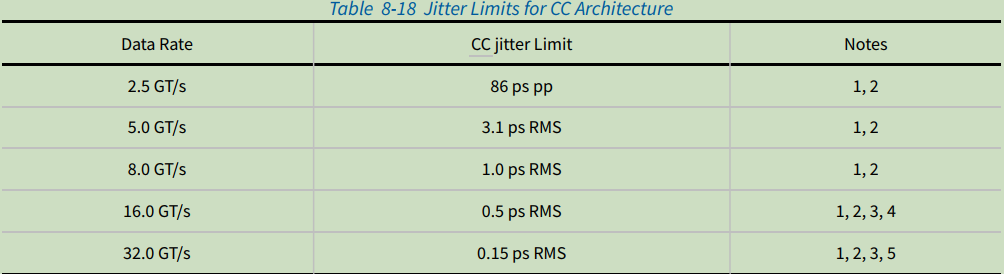

下图为REFCLK#最大允许的RMS Rj相位抖动值(捕获至少100,000个时钟间隔——1.0 ms)

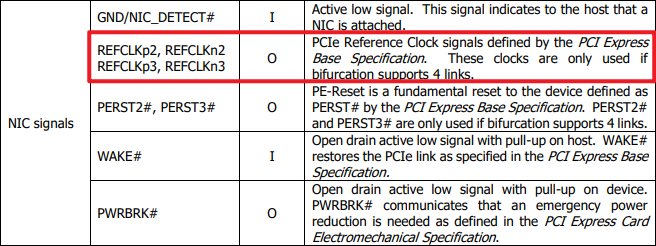

EDSFF 4 links有REFCLKp2和REFCLKp3

如果主机不提供参考时钟,建议用电阻下拉参考时钟信号。

(4)WAKE#(AIC Optional/OBFF Required)

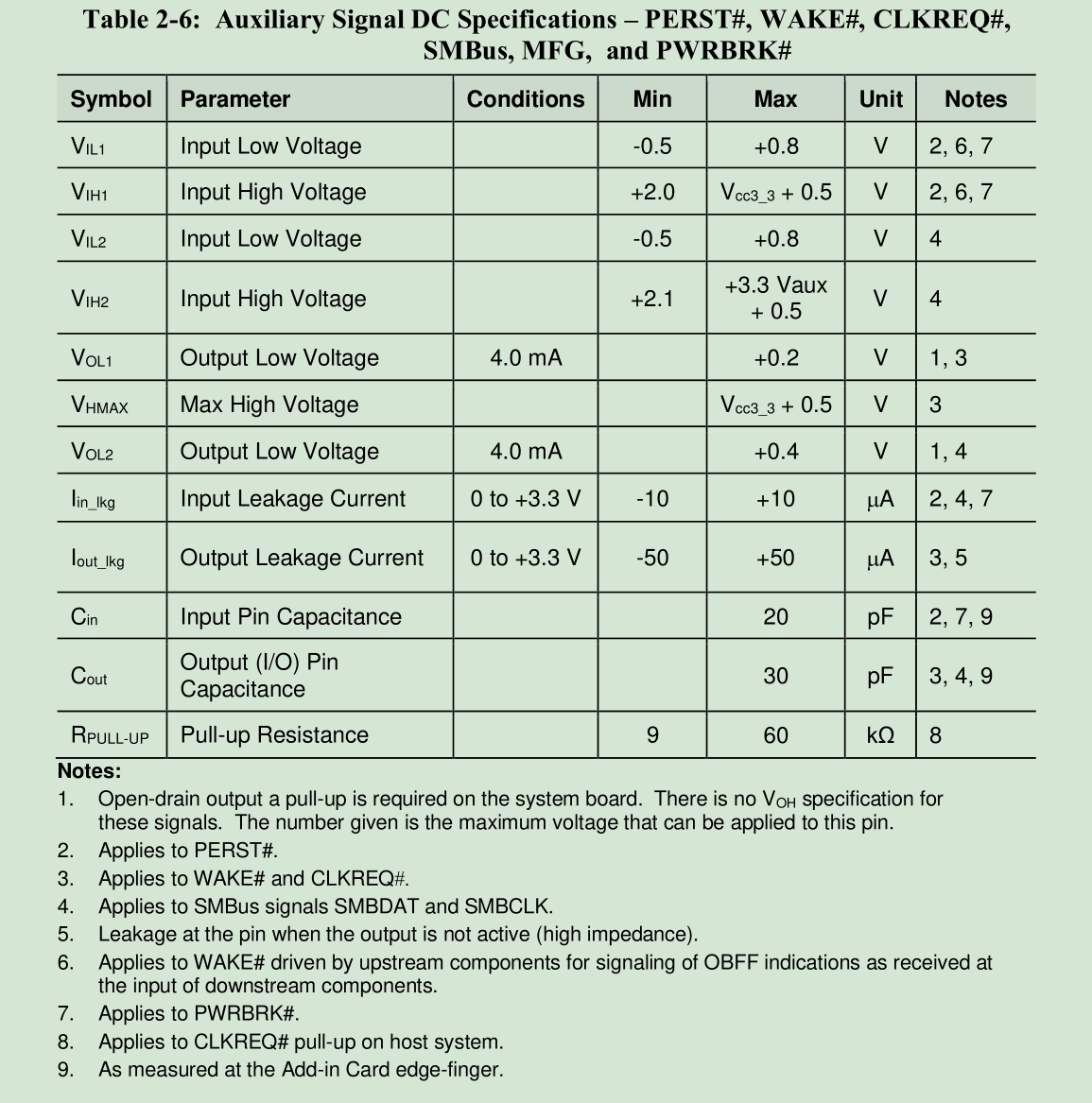

WAKE#信号是一种开漏(Open Drain)结构,低电平有效的信号。主要用于唤醒插槽上的主电源和参考时钟等,进而唤醒链路(Links)。需要注意的是,WAKE#信号的电平变换操作与任何系统时钟都是异步的(Asynchronous)。

注:WAKE#和PME#是两码事,WAKE#不可以被直接连接到PME#信号上。PCI-PME#往往会产生中断信号,而WAKE#只是用于唤醒操作,一般并不会直接产生中断。

系统板上WAKE#的上拉电阻值必须考虑到WAKE#的寄生电容,以确保WAKE#在不超过100 ns的时间内充电到逻辑高压水平。(参考PCI本地总线规范,有关上拉电阻的信息)

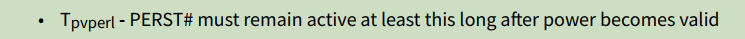

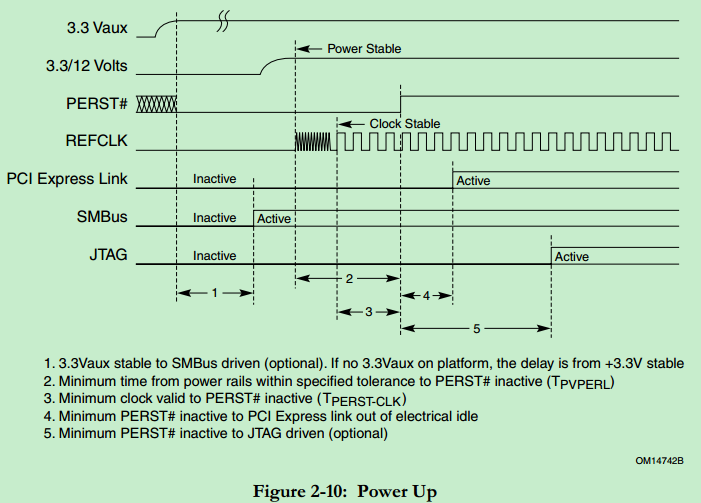

(5)PERST#(AIC Required/EDSFF Required)

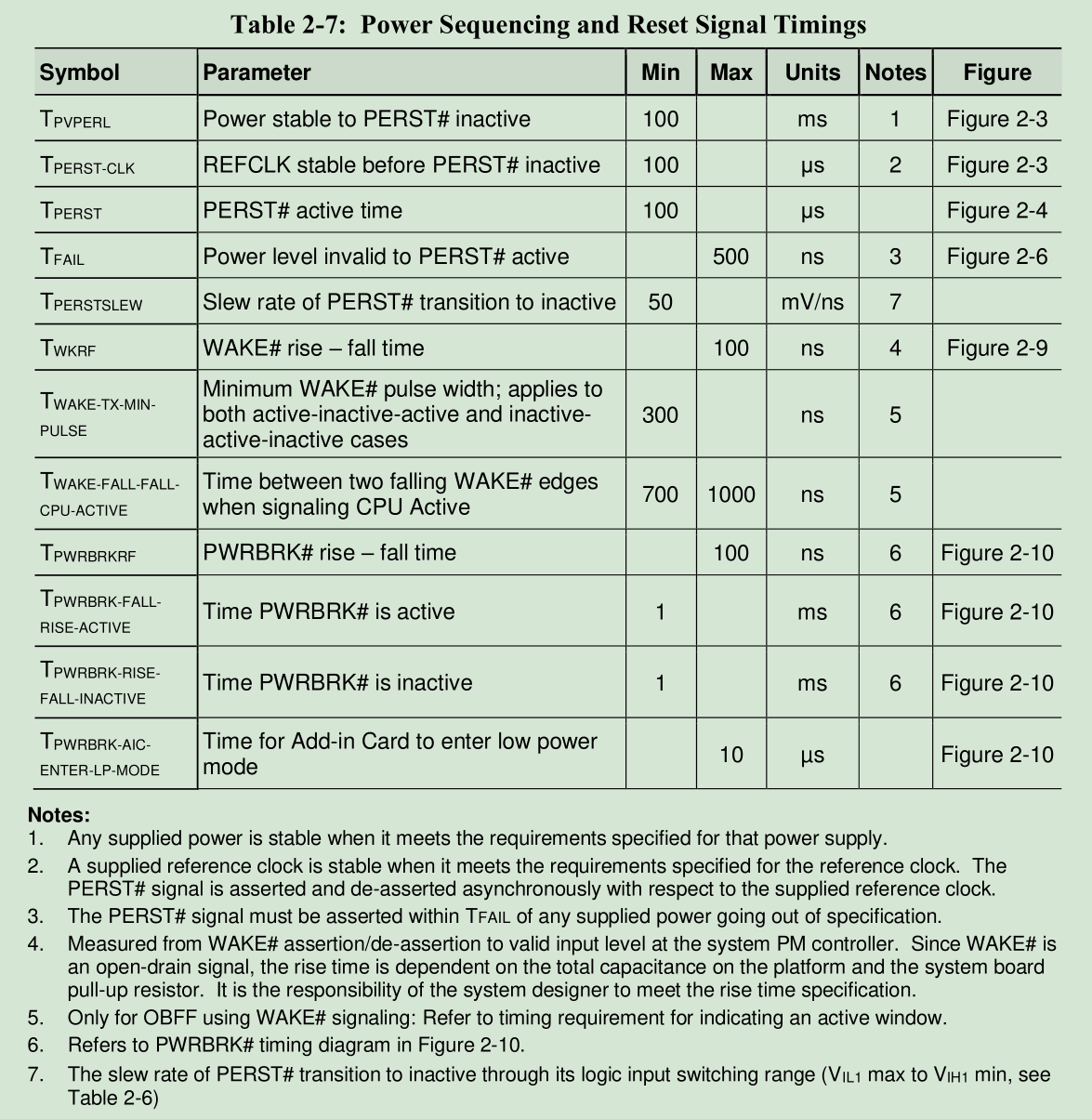

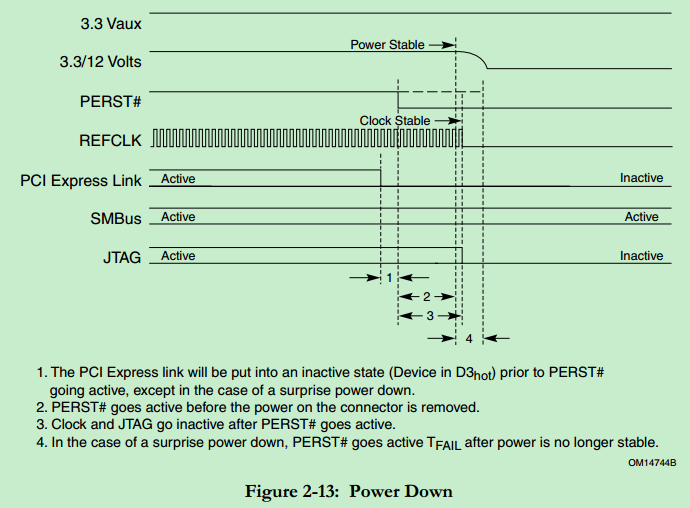

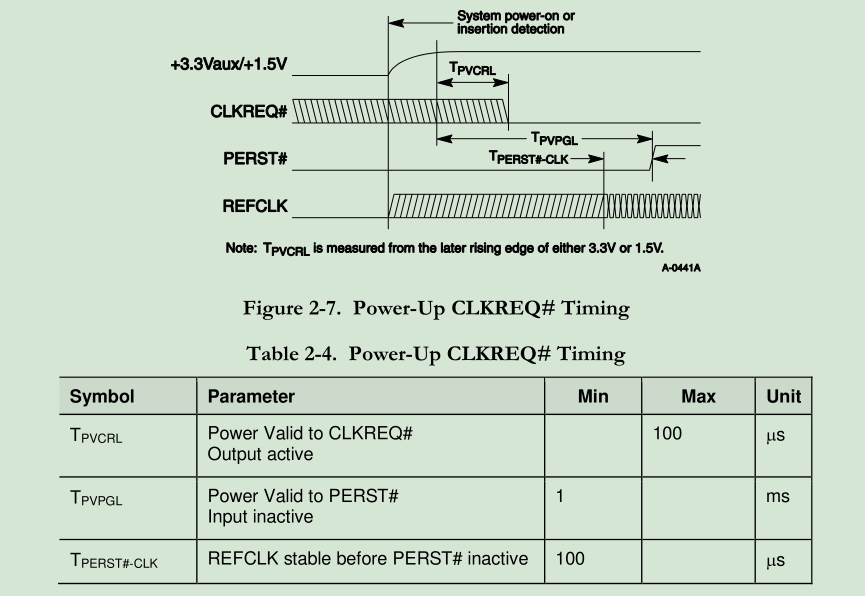

在电源和时钟稳定前,至少保证PERST#引脚拉低(2) T PVPERL和(3) T PERST-CLK,如以下三张图展示了各类电源状态和时序要求:

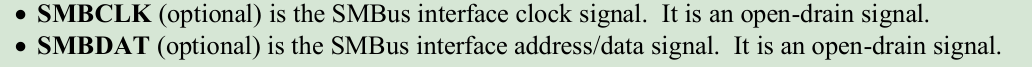

(6)SMBUS(AIC Optional/EDSFF Required)

AIC SMBus,系统板提供+3.3 Vaux的上拉

EDSFF上拉电阻推荐45kΩ以下:

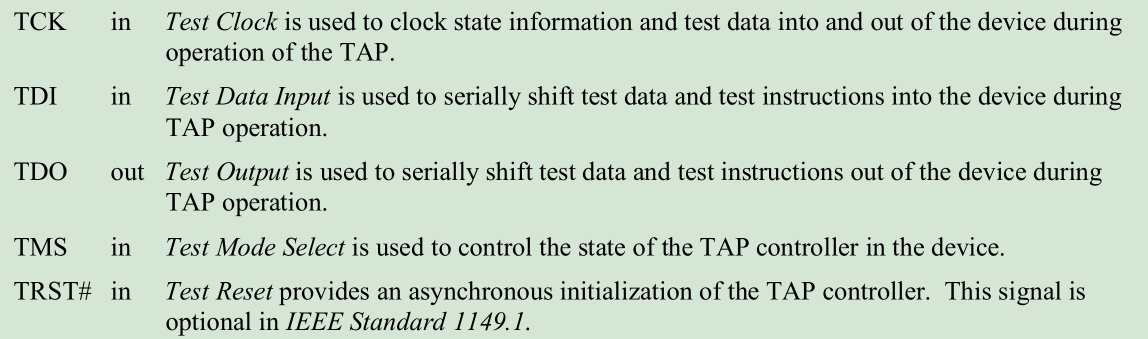

(7)JTAG(AIC Optional/EDSFF Optional)

(8)PWRBRK#(AIC Optional/EDSFF Optional)

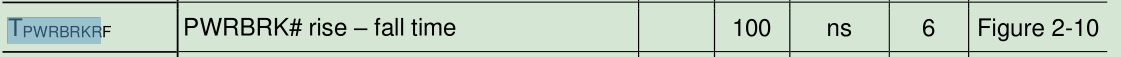

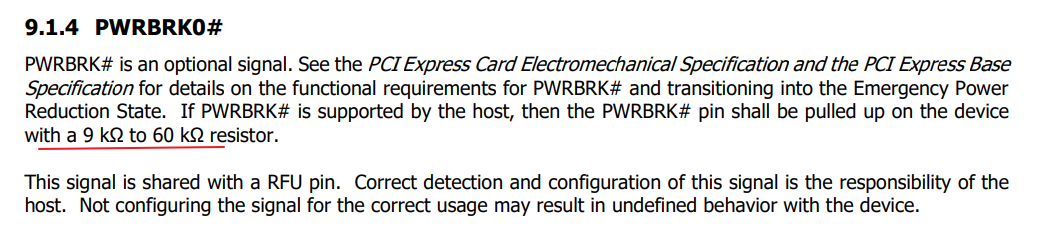

PWRBRK#与任何系统时钟都是异步的,低电平有效,开漏(Open Drain)结构。支持紧急电源减少的PCIe卡必须在PWRBRK#上提供弱上拉(最大95 KΩ),支持紧急断电的PCIe卡必须在PWRBRK#上提供更强的上拉。这些上拉电阻值必须保证满足T PWRBRKR的上升时间规范。

EDSFF要求上拉电阻9kΩ~60kΩ:

当host主动拉低PWRBRK#时,支持紧急电源减少的PCIe卡必须迅速降低其功耗;当解除PWRBRK状态时,支持紧急电源降低的PCIe卡允许恢复正常功耗。该机制是一种紧急故障安全机制,用于防止系统损坏,而不是用于提供正常的动态电源管理。

(9)MFG(AIC Optional/EDSFF Optional)

MFG是一个制造商测试模式信号,引脚功能由AIC制造商定义。

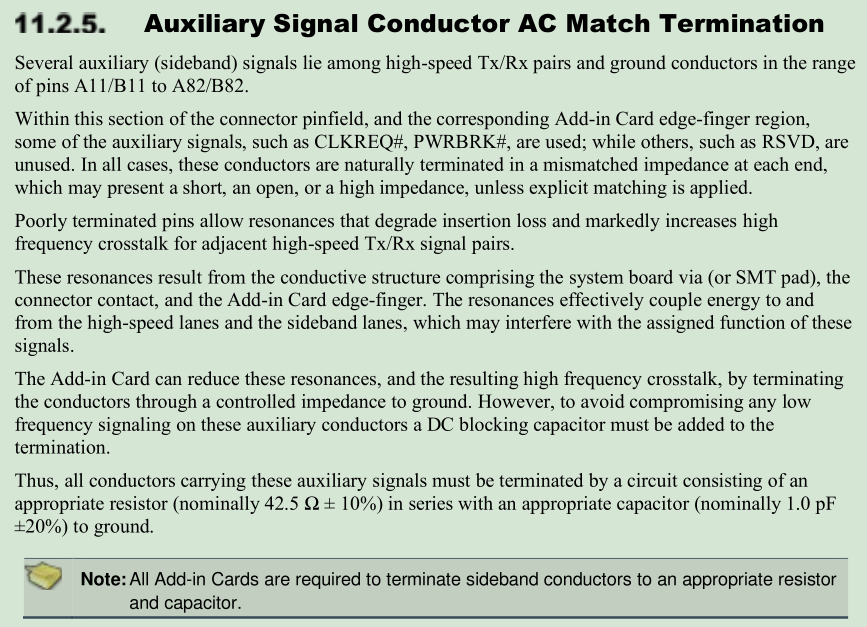

MFG引脚必须按照Spec规定采用交流端接(不得悬空),并且不得对正常的AIC操作产生任何影响。交流端接一般由电阻(42.5 Ω±10%)串联电容(1.0 pF±20%)端接接地,端接走线阻抗匹配42.5Ω(从金手指到DC Blocking电容),端接的接地孔必须位于电阻通孔1.0 mm (39.4 mil)以内。

【注】:以下信号悬空时必须进行AC端接

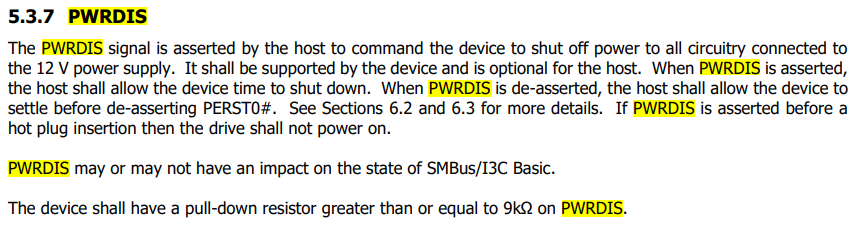

(10)PWRDIS#(EDSFF Required)

PWRDIS定义:当PWRDIS高电平有效时,host应切断卡的所有供电(12V power off)

①PWRDIS默认下拉(下拉电阻阻值<=9 kΩ)

②PWRDIS不得影响SMBus/I3C

(11)CLKREQ#(AIC Optional/EDSFF Optional)

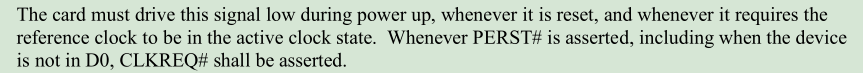

CLKREQ#与任何系统时钟都是异步的,是一个开漏结构信号,低电平有效,由PCIe卡驱动低电平请求参考时钟(用于PCI Express接口发送/接收数据)

在PCIe卡上电时,CLKREQ#信号必须被拉低(复位和需要参考时钟的时候)

当PERST#有效,包括PCIe不在D0状态时,CLKREQ#应被拉低,具体看时序图:

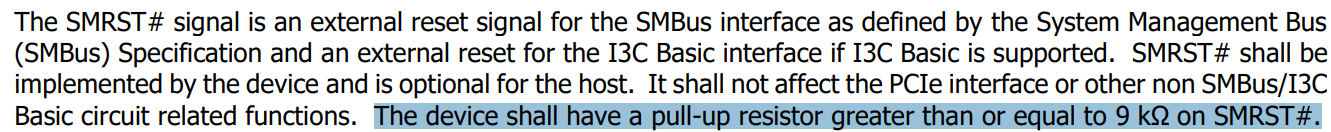

(12)SMRST(AIC Optional/EDSFF Required)

SMRST为SMBUS的复位引脚(支持I3C设备上存在),EDSFF 上拉电阻推荐9kΩ以下:

(13)DUALPORTEN#(EDSFF Required)

Dual port使能引脚,在Dualporten#上应有一个小于或等于4.7 kΩ的上拉电阻

(14)RSVD/RFU(Reserved)

预留引脚,不可悬空,AC端接

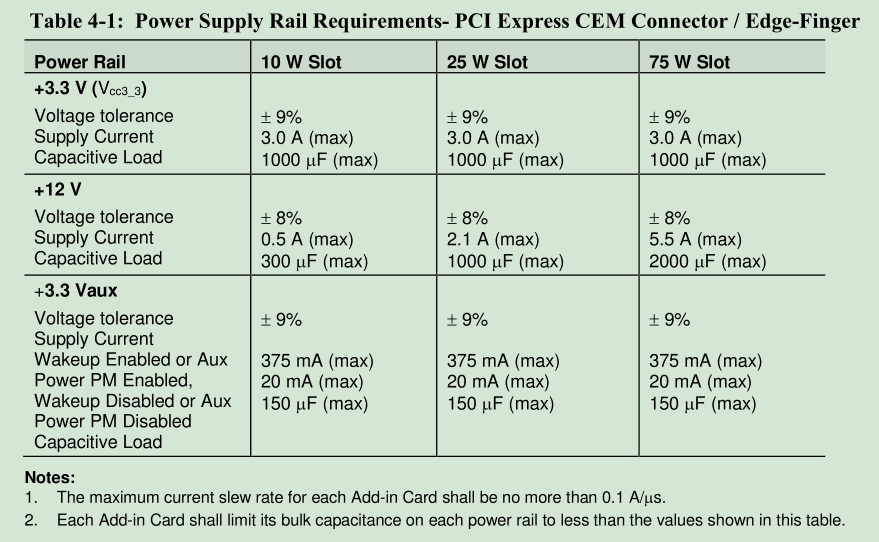

三、PCIe电源

(1)基本电源要求

PCI Express Card Electromechanical Specification要求至少两个电源:+12V和+3.3V,第三个辅助电源+3.3Vaux是可选的。各个电源的基本要求如下:

注:对于SMBUS和3.3Vaux的关系:

如果3.3Vaux不存在,12v存在,同时SMRST#无效时,则SMBus或I3C接口正常。

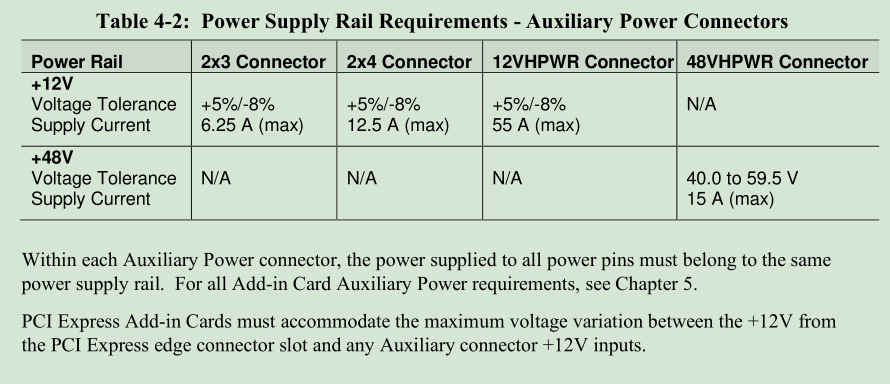

(2)EDSFF电源要求

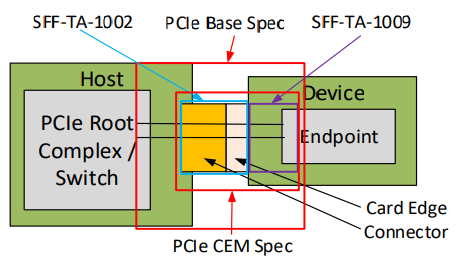

EDSFF电气参数参照SFF-TA-1009规范,连接器参照SFF-TA-1002规范:

EDSFF产品的电源要求会不同于AIC的基本电源要求:

四、硬件Layout

(1)Design rule

在PCIe布线过程中差分线会出现一些拐角。PCIe 3.0设计中一般采用45°拐角来进行布线,但是在PCIe 4.0、PCIe 5.0的差分线设计中尽量使用curved布线方式。因为在速率达到一定程度时,45°拐角走线会有比curved类型走线更大的阻抗突变。

在理想情况下共模信号是不变的,而且共模信号通常不携带任何信息,因此也不会影响到信号完整性和系统性能。但是当差分线的信号相位出现skew将会产生共模干扰,共模干扰比差分干扰的危害大得多,所以抑制差模转共模是有必要的。因此在进行PCIe 5.0的设计时需要进行动态等长绕线,减小共模干扰。

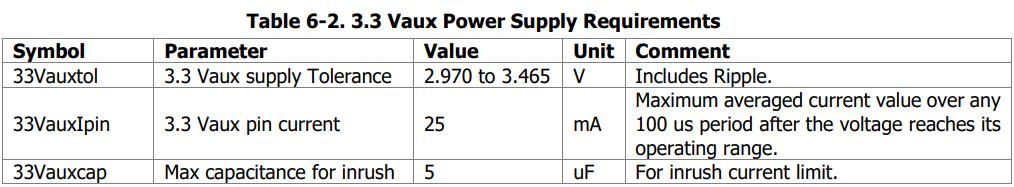

(2)玻纤效应

一般PCB的PP层是以glass weave(玻璃纤维)编织,然后再以环氧树脂包裹形成。从宏观角度,一般会用固定的介电系数表示,但对于PCIe 5.0这样的高速差分信号来说,如果走线顺着玻璃纤维编织方向0°或者90°,差分信号的正负信号会由于介质结构的不同导致特性阻抗变化,从而造成信号时延不匹配、眼图质量变差。通过仿真选择比较合适的玻纤布、走线宽度、走线距离,来避免玻纤效应带来的影响,并且在设计阶段可以让差分走线与玻纤编织方向有一定夹角,一般会使用类似Zig-Zag布线方式进行避免。除此之外在生产的时候可以选择将玻纤布的方向旋转10°~15°来减轻玻纤效应对信号的影响。

常见的玻纤布型号

Zig-Zag走线、Jogged走线和旋转拼板

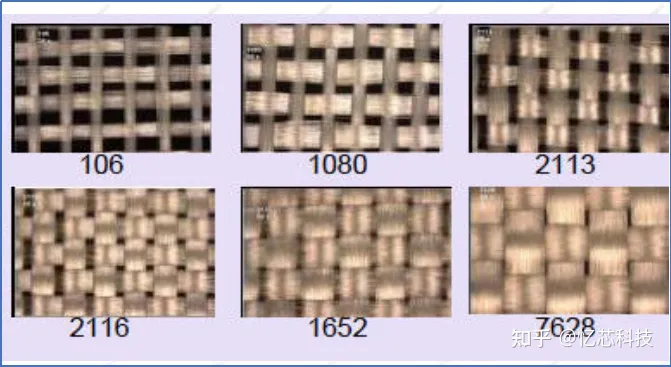

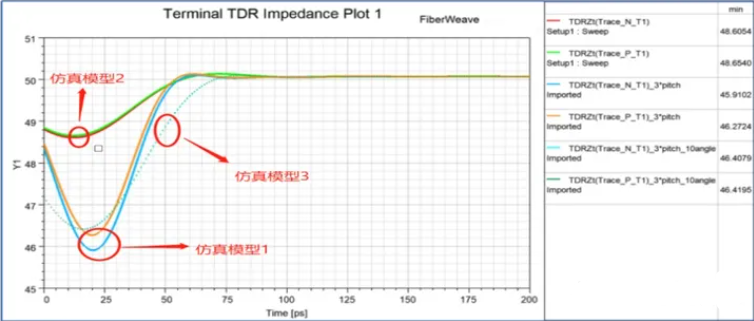

下图展示了三种结构下的差分信号线,模型1和模型2的玻纤布的pitch不同,模型三是将模型1的玻纤布旋转15°,使得差分线的正负信号线感受到的介质结构尽量一致。从仿真结果图6中可以看出:对于仿真模型1,当玻纤布的pitch比较大并且差分信号正负走线感受到玻纤布的介质结构不一样时,阻抗会有很大的跌落,并且两根信号线阻抗跌落程度不一致;对于仿真模型2,当玻纤布的pitch很小的时候,差分信号正负走线的特性阻抗基本一致,并且阻抗跌落也较小;对于仿真模型3,玻纤布的pitch比较大,但是将玻纤布旋转15°,差分信号正负走线的特性阻抗变得基本一致,并且阻抗跌落也有所减缓。

玻纤布仿真模型

TDR阻抗仿真结果

高速信号层会选择密集的玻璃纤维风格以获得更均匀的Ɛr,最大限度地减少阻抗和信号速度的变化。功率层和低速通用信号层会选择稀疏的玻璃纤维风格,以减少PCB成本。

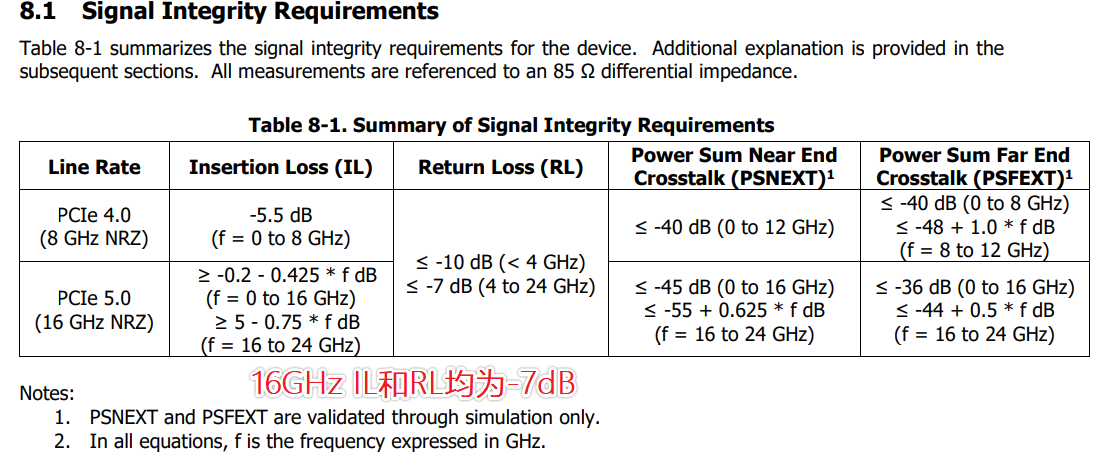

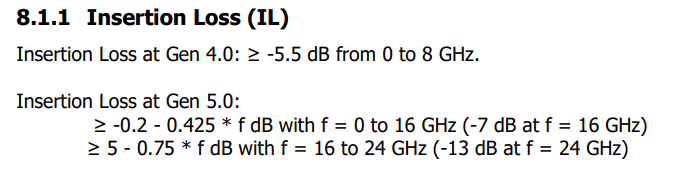

(3)EDSFF损耗要求

EDSFF损耗要求高于PCIe 5.0 CEM基本要求(-9.5dB@16GHz)

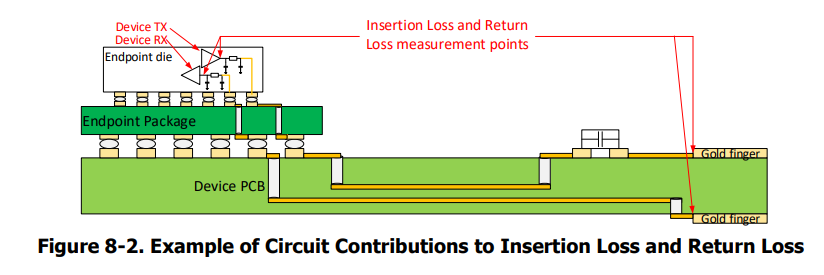

【注】:

①该损耗测量条件为差分走线控85Ω

②对于插损和回损,其被定义为从金手指到芯片内部Die对TX或RX的损耗测量。损耗计算应包括 Die寄生参数、封装参数、芯片ESD结构(但不包括驱动器的输出阻抗)、参考平面位置、PCB走线、过孔、隔直电容(只用于TX),需要注意的是金手指并不包括在损耗计算之中。如下图:

五、硬件仿真

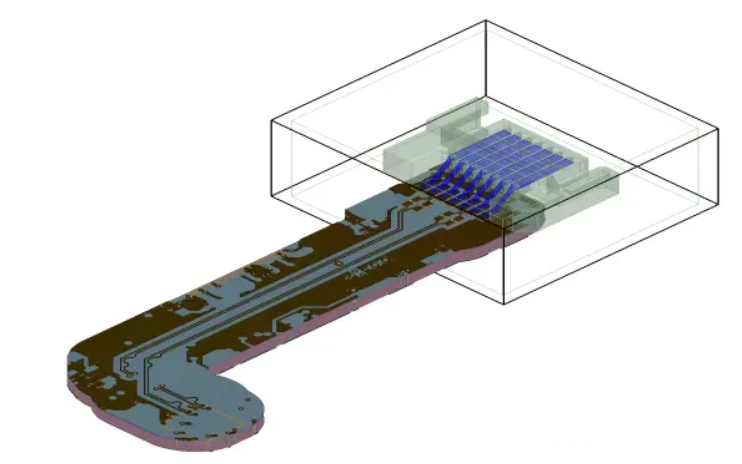

(1)PCIe 3D仿真模型

为保证PCIe端到端的信号完整性,必须对链路的长度以及信号轨之间的设计进行全面的仿真,并且满足相应速率下的插入损耗和串扰规范要求。在PCIe 3.0/4.0阶段全链路的仿真一般采用各个组件在各自求解域求解完成后,再进行S参数级联的仿真方法来进行全通道有源无源仿真。但是在PCIe 5.0的时候,速率越来越高设计裕量也越来越小,各个组件之间垂直互连的空间耦合也会越来越紧密,这将在一定程度上影响信号完整性,所以在仿真阶段需要考虑垂直互联的影响。垂直互连访问包括 VIA、球栅阵列 (BGA) 球、连接器、隔直电容等。因此在进行PCIe 5.0全通道仿真的时候需要对PKG、PCB和connector进行物理结构的互联,再进行参数提取、瞬态求解。

全通道3D仿真模型

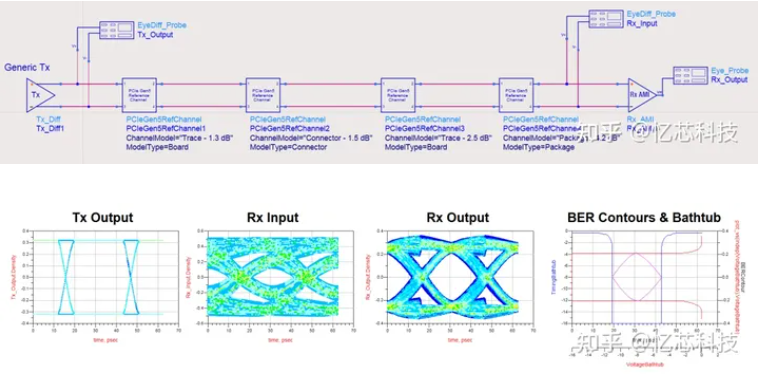

(2)PCIe IBIS-AMI仿真

PCIe 5.0在TX端使用三阶FIR滤波器,通过对高频分量的增强和低频分量的减弱来减小信号在高速链路中对高频信号高损的影响。在RX端使用二阶CTLE和三阶DFE技术,以应对更高的信号速率,使闭合的眼图张开。CTLE可以减小高频通道损耗,DFE则可以减小ISI带来的信号的恶化。

进行PCIe全链路有源仿真的最佳方法是使用带有EQ功能的IBIS-AMI模型及PKG、PCB、Connector的无源通道参数进行眼图仿真。可以通过仿真找出链路在EQ组合下的最佳眼图,与协会标准进行对比,评判设计是否满足要求。

PCIe 5.0全通道时域眼图仿真

六、硬件测试

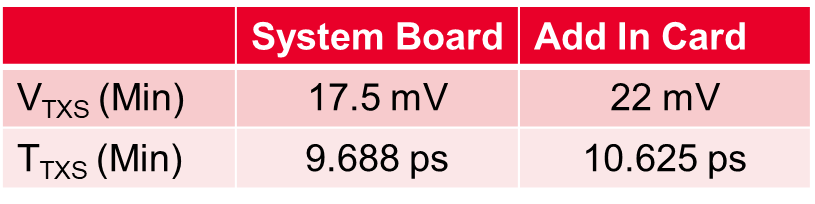

(1)PCIe 5.0 发射机Tx测试

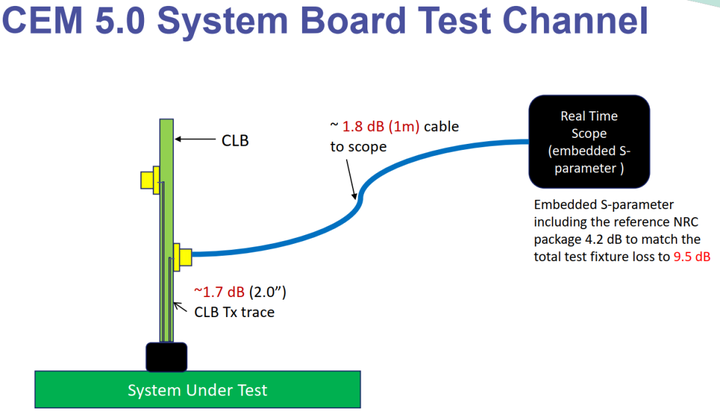

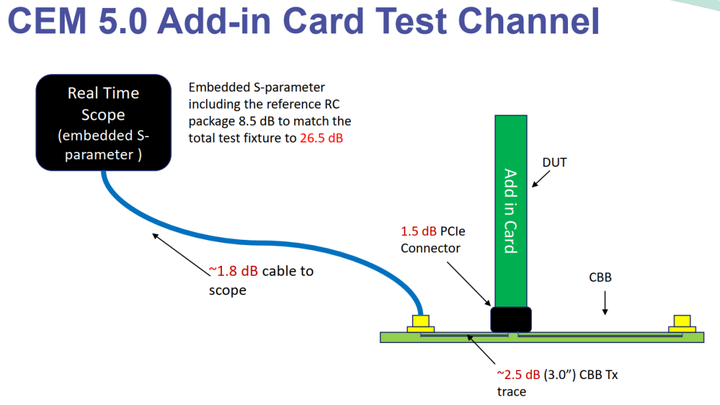

①PCIe 5.0的CEM中定义了系统主板和 AIC卡发射机 Tx 眼图的指标如下:

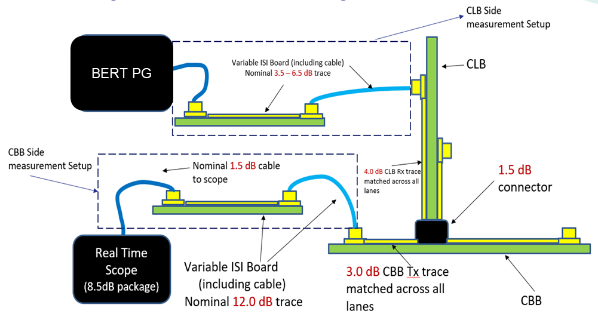

发射机Tx测试是基于以下系统链路分配的组网环境完成的:

其中包括测试通道以及对端芯片封装模型,具体测试组网将在第③点详细说明。

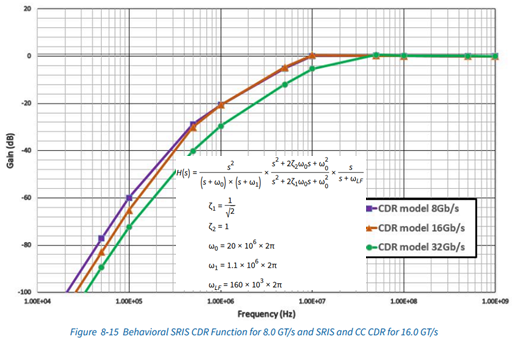

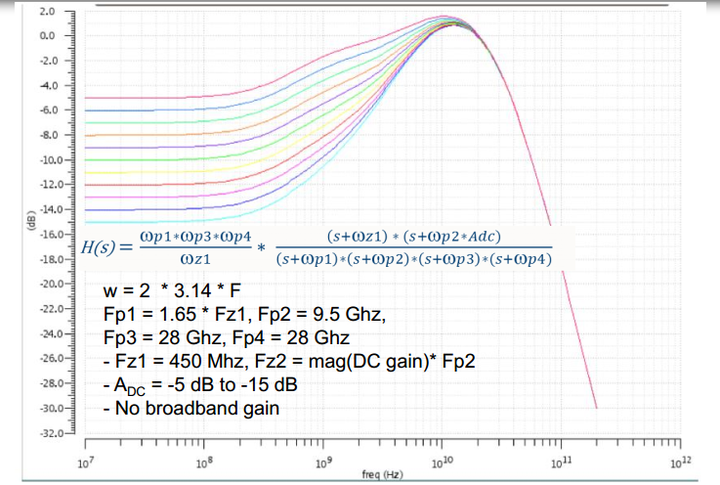

另外,在做眼图的信号参数计算时,需要经过PCIe 5.0基础规范里定义 CDR 和接收均衡器 (CTLE+DFE) 模型,PCIE 5.0 CDR和均衡模型如下图所示:

目前官方已经发布了初步的 PCIe 5.0软件工具 Sigtest Phoenix 5.0.10 Beta版本,支持基础规范和 CEM 规范的大部分校准和测试场景,相信后续还会逐步完善。

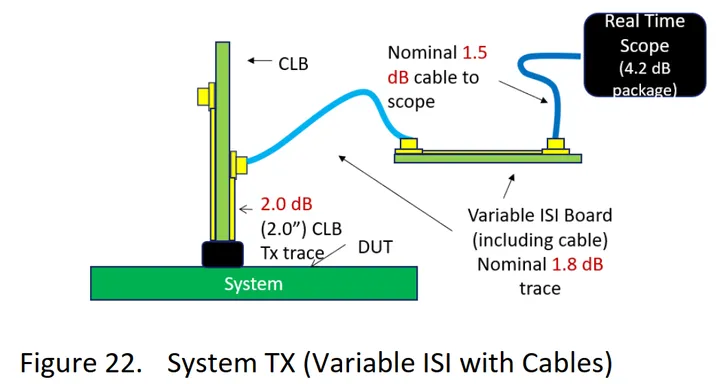

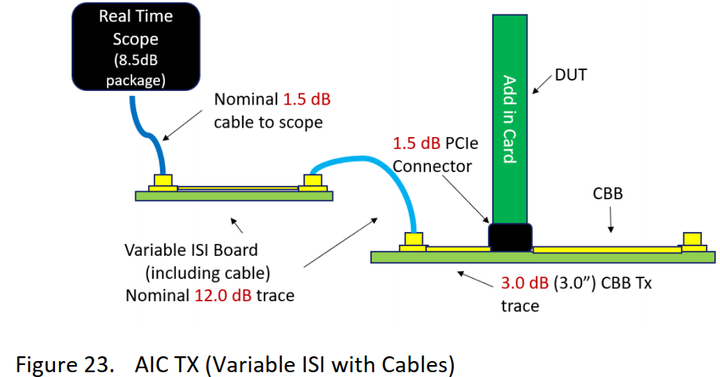

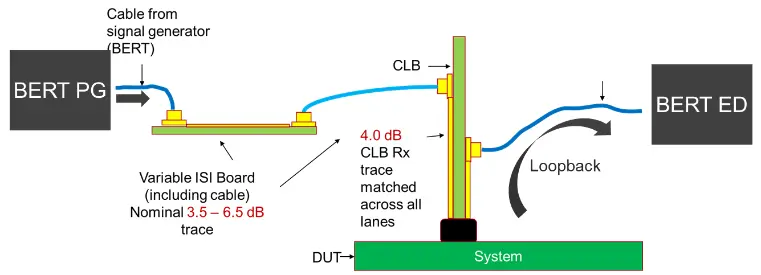

②对系统主板的测试,PCIe 5.0 32 GT/s不再使用Dual Port 测试方法,也就是说,测试发射机 Tx 时只需要将测试Data Lane的差分信号接到示波器,不需要同时捕获差分时钟信号。但有一点需要明确的是,在 16 GT/s 及以下速率依旧采用 Dual Port 测试方式,对于 16 GT/s的测试采用同轴电缆连接的方式,仍然需要4通道同时打开时示波器维持 25 GHz 带宽。下图展示了PCIe 5.0 32GT/s系统主板和 AIC 的测试组网方法:

③自PCIe 4.0开始,CEM 夹具里引入了可变ISI板夹具,这个夹具上设计了以接近 0.5 dB损耗步进的若干差分走线对,在发射机/接收机 Tx/Rx 测试之前,需要使用网络分析仪 VNA 标定和选取合适的走线对,构建规范要求的总链路损耗目标。如上图所示Tx测试时级联经过标定的ISI走线对,以及示波器嵌入对端芯片封装损耗。

有一点变化的是,对于PCIe 5.0 发射机 Tx 测试,协会会也在考虑使用 S 参数嵌入的方式,取代可变 ISI 板,将上述的 发射机 Tx 测试组网简化为测试组网图,在示波器内嵌入除了夹具和测试电缆外的链路损耗 S 参数,以下为采用软件嵌入 S 参数方法简化的 CEM 发射机 TX 测试组网图:

在 PCIe 5.0 PHY Test Spec v0.5中,对发射机 Tx 测试已经按这种嵌入 S 参数的方式要求,但这种方式与硬件ISI夹具连接的方式对测量结果的一致性如何?PCI-SIG协会计划在我前面提到的明年PCIe 5.0初步workshop中进行验证和比对。需要注意,用 S 参数取代走线的方法这只适用于发射机 Tx 测试,接收机 Rx 测试仍然需要使用实际的可变 ISI 夹具板。

④在 PCIe 4.0 之前规范采用 Dual Port 的测试方法,基于系统主板的Common Clock架构,对系统发射端包括参考时钟在内的特性进行评估,但PCIe 5.0取消了Dual Port的测试方法,只测试发射机 Tx 信号链路特性,这对于提供参考时钟架构下的主板和 AIC 互操作可能存在一定风险,所以从 PCIe 5.0 开始,对系统主板的参考时钟有专门的测试要求,会在第(2)节PCIe 5.0 参考时钟抖动测试进行解释。

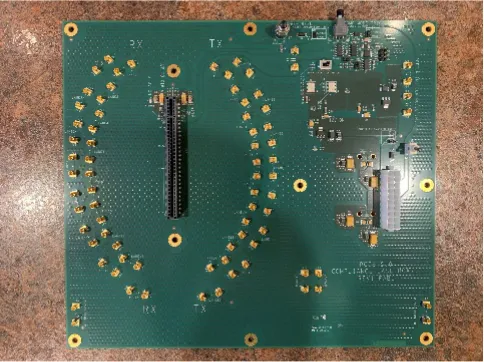

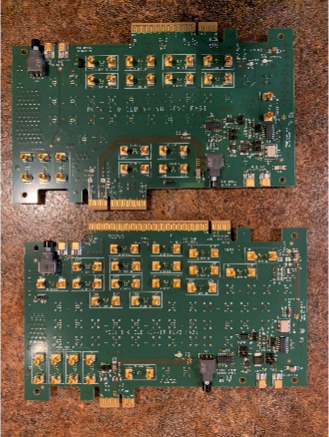

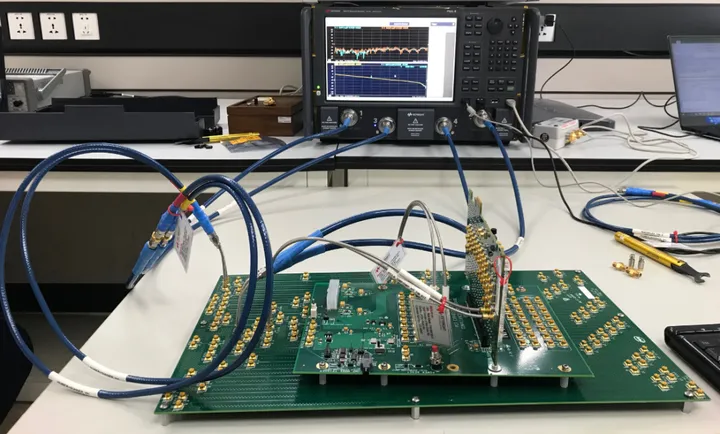

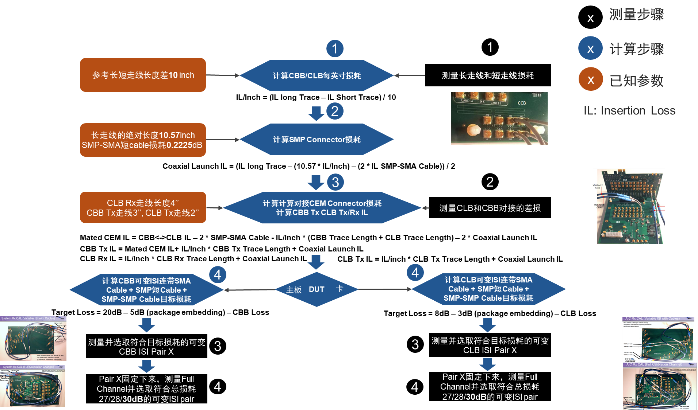

夹具套件中包含了 CBB,CLB 和可变 ISI 板,及若干 MMPX 短线。需要使用频率范围至少 20 GHz 的 VNA,测量在 PCIe 5.0 32GT/s的奈奎斯特频率点 16 GHz 下,电缆、夹具 PCB、接头、CEM插槽等损耗,选取Tx和Rx测试目标损耗所需要的ISI走线对,总体测量和标定方法与PCIe 4.0类似,如下所示,用 PNA-X系列VNA 测量完整通道组网损耗的测试实物图,及标定夹具流程图:

⑥PCIe 5.0 CEM Tx测试的几个问题

a.CEM Tx测试带宽和采样率的要求

在 PCIe 5.0 PHY Test Spec中,对于 AIC 或者系统主板Tx 信号质量一致性测试,要求示波器的带宽设置为 33 GHz,采样率至少达到 128 GSa/s,如果示波器硬件采样率达不到这个要求,允许使用Sin(x)/x内插,但至多允许加入一个内插点,也就是最多是原始采样率的两倍,保证每个UI至少有4个采样点。

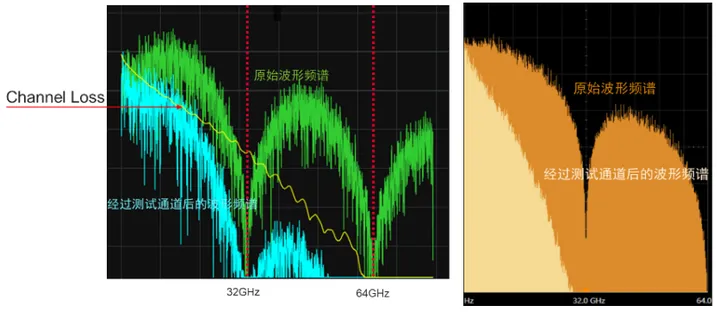

关于 CEM Tx 测试带宽问题的理解,由于在系统级的测试,考虑到CEM端到端的链路损耗达到 -36 dB@16GHz,原始信号(下图绿色频域谱线)经过传输测试通道的低通特性后,信号中的高频成分被相当程度的抑制( -36dB @ 16 GHz),由于示波器本身的动态范围的限制,高频成分会淹没在仪器本身的噪声中,对信号均衡和重建来说,低信噪比的高频成分并不会提升信号本身的计算精度,协会要求的 33 GHz带宽是一个合理的选择。但从另外一个角度来看,提升示波器的 ADC 分辨率并降低仪器本底噪声是提升测量精度的不二选择。

上述要求针对的是Tx的信号质量测试的示波器带宽选择,对于Tx Link EQ与上述的要求一致,同样是 33 GHz 带宽,128 GSa/s采样率。但有一点需要注意,Tx Link EQ的测试组网中,BERT误码仪输出的差分信号,以及DUT环回的差分信号,分别通过同轴分路连接的方式连接到示波器的 4 路通道,进行激励响应测试,也就是说示波器在4通道同时工作时要满足33GHz带宽要求。

PCIe 5.0 测试在做Rx校准时,示波器带宽至少需要 50 GHz。

以下是PCIE5.0 TX LinkEQ 测试组网示意图:

另外补充一点:PHY Test Spec定义的是对系统级别的测试要求,对于 PCIe 5.0 的芯片测试,要遵循 PCIe 5.0 Base Spec,要求的示波器带宽 50 GHz。

b.测量精度的影响因素

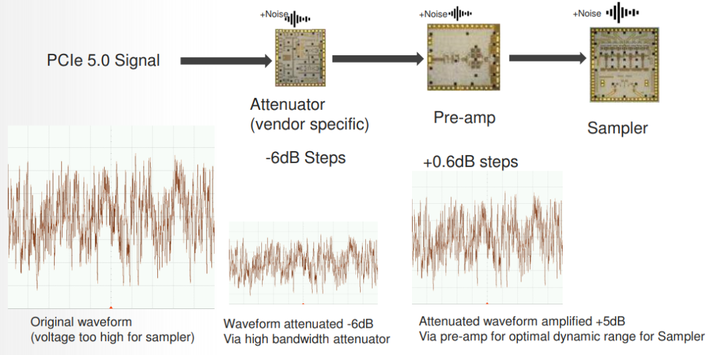

前面讲到,由于信号经过链路衰减,以及示波器本身的动态范围的影响,在Tx测试时规范要求了折衷的33GHz。在这种测量链路环境下,测试仪器本身和测试方法对测量结果的影响是不可忽略的,下面我们来分析一下,哪些因素会影响到信号的测量精度。示波器内的信号采集链如下图所示:

信号进入示波器后,经过模拟前端包括衰减器、放大器、采样器,再进入到 ADC,示波器中所使用的半导体工艺、封装设计、互连设计,ADC 的垂直有效位数等的差异,会导致信噪比会存在差距。所以,降低仪器底噪、提升 ADC 的位数会为提升测量精度带来非常大的帮助,在足够采样率的条件下,这些性能超过了采用更高采样率对测量结果的影响。

另外从测量方法上来说,垂直刻度的设定会影响到测量的信噪比,测量时有一点比较重要的是,要优化垂直刻度,让信号尽量充满垂直满量程,这样会达到最佳的测量信噪比。在Keysight 提交给协会的测试数据也验证了这样的观点,从下表中可以看到,在相同的测试条件下:使用 M8040A误码仪,加入一定的压力,经过 PCIe 5.0 Base夹具构建的36dB的损耗,设置相同的 Preset P9,使用相同的接收 CTLE DC Gain 10dB,示波器都优化调整了垂直刻度。

(2)PCIe 5.0 参考时钟抖动测试

如前文所述,PCIe 5.0 取消了系统主板 Dual Port 测试模式,但专门定义了参考时钟的测试内容。

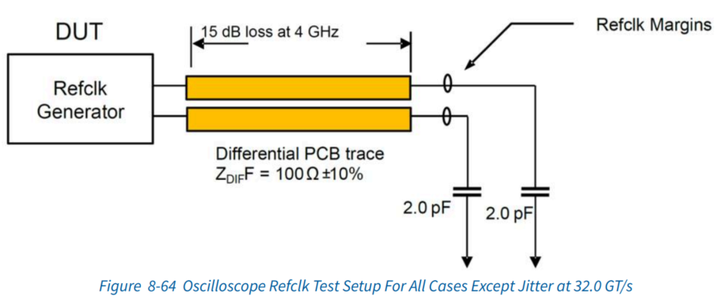

PCIe 4.0 及之前的规范,参考时钟的抖动要求只在基础规范里有所体现,我们先来回顾一下在基础规范中对参考时钟抖动的要求,基于共同时钟架构中 Tx/Rx PLL 及 CDR 的传递函数组合下,32 GT/s的参考时钟抖动小于或等于150 fs RMS,考虑到系统互连引入的噪声,这个指标放宽到 250 fs RMS,但测试组网不同以往,32GT/s的参考时钟需要通过50ohm端接的方式直接测量,也取消了之前定义的参考通道,这样做主要是为了提升信噪比提高测量精度。

Base Spec PCIe 5.0 REF CLK测试说明:

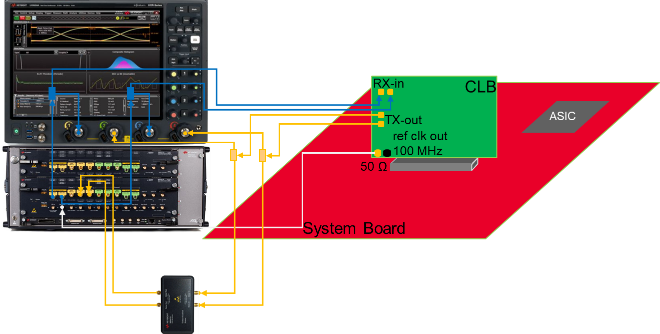

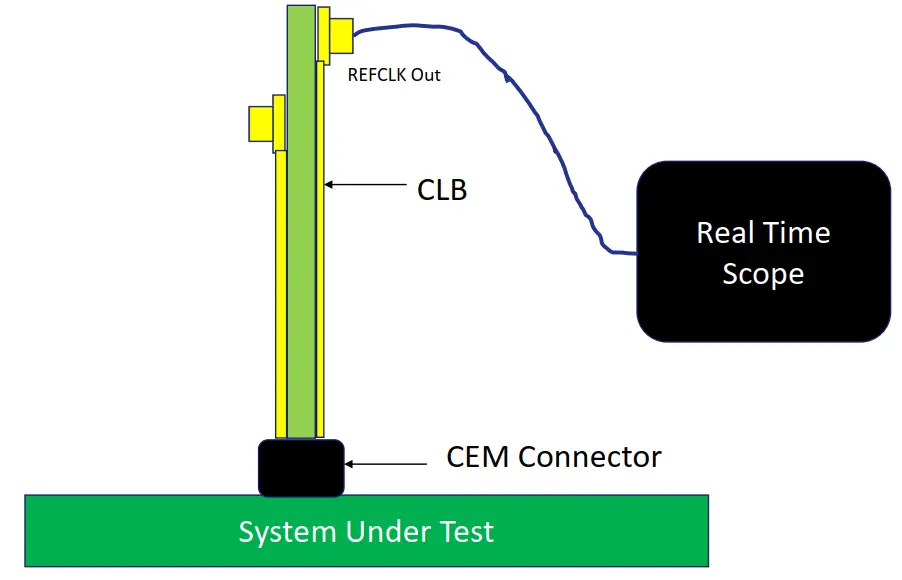

在系统级的 PCIe 5.0 PHY Test Spec v0.5 版本已经列入了参考时钟抖动的测试内容,将 CLB边缘 SMP 接口的时钟信号直接通过同轴电缆接入示波器,示波器带宽至少 5 GHz,这部分内容可以关注后续更新,目前抖动参数的范围和抖动测试工具还处于 TBD 的状态。

越来越高的参考时钟抖动要求对测量工具的触发抖动和本底抖动即通道间的固有抖动(差分测量需考虑通道间固有抖动)等指标都提出了越来越高的要求和挑战。

10 月底,Intel 提交了参考时钟初步建议,其中Rj的数值建议为 200 fs,从测试的角度来看,由于规范要求的指标范围非常苛刻,虽然测试算法中会加入多组传递函数滤波器,但仪器自身的固有抖动如果太大,可能还是会对测量结果的裕度造成影响。

REF CLK测试示意图:

另外, Intel 已经向其 OEM/ODM 发布了 Intel Clock Jitter Analysis Tool可以进行 PCIe 5.0 参考时钟抖动测试,其中有一些很有特色的功能比如示波器底噪去嵌,Midbus探测,自动带宽限制等功能。

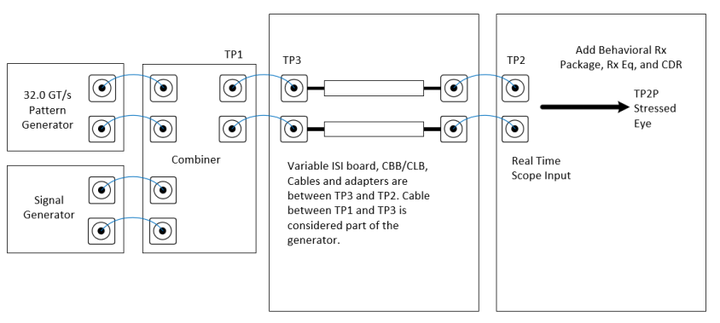

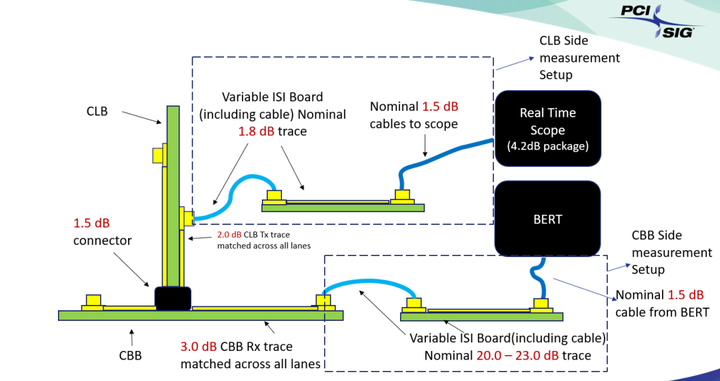

(3)PCIe 5.0 Rx测试

首先看一下 5.0 的校准:校准分为两个测试点,如下图所示,分别是在TP3点也就是BERT输出经过电缆连接到示波器,分别校准信号幅度800mV/720mV,TxEQ,Rj,Sj,第二个部分是从TP3继续延伸经过可变ISI板及CBB和CLB后的TP2点,示波器内嵌入芯片封装S参数,以及经过参考CDR和均衡器后TP2P的压力眼图校准,TP2P校准的目标值分别为EH 15+/-1.5mV, EW 9.375+/-0.5ps。

PCIe 5.0 RX 测试校准点示意图:

需要注意的是 32 GT/s 的 Rx 校准要求示波器带宽设置为 50 GHz,采样率大于或等于128 GSa/s,并且由于TP3点的校准电压为差分 800 mV,50 GHz带宽示波器通道的输入电压要满足这个幅度测量量程,如果加入外部衰减器,因为 TP2P点校准要经过最大 loss 达到 37 dB 的损耗,在加入外部衰减器的情况下,信噪比再度恶化会造成校准精度的恶化。

完整的通道选取校准要从最大的包括封装损耗的 -37 dB 开始 ( PCIe 4.0 PHY Test Spec v1.01 标准也要求从最大 -30dB开始),搜寻 Preset 和 CTLE 组合,找到最大的EH*EW 眼面积,然后扫描 Sj 和 DMI,以及可以调整Vswing,计算EH和EW是否落在EH 15+/-1.5mV, EW 9.375+/-0.5ps范围,如果不满足,就步进减小ISI pair,重复上述过程,注意每一步都要扫描Preset 和 CTLE 组合,直到找到这个 ISI pair,最小可用的ISI 损耗是 -34dB。下图是系统主板和AIC的完整通道校准组网。如果不能完全遵守规范的要求,可能导致加压SJ/DMSI等达不到规范的要求,就无法真实反映 DUT 的 Rx 性能。

PCIe 5.0 RX测试校准组网图:

系统主板Rx LEQ测试组网图:

Rx LEQ测试是评价被测件Rx对压力信号的容忍性能,反映的是Rx端对抖动跟踪能力和对恶化信号的均衡能力,以误码率来评价。

测试要尽量避免在环回路径引入误码,由于服务器主板 32 GT/s环回信号损耗较大,在环回测试时,信号经过CLB直接接入BERT ED,不加额外ISI板,可以训练DUT目标TxEQ值,使环回信号Tx质量调优,SEG工作组也有讨论允许在信号环回接到BERT的路径上加入外部repeater,PCIe 5.0 Rx 测试的 BERT M8040A 的ED自带内部均衡器,避免由于环回信号衰减引入的额外误码。

七、参考文章

3、Gen-Z 可扩展连接器和SFF-TA-1002规范。-CSDN博客

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/115426.html