大家好,欢迎来到IT知识分享网。

文章目录

- 一、MIPI接口

- 二、网口

- 三、SRIO

-

- 1、基本介绍

- 2、[DSP与FPGA间实现SRIO及其初始化配置](https://zhuanlan.zhihu.com/p/)

- 四、PCIE

- 五、JESD204B

- 附:各类接口电平标准介绍

一、MIPI接口

1、基本介绍

- MIPI D-PHY是一种低功耗、低成本的物理层协议,支持最高1.5Gbps的传输速率;

- MIPI C-PHY是一种高带宽、低功耗的物理层协议,支持最高6Gbps的传输速率;

- MIPI M-PHY是一种高性能、高可靠性的物理层协议,支持最高11.6Gbps的传输速率。

- D-PHY和C-PHY的硬件区别:D-PHY有专门的一对时钟线,DDR双边沿对数据采样,C-PHY没有专门的时钟线,采用时钟恢复技术。

- D-PHY支持HS(High Speed)和LP(Low Power)两种模式,HS模式采用低压差分信号传输(SLVS电平),功耗较大,但可以传输很高的数据速率(80M~1.5G),采用源同步的方式,由主机向从机提供DDR时钟;LP模式采用单端信号(1.2V LVCMOS),功耗低,速率低(10M以下),用于传输初始化控制信号和状态判断,LP模式下只有lane0实现双向数据传输。

- 目前,Xilinx仅在Ultrascale+及其以上版本的FPGA IO可直接支持MIPI 电平输入,其他的,需要转换成LVDS来接收,SLVS转成LVDS,可通过专门的电平转换芯片,如MC20901,或者采用电阻匹配网络。

- SLVS电平的摆幅很低(200mV),LVDS(350mV),把终端电阻加大(150Ω,需要注意的是内部的DIFF_TERM要False掉)一点儿,确保差分终端电阻两端的电压够LVDS的裁决门限;至于低速LP信号,分出来以后要是BANK富裕可以专门搞一个1.2V的bank,如果不富裕,可以加一个输入阻抗很大的电平转换芯片(比如74LVC1T45)把它转成任意你想要的电平标准,比如1.8V、2.5V或3.3V。整个输入的网络结构如下图。

3、MIPI接口支持不同的数据编码格式,包括RGB、YUV和RAW等。RGB是一种常见的色彩编码格式,用于表示红、绿、蓝三原色;YUV是一种亮度和色度分离的编码格式,可以有效地压缩数据量,从而节省带宽和存储空间;RAW是一种未经压缩的原始数据格式,可以提供最高质量的图像数据。MIPI接口还支持不同的数据位宽,包括8位、10位和12位等。

二、网口

1、设计事项

三、SRIO

1、基本介绍

2、DSP与FPGA间实现SRIO及其初始化配置

四、PCIE

1、基本介绍

1、PCIE各个版本的速率支持

| 版本 | 速率支持 | 编码方式 | 调制样式 |

|---|---|---|---|

| PCIE1.0 | 2.5G | 8b/10b | NRZ |

| PCIE2.0 | 5G | 8b/10b | NRZ |

| PCIE3.0 | 8G | 128b/130b | NRZ |

| PCIE4.0 | 16G | 128b/130b | NRZ |

| PCIE5.0 | 32G | 128b/130b | NRZ |

| PCIE6.0 | 64G | 1b/1b | PAM4 |

| PCIE7.0 | 128G | 1b/1b | PAM4 |

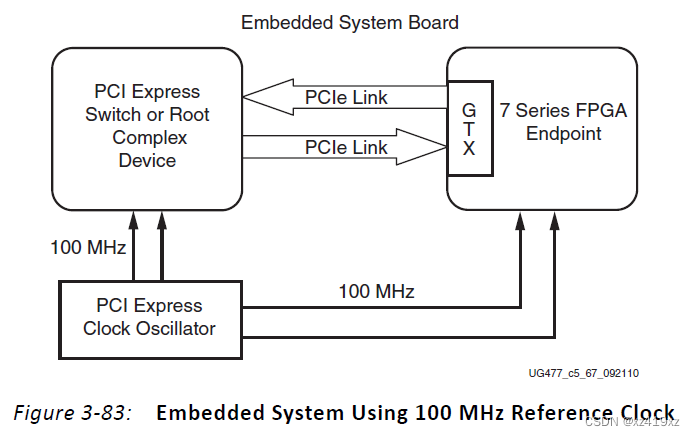

- PCIe 协议指定标准的参考时钟为 HCSL 电平的 100 MHz 时钟,Gen1~Gen4 下要求收发端参考时钟精度在 ±300 ppm 以内,Gen5 要求频率稳定性 ±100 ppm。

- CC即时钟同源模式,大多数系统均采用此时钟架构,xilinx pg054推荐采用同源时钟。Common Clock 对于频率稳定性的要求是 ±300 ppm。对于使用同一 Common Clock 作为参考时钟的 PCIe 设备,所有设备间的时钟偏斜(Clock Skew)必须保持在 12 ns 以内

- separate reference独立时钟模式,根据有无 SSC[spread spectrum clock/扩频时钟]可进一步分为 SRNS ( Separate Refclk with No SSC) 及 SRIS (Separate Refclk with Independent SSC)。

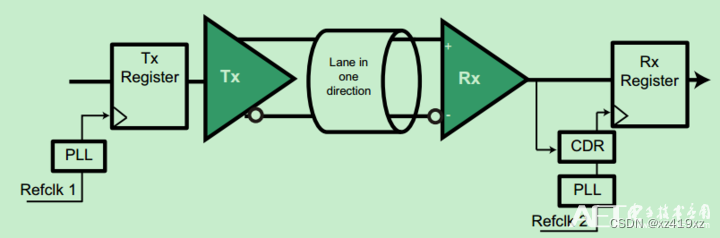

- DC数据时钟模式,仅发送端需要 Refclk,接收端无需外部 RefClk,其 CDR (Clock Data Recovery,时钟数据恢复)的 Refclk 参考时钟从数据流中恢复出来。

Data Clock 时钟方案仅适用于 Gen2 及 Gen3,单 lane 单向最高速率 8GT/s

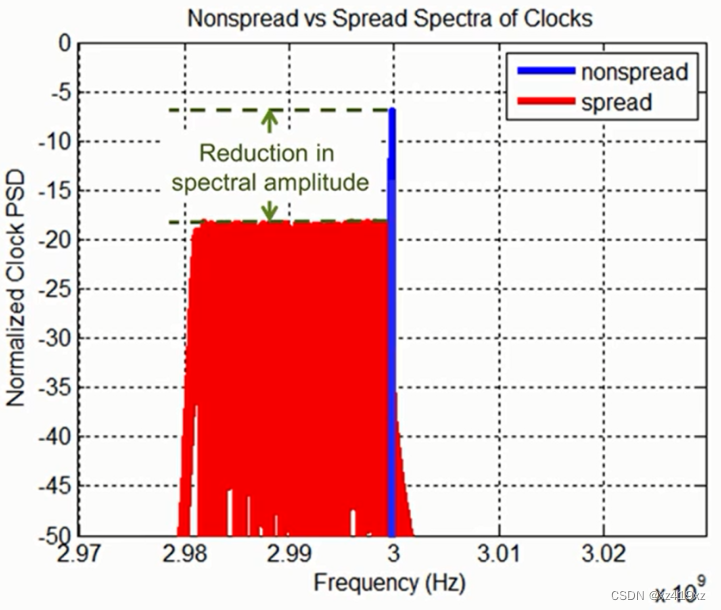

- SSC[spread spectrum clock/扩频时钟]。扩频时钟是以受控方式对系统时钟进行抖动以降低峰值能量含量的过程。主要用来抑制电磁干扰(EMI),降低 PCIe 时钟及数据线的电磁辐射、增强高速数据传输可靠性。PCIE的扩频时钟是可选,非强制的。

PCIe 扩频模式为向下扩频,扩频范围为-0.5%~0%,确保最大频率在标称频率之下。最大调制幅度为 -0.5%。

调制频率为 30 KHz ~ 33 KHz,确保 PLL 能够跟得上,同时减小音频噪声的引入。

调制波形采用三角波,该波形易于实现,且调制后的频谱接近均匀分布。

参考时钟源的抖动(Jitter)需在300ppm以内。

2、链路同步

2.1、基本介绍

- lane Reversal:通道翻转,该功能用于解决PCIE通道两端设备存在lane交叉的问题,需注意PCIE协议未对该功能做强制要求,故设计者如需使用该功能,需要核对PCIE设备是否支持该功能。

- Polarity lnversion:极性翻转,PCIE链路中的高速差分对支持对内P/N翻转,需注意PCIE协议对该功能是做了强制要求的。

- bit Lock:位锁定,在链路训练开始前,RX端的PLL还未与TX端的发送时钟同步,会导致RX端无法对TX端发送过来的bit进行区分识别,而在链路训练过程中,RX端的PLL与发送时钟已完成同步(CDR功能),RX端将能识别到TX端发送的bit内容。

- Symbol Lock:符号锁定,在链路训练之前,RX端无法识别10bit组成的字符内容,在链路训练过程中,RX端能够找到COM符号,并使用COM符号来完成初始化,完成符号锁定(由于协议本身定义的是10bit数据所组成的符号,所以只适用于PCIE Gen1和PCIE Gen2)。

- Link Data Rate:链路数据速率,在链路训练开始时以默认的2.5Gbit/s速率进行,如果Link两端的设备都支持更高的速率,则会自动进入Re-training状态,以重新切换速率。

- Lane-to-Lane De-skew:通道对齐,当采用多lane进行数据传输时,由于每条lane的长度以及TX和RX的特性差异,可能会导致数据无法同一时间到达RX端,如果RX端不做任何处理会导致这部分数据上传到链路层导致数据出错。

2.2、LTSSM状态机

- 链路训练状态(Link Traing States):如上图所示正常的PCIE设备建链过程的流程依次为Detect–>polling–>Configuration–>L0(红色虚线选中部分)。

- 再训练状态(Link Re-Training State):也就是Recovery,此状态从L0状态进入,原因是出现错误(如电源状态、速率变化等),导致Link无法操作。当Link在转换到L0状态之前需要重新训练时,也从L1状态进入恢复。恢复中,重新建立位锁和符号锁的方式类似于在轮询状态。但是,与Link Traing States相比,过渡到该状态所需的时间要短得多。

- 电源状态相关(Power Mngt States):PCIE协议定义了关于电源状态的管理,分为两种,一种为PCI-PM软件管理电源机制(Power Management states),即软件可通过配置寄存器来实现电源状态管理,主要分为D0、D1、D2、D3这4种状态,其中D0为正常运行状态消耗的功率最大,D1和D2是中间省电状态,D3hot是低功率状态,D3cold是断电状态。Power Mngt States主要实现功能为电源切换,即如何从全速运行切入低功耗或从低功耗进入正常工作。例如,链路从L0转换到一个较低的电源管理状态,如L1或L2。

- 电源状态相关(Active Power Management):即为PCIE协议定义的另外一种电源状态管理,基于硬件层面的自主控制链路电源状态管理机制(ASPM),如果在链路上没有数据包传输(即,如果逻辑空闲序列被传输)并且发生超时,则设备可以将其链路置于低功率状态,例L0、L1。

- Other States:其他状态,例如Disabled、loop back、Hot Resst等。

LTSSM状态机中共有11种状态,对于这11种状态所完成的功能描述如下所示:

- Detect(检测):Detect作为PCIE链路训练的第1个环节,主要完成TX端检测RX端是否存在以及RX端能否正常工作等功能,如果检测通过则会进入下个状态。协议规定,Detect作为上电时的初始状态,在基本复位或热复位完成后,必须在80ms内进入Detect。Detect分为两种子状态,Detect Quiet和Detect.Active。Detect Quiet:当设备从其他状态或Reset状态进入Detect后,TX端处于电气空闲状态(Electrical Idle),在Detect Quiet状态下PCIE默认为2.5GT/s,同时TX端数据链路层Link up为0,即整个链路处于静止状态,当PCIE设备在12ms或者有lane退出Electrical Idle模式后,链路会进入Detect.Active状态,在这个状态就会开启检测RX工作。Detect.Active:在这个状态完成在位检测(During Detect.Active)的功能,用于检测RX端是否连接到链路通道上。如果未检测到RX端设备则会进入Detect Quiet状态。

- 检测原理:对于Detect检测RX端设备是否存在的原理较为简单,利用RC端充放电的时间来判断,详细判断过程如下图所示,当RX断设备未连接时,由于C较小,所以RC充电时间较短,而当RX端设备连接时,由于Ctx电容的接入,会导致RC充电时间较长,通过RC时间的长短来判断是否有RX端设备接入(也是PCIE接口串接电容靠近TX端摆放的原因)。

- Polling(轮询):在轮询的状态期间主要完成位锁定(bit lock)、符号锁定(Symbol Lock)、链路速率协商(Link Data Rate)、通道极性反转(Lane Polarity)等功能。在Polling的状态下主要包含Polling. Active、Polling. Compliance、Polling. Configuration、Polling. Speed等4个子状态。

- Polling. Active:当PCIE设备完成检测(Detect)后,会进入轮询状态(Polling),在Polling.Active状态下,PCIE所有的lane至少会传输1024个连续的TS1有序集,由于TX端和RX端可能不同一时间退出Detect状态,因此设备间的TS1有序集交流可能存在不同步的情况,协议规定链路完成1024个TS1有序集的至少需要64us的时间来完成bit lock、Symbol lock的动作。

- Polling. Configuration:此过程主要完成链路通道反转的动作,当发送端TX发送完至少1024个TS1并且接收端RX连续收到8个TS1或者TS2,此时TS1和TS2中的Link/Lane区域由PAD填充,那么,链路进入Polling.Configuration状态。处于此状态,发送端停止发送TS1序列,改为发送TS2序列,此时Link/Lane区域仍然由PAD填充,这个过程也会完成极性反转的问题,为进入下一个状态作准备。

- Polling. Compliance:Compliance 此状态用于测试。发送方会发送特定的码字组合(pattern),构建一种码间干扰和串扰接近最严重的场景,用于链路信号质量分析。在该次状态中,可以发送两类码字,分别是 Compliance pattern 和 modified compliance pattern。

- Polling. Speed:在此状态下,所有通道的数据速率都被更改为链路两端所支持的最大速率。

- Configuration(配置):在该状态中,PCIe设备会依次发送TS1有序集和TS2有序集实现以下目标:

- 确定链路宽度(Link Width)

- 链路编号(Link Number)

- 通道位置翻转(Lane Reversal)

- 通道对齐(Lane-to-Lane De-skew)

在Configuration状态下,发送端和接收端已经确认可以正常通信。

- L0:这是链路的正常、完全活动状态,在此期间可以发送和接收TLP、DLLP和PLP。

- Recovery(恢复):当PCIe链路需要重新训练时,进入Recovery状态。主要有以下几种情况:

- PCIe链路信号发现error,需要调整Bit Lock和Symbol Lock。

- 从L0s或者L1低功耗电源状态退出。

- Speed Change。因为第一次进入L0状态时,速率是2.5GT/s. 当需要进行速率调整5.0GT/s或者8.0GT/s时,需要进入Recovery状态进行Speed Change这个阶段,Bit Lock、Symbol Lock等都需要重新获取。

- 需要重新调整PCIe链路的Width。

- 软件触发retrain操作。

- 仅在Gen3、Gen4和Gen5,需要重新进行Equalization。

- L0s:该状态主要用于降低设备功耗,在总线空闲的时候可以进入该状态,且从该状态可以迅速地重新切换回L0状态。当PCIe设备发现链路空闲时,可以主动进入L0s状态,PCIe设备进入或退出该状态不需要系统软件干预(通过ASPM机制实现)

- L1:相对于L0s状态,L1状态下的功耗更低。但进入和退出L0状态时间更长。

- 由ASPM(电源管理技术)引导,通常来讲可由硬件设备自主协商完成。即当发送端发现链路上长时间没有TLP或者DLLP时,便通过ASPM建议接收端进入L1状态。如果接收端允许进入,则链路进入L1状态;如果接收端不允许进入,则链路进入L0s状态。

- 由软件引导,软件发送一系列的命令让链路进入低功耗状态(D1,D2,or D3hot )。随后,链路的上端设备会通知下端设备进入L1状态,收到来自下端设备的应答后,链路进入L1状态,设备会自动将其Link置于L1状态。

- L2:这是最低功率状态。大部分发射器和接收器逻辑被关断(接收器端接除外,它必须被供电以使接收器处于低阻抗状态)。主要的电源和时钟不能保证,但Vaux电源可用(辅助电源(Vaux)保持设备供电的有限部分,包括唤醒信令逻辑)。当相关系统或外形规格要求Beacon支持时,支持这种唤醒功能的上游端口必须能够发送Beacon信号,下游端口必须能够检测Beacon信号。处于D3Cold状态的设备,需要Beacon信号或者WAKE#边带信号来唤醒系统。其中Beacon信号是一种低频信号(通常为1Hz)

- Hot Reset (热复位):热复位通常用于需要对 PCIe 设备进行重置而又不能中断系统运行的情况。在进行热复位时,PCIe 主机系统向目标设备发送复位信号,以将其重置为初始状态。与冷启动不同,热复位过程不会影响系统中的其他设备或总线通信,因此系统的运行不会中断。相比冷启动,热复位只会对目标设备执行重置操作,而冷启动通常需要重新初始化整个 PCIe 总线和相关设备,所以热复位比冷重启更为快速。

- Loopback (回环测试):Loopback 是一种用于测试和诊断 PCIe 总线连接的技术。通过配置 PCIe 设备为 Loopback 模式,可以将发送到设备的数据通过 PCIe 总线回环到设备的接收端口,从而实现自我测试或诊断,可以通过软件或硬件的方式来实现(处于此状态时,Loopback主机将有效的8b/10b编码符号发送到Loopback从机)

- Disable:是指禁用 PCIe 设备或功能的操作(不需要DC共模电压)。在此状态下,TX端处于电高阻抗状态,RX端被启用并处于低阻抗状态。软件通过设置链路控制寄存器中的禁用位命令设备进入禁用状态。然后,该设备发送16 TS1排序集与禁用链路位设置TS1训练控制字段。连接的接收器在接收到设置了禁用链路位的TS1 Ordered-Set时被禁用。一般来讲,进入Disable的原因是由于PCIE设备发生硬件故障(插拔、过热等)或数据错误时,为防止对系统进一步影响而将其链路进行禁用。

3、PCIE误码排查

- 二分法降低 Lane 宽度,比如x16的 Port ,可以保留高8 Lane 或者低8 Lane运行,判断误码在哪个x8,然后再依次减小到x4等。

- 使用内部眼图,查看哪个 lane 眼图异常。

- 排查各 Lane TX 、 RX 参数,看是否有异常。

- 排查时钟抖动是否太大。

- PCB 设计,比如 Fiber wave 效应、忘记背钻导致过孔 Stub 太大、阻抗波动大、板材用料错误、设计裕量不足、连接器接触问题、连接器 De-mating 太大等原因。

2、如果降速依然导致误码发生,应该考虑电源、时钟、复位的影响。

- 时钟架构非同源+芯片不支持 SRIS 、 SRNS 。

- 如果展频打开可以关闭展频确认误码情况。

- 复位时序或者复位脉宽不够。

五、JESD204B

1、链路同步介绍

- 子类0使用器件时钟、通道和SYNC。

- 子类1使用器件时钟、通道、SYNC和SYSREF。

- 子类2使用器件时钟、通道和SYNC。

2、同步步骤

- CGS代码组同步阶段

- 接收器拉低SYNC信号,发出同步请求。

- 收发器从下一个符号开始,发送未加扰的/K28.5/符号(每个符号10位)。

- 当接收器收到至少4个无错误的连续/K28.5/符号时同步,然后将SYNC~引脚拉高。CGS阶段结束,ILAS阶段开始。

接收器必须接收到至少4个无错误8B/10B字符,否则同步将失败,链路留在CGS阶段。

- ILAS通道同步阶段

- 多帧1:以/R/字符[K28.0]开始,以/A/字符[K28.3]结束。

- 多帧2:以/R/字符开始,后接/Q/ [K28.4]字符,然后是14个配置8位字的链路配置参数,最后以/A/字符结束。

- 多帧3:与多帧1相同。

- 多帧4:与多帧1相同。

3. 数据传输阶段

在数据传输阶段,通过控制字符监控帧对齐。发射器和接收器各自保持一个本地多帧计数器(LMFC),它持续计数到(F × K) − 1,然后绕回到”0″重新开始计数。向所有发送器和接收器发送一个公共(源)SYSREF,这些器件利用SYSREF复位其LMFC,这样所有LMFC应互相同步。

数据在下一个LMFC之前从发射器的SERDES传播出去。接收器将把数据送入FIFO,然后 在下一个(Rx) LMFC边界开始输出数据。发射器的SERDES输入和接收器FIFO输出之间的这种已知关系称为确定性延迟。

3、常见问题

- SYSREF和SYNC信号应直流耦合。

- 在电路板未上电的情况下,检查从SYNC源(通常来自FPGA或DAC)到SYNC输入(通常是ADC或FPGA)连接是否良好且具有低阻抗。

- 陷入CGS模式:SYNC没有拉高,保持逻辑低电平;可能是所发送的数据有问题,或者JESD204B接收器未对样本进行正确解码。

- ILAS阶段:脉冲高电平持续时间少于4个多帧。

- 确认SYNC源和接收器件逻辑电平是否匹配。

附:各类接口电平标准介绍

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/117363.html