大家好,欢迎来到IT知识分享网。

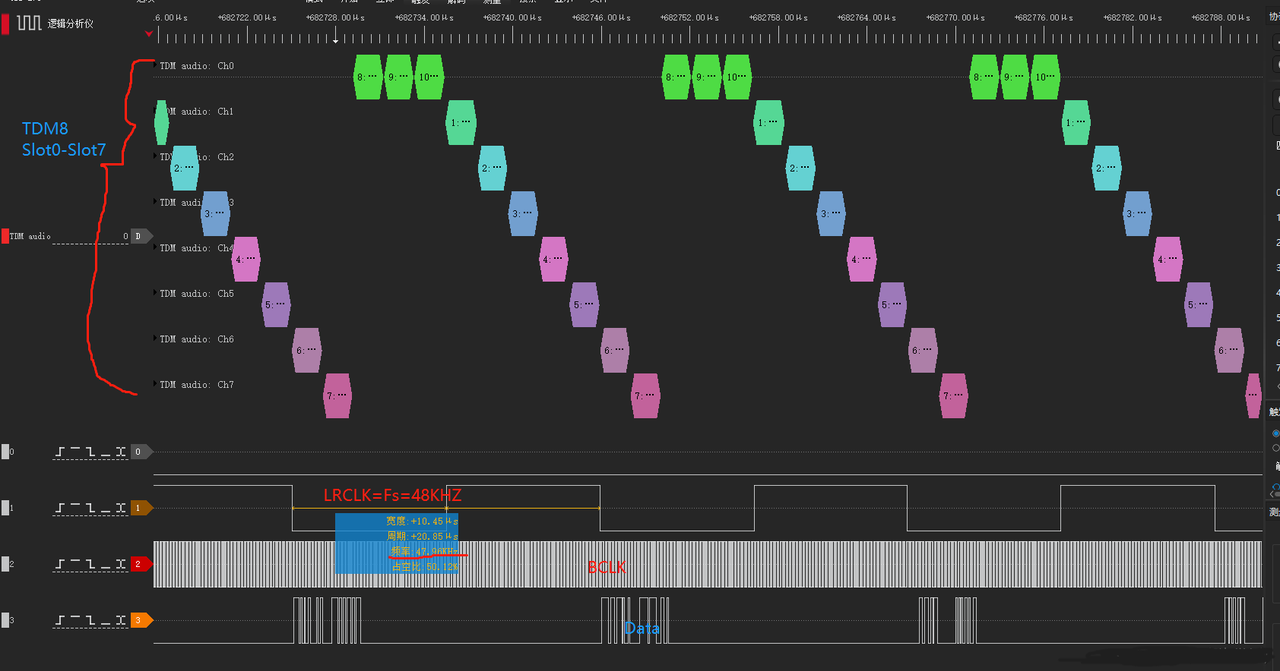

一、I2C

1.1 I2C总线的构成,主设备、从设备连接方式

I2C通讯协议(Inter – Integrated Cricuit)是由Phiilps公司开发的,由于它引脚少,硬件实现简单, 可扩展性强,不需要USART、CAN等通讯协议的外部收发设备。

- 两根通信线:SCL(Serial Clock)、SDA(Serial Data)

- 同步,半双工

- 带数据应答

- 两种模式:标准模式——100KHz,高速模式——400KHz

- 支持总线挂在多设备(一主多从、多主多从——会进行仲裁)

硬件电路 - 所有I2C设备的SCL连在一起,SDA连在一起

- 设备的SCL和SDA均要配置成开漏输出模式但是不一定是4.7KΩ

- SCL和SDA各添加一个上拉电阻,阻值一般在4.7KΩ左右,

(为什么要加上拉电阻可以参考下方链接)

https://baijiahao.baidu.com/s?id=&wfr=spider&for=pc

不一定是4.7KΩ

(空闲状态,SDA的控制权在主机;只有在主机发送读取从机的命令后,或者从机应答的时候,从机才能短暂地取得SDA的控制权—— 一主多从)

- 怎么确认选择的从机?——地址

I2C没有像SPI那样的从机选择线,因此它需要另一种方法让器件知道数据正在发送给它,而不是另一个从器件。它通过地址来做到这一点。地址帧始终是新消息中起始位之后的第一帧。主设备将其通信的地址发送给连接的每个从设备。然后从设备将从主设备发送的地址与其自己的地址进行比较。如果地址匹配,则将低电压ACK位发送回主机。如果地址不匹配,则从器件不执行任何操作,SDA线保持高电平。

1. 2 I2C总线Start、Stop信号

static void SetSCL_High(void) {

GPIO_SetBits(GPIOx, GPIO_Pin_X); Delay(xus); } static void SetSDA_High(void) {

GPIO_SetBits(GPIOx, GPIO_Pin_x); Delay(xus); } static void SetSCL_Low(void) {

GPIO_ResetBits(GPIOx, GPIO_Pin_x); Delay(xus); } static void SetSDA_Low(void) {

GPIO_ResetBits(GPIOx, GPIO_Pin_x); Delay(xus); } static void SetSCL_High(void) {

GPIO_SetBits(GPIOx, GPIO_Pin_X); Delay(xus); } static void SetSDA_High(void) {

GPIO_SetBits(GPIOx, GPIO_Pin_x); Delay(xus); } static void SetSCL_Low(void) {

GPIO_ResetBits(GPIOx, GPIO_Pin_x); Delay(xus); } static void SetSDA_Low(void) {

GPIO_ResetBits(GPIOx, GPIO_Pin_x); Delay(xus); } static void Start_I2C(void) {

SetSDA_High(); SetSCL_High(); SetSDA_Low(); SetSCL_Low(); } static void Stop_I2C(void) {

SetSDA_Low(); SetSCL_High(); SetSDA_High(); } 1.3 I2C读写时序,ACK,NACK

1.3.1 发送一个字节

static uint8_t ReadSDA(void) {

Delay(xus); return GPIO_ReadInputDataBit(GPIOx, GPIO_Pin_x); } static uint8_t I2C_SendByte(uint8_t Data) {

uint8_t ack; uint8_t count =8; ConfigSDA_Output(); while(count --) {

if(Data & 0x80) {

SetSDA_High(); } else {

SetSDA_Low(); } Data << 1; SetSCL_High(); SetSCL_Low(); } SetSDA_High(); ConfigSDA_Input(); SetSCL_High(); for (; ; ) {

if (ReadSDA() != 0) {

ack = 0; } else {

ack = 1; break; } Delay(xus); } SetSCL_Low(); ConfigSDA_Output(); return ack; } 1.3.2 接收一个字节

static uint8_t I2C_RecvByte(void) {

uint8_t Data; uint8_t count = 0; SetSDA_High(); SetSCL_Low(); ConfigSDA_Input(); while (count --) {

SetSCL_Low(); SetSCL_High(); Data << 1; if (Read_SDA()) {

Data |= 1; } } SetSCL_Low(); return Data; } 1.3.3 发送/接收应答(ACK/NACK)

static void Ack_I2C(void) {

SetSDA_High(); ConfigSDA_Output(); if (Ack == 0) {

SetSDA_Low(); } else {

SetSDA_High(); } SetSCL_High(); SetSCL_Low(); } 1.4 I2C Clock Stretching

https://www.i2c-bus.org/clock-stretching/

Clock Stretching

二、SPI

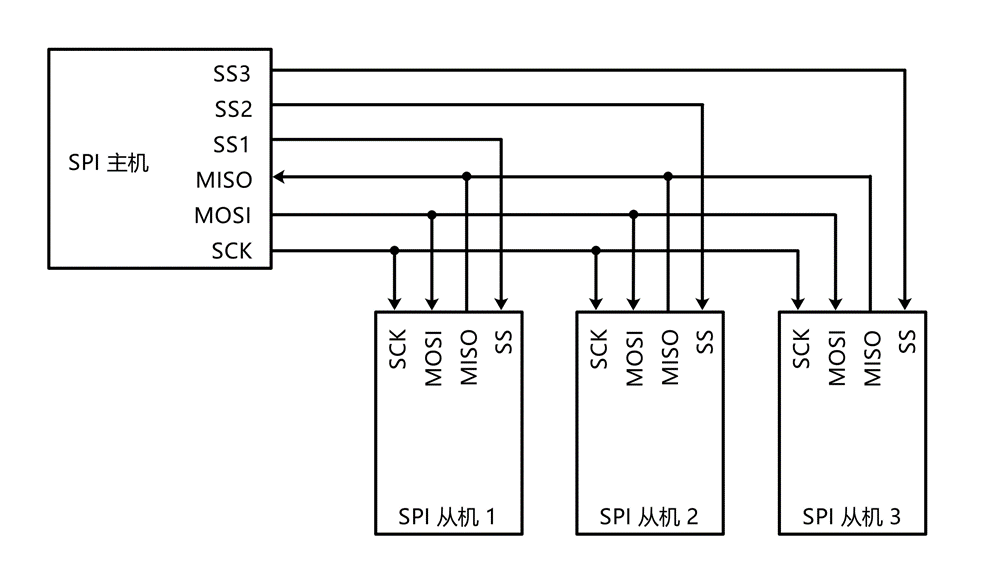

2.1 SPI总线构成,主设备、从设备连接方式

- SPI(Serial Peripheral Interface)是由Motorola公司开发的一种通用数据总线。和I2C都是用于主控和外挂芯片之间的通信。

- 四根通讯线:

SCK——Serial Clock,有的地方可能叫做SCLK、CLK、CK

MOSI——Master Output Slave Input,(DO——Data Output)

MISO——Master Input Slave Output,(DI——Data Input)

SS——Slave Select,(NSS——No Slave Select / CS——Chip Select) - 同步,全双工(数据发送和数据接收单独各占一条线)

- 支持总线挂载多设备(一主多从)

硬件电路: - 所有SPI设备的SCK、MOSI、MISO分别连接在一起

- 主机另外引出多条SS控制线,分别接到各从机的SS引脚

- 输出引脚配置为推挽输出,输入引脚配置为浮空或者上拉输出

推挽输出,高低电平均有很强的驱动能力,可以使得SPI引脚信号的下降沿,非常迅速,上升沿,也非常迅速。

当从机的SS引脚为高电平,也就是从机未被选中时,它的MISO引脚,必须切换为高阻态,高阻态就相当于引脚断开,不输出任何电平,这样就可以防止,一条线多个输出,而导致的电平冲突的问题了。在SS为低电平时,MISO才允许变为推挽输出

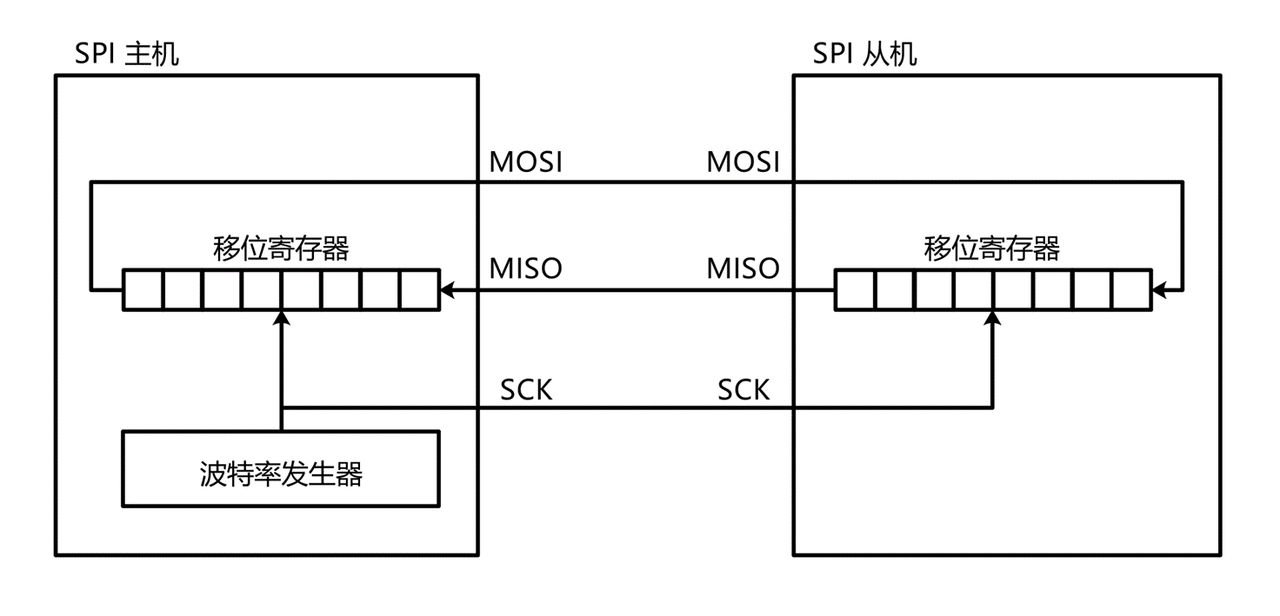

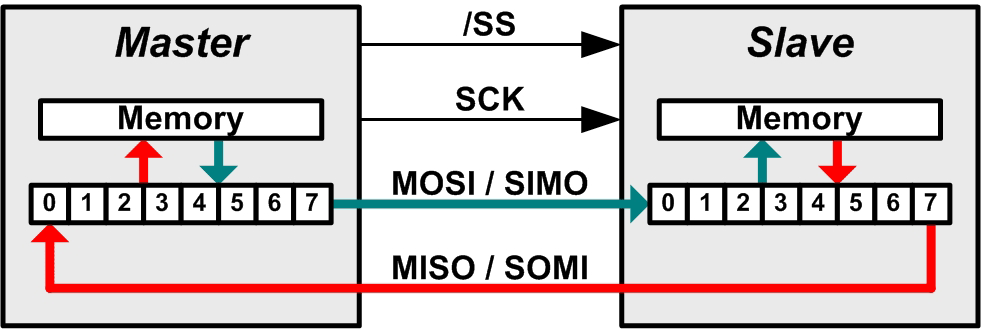

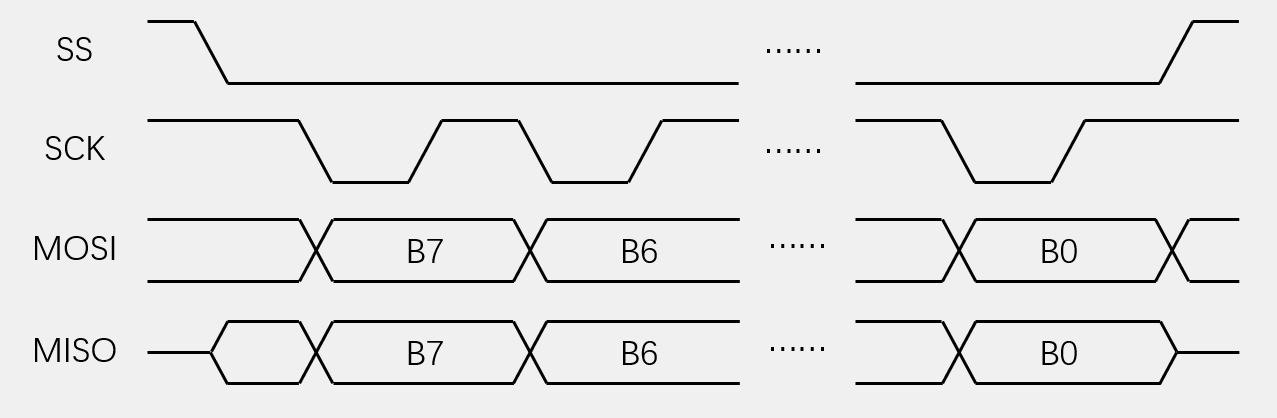

移位示意图:

SPI的数据收发,都是基于字节交换,这个基本单元来进行的。当主机需要发送一个字节,并且同时需要接收一个字节时,就可以执行一下字节交换的时序。这样,主机要发送的数据跑到从机,主机要从从机接收的数据,跑到主机。SPI通信的基础是交换一个字节。实现三种功能。

2.2 SPI总线Start、Stop信号

static void Start_SPI(void) {

GPIO_WriteBit(GPIOx, GPIO_Pin_x, 0); //The speed of SPI is very fast, so there is no need for a delay after the pin is operated } static void Stop_SPI(void) {

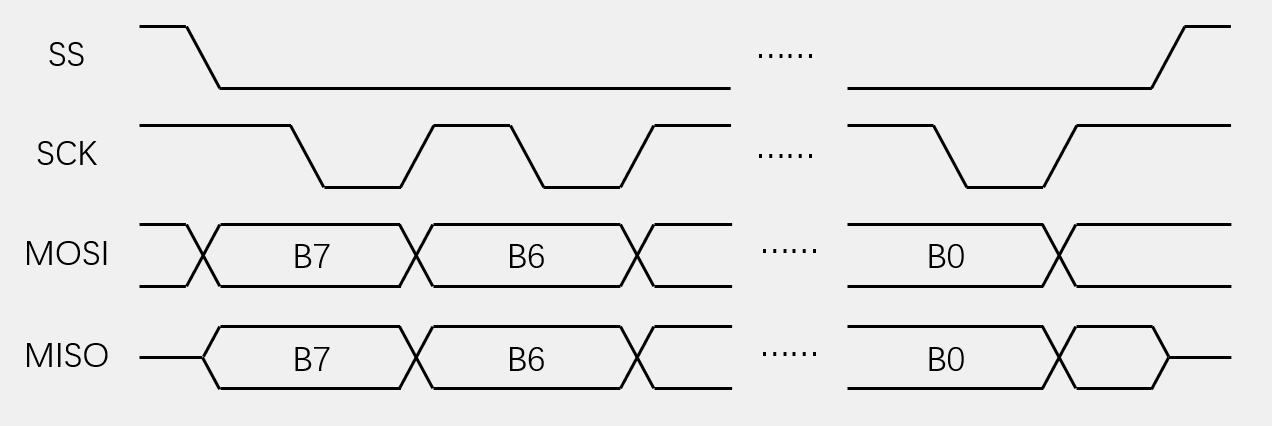

GPIO_WriteBit(GPIOx, GPIO_Pin_x, 1); //The speed of SPI is very fast, so there is no need for a delay after the pin is operated } 2.3 SPI总线速度、字长、CPOL、CPHA、MSBF、LSBF

交换一个字节(模式3)

CPOL = 1 : 空闲状态时,SCK高电平

CPHA = 1 : SCK第一个边沿移出数据,第二个边沿移入数据

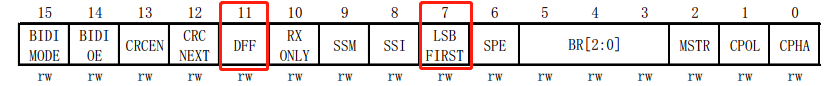

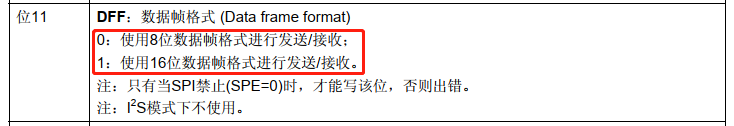

④数据帧格式:(8位或16位)

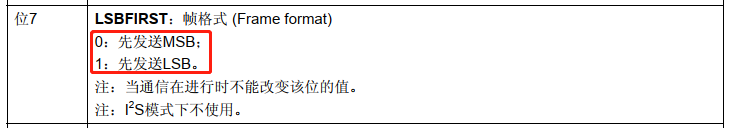

LSBF——Least Significant Bit First 和 MSBF——Most Significant Bit First

根据SPI_CR1寄存器中的LSBFIRST位,输出数据位时可以MSB在先也可以LSB在先。

2.4 SPI 单工、半双工、全双工

三、I2S

I2S——Inter-IC Sound,Integrated Interchip Sound,又称集成电路内置音频总线,是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准。采用了独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真。

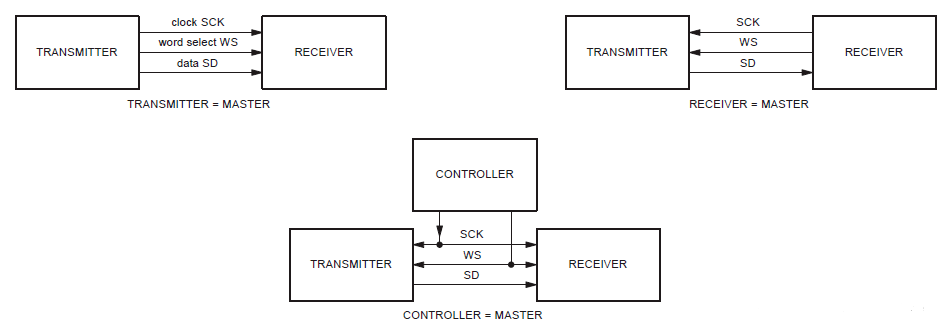

3.1 I2S总线构成和连接方式

- 支持全双工和半双工模式;支持主、从模式;

- I2S总线一般由1根系统时钟线和3根信号线组成:

MCLK:称为主时钟,也叫系统时钟(Sys Clock),一般为了使系统间能够更好地同步时增加MCLK。

SCLK(BCLK):串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1一个脉冲。

LRCK:帧时钟LRCK,也称(WS),用于切换左右声道的数据。

SDATA(SD):就是用二进制补码表示的音频数据。最高位拥有固定的位置,而最低位的位置则是依赖于数据的有效位。

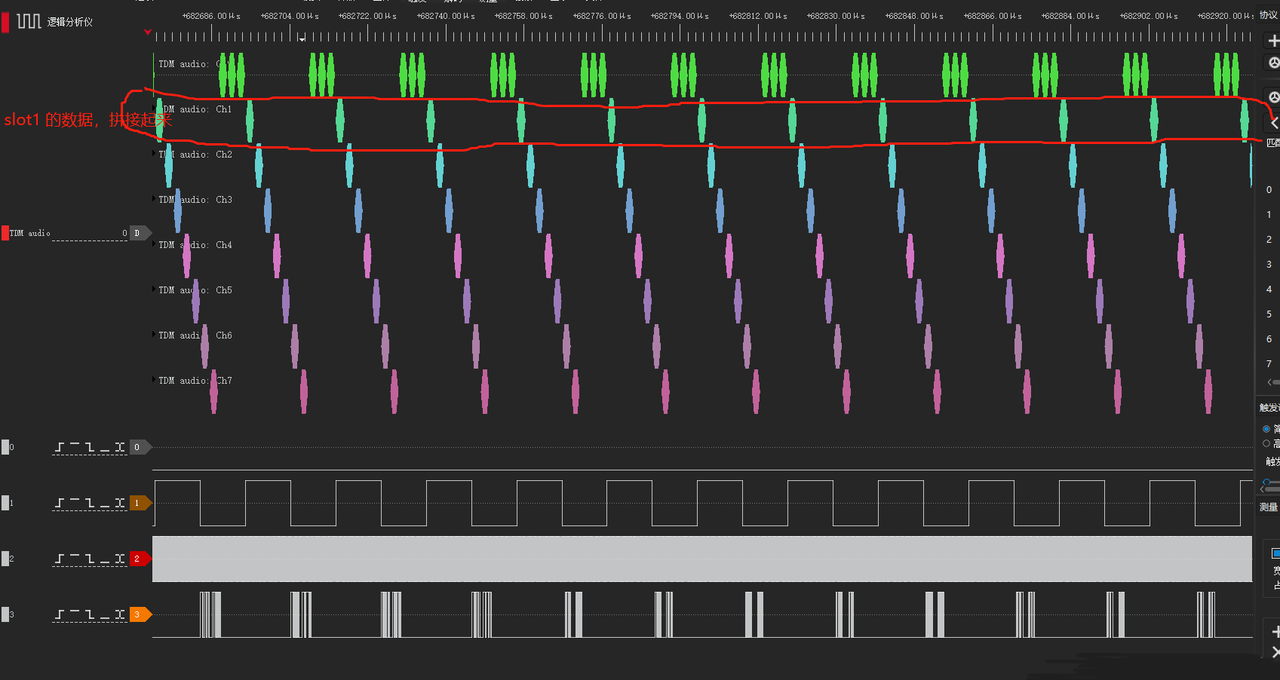

3.2 采样率,LRCK、BCLK、MCLK频率对应关系

- 采样:

就是间隔一定得时间对模拟信号做一个取样。比如间隔0.001秒采一个样,这样采样频率(Fs)就是:

Fs = 1 / 0.001 = 1KHz

要多大采样率才可以还原一个模拟信号,这个涉及到数字信号处理原理(奈奎斯特定理)。采样频率Fs大于信号中最高频率fmax 的2倍时(Fs > 2fmax ),采样之后的数字信号完整地保留了原始信号中的信息。

人耳听到的音频范围是20Hz~20KHz,如果对人耳听力范围内的音频数字化,fmax = 20KHz,Fs > 40KHz的采样率44.1KHz就是高保真了。它能覆盖人耳听到的所有声音。 - MLCK:

主时钟(独立映射),在I2S配置为主模式,寄存器SPI_I2SPR的MCKOE位为“1”时,作为输出额外的时钟信号引脚使用。输出时钟信号的频率预先设置为256 × Fs,其中Fs是音频信号的采样频率。

MCLK的频率 = 128或者256或者512 * 采样频率 - SCLK:

SCLK的频率 = 声道数 * 采样频率 * 采样位数 - LRCK:

LRCK的频率 = 采样频率

3.3 I2S、左对齐、右对齐的含义

3.3.1 I2S Philips标准

3.3.2 左对齐——Left Justified Standard

3.3.3 右对齐——Right Justified Standard

3.4 I2S字长,发送端和接收端怎么样截取数据

如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的地位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位(标准I2S格式)。

3.5 怎样确认左右声道

三种格式,具体见3.3

四、UART

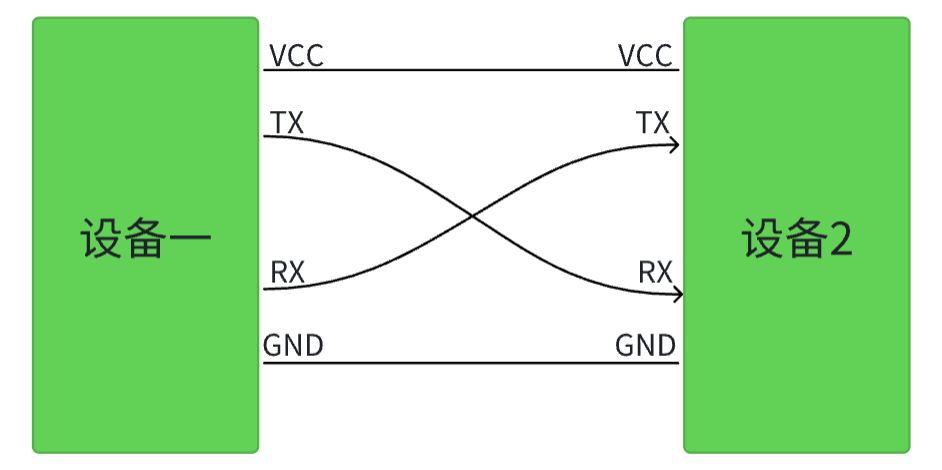

4.1 UART总线连接方式,TX/RX

- 简单双向串口通信有两根通信线(发送端TX和接收端RX)

- TX和RX要交叉连接

- 当只需单向传输数据时,可以只接一根通信线

- 电平标准不一致时,需要加电平转接芯片

4.2 UART怎么样表达0/1,RS232、RS485和UART的区别

4.2.1 UART表达0/1

4.2.2 RS232、RS485、UART的区别

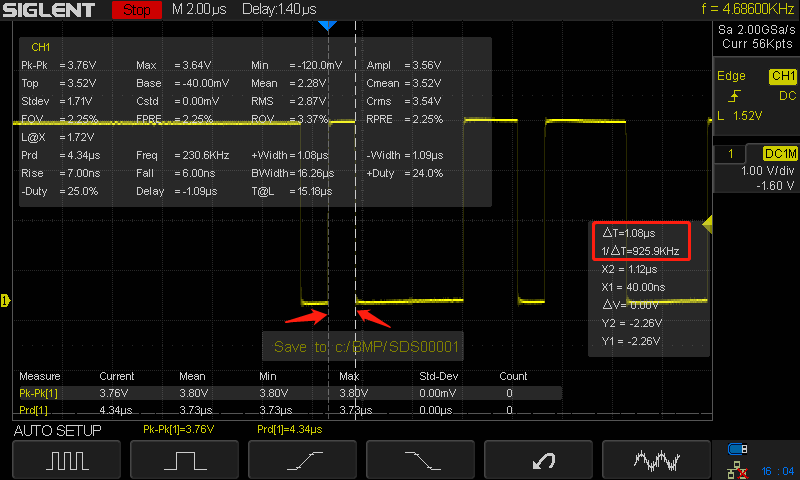

UART是通用异步收发传输器,它是完成一个特定的功能的硬件,它本身不是协议、它的最基本功能,是串行数据和并行数据之间的转换。计算机中的数据以Byte为基本单位,对一个Byte的存取是并行的,即同时取得/写入8个bit。而串行通信,则需要将这个Byte“打碎”,按照时间顺序来收发以实现串行。它是设备间进行异步通信的关键模块,UART负责处理数据总线和串行口之间的串/并、并/串转换,并规定了帧格式;通信双方只要采用相同的帧格式和波特率,就能在未共享时钟信号的情况下,仅用两根信号线(Rx和Tx)就可以完成通信过程,因此也称为异步串行通信。 4.3 怎样从波形上分析波特率

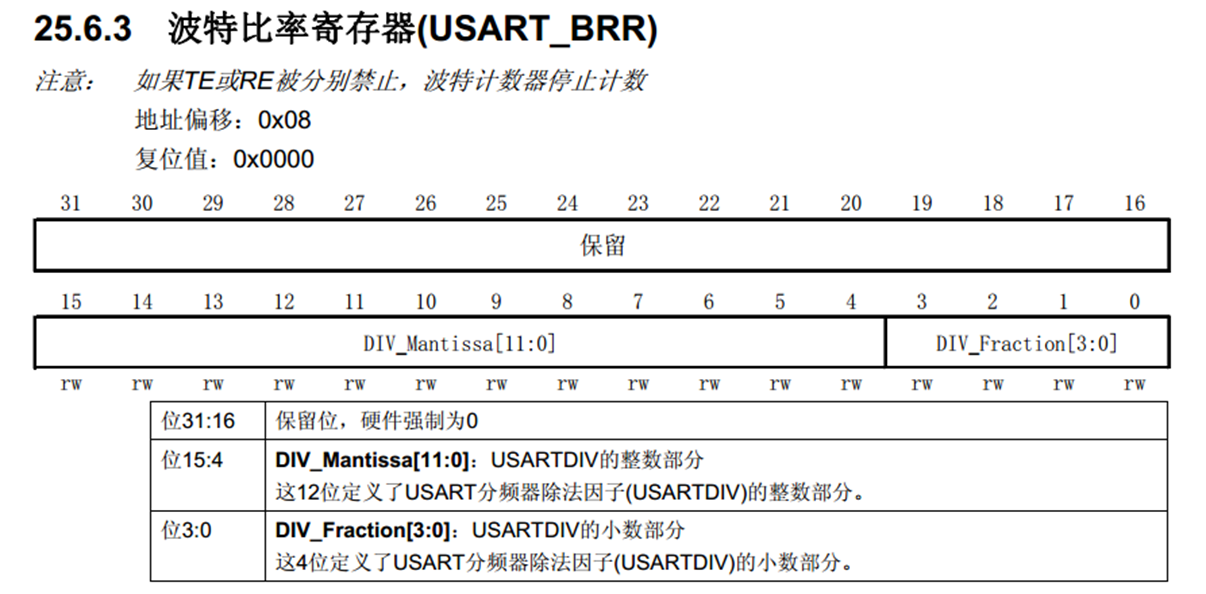

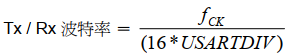

发送器和接收器的波特率由波特率寄存器BRR里的DIV确定

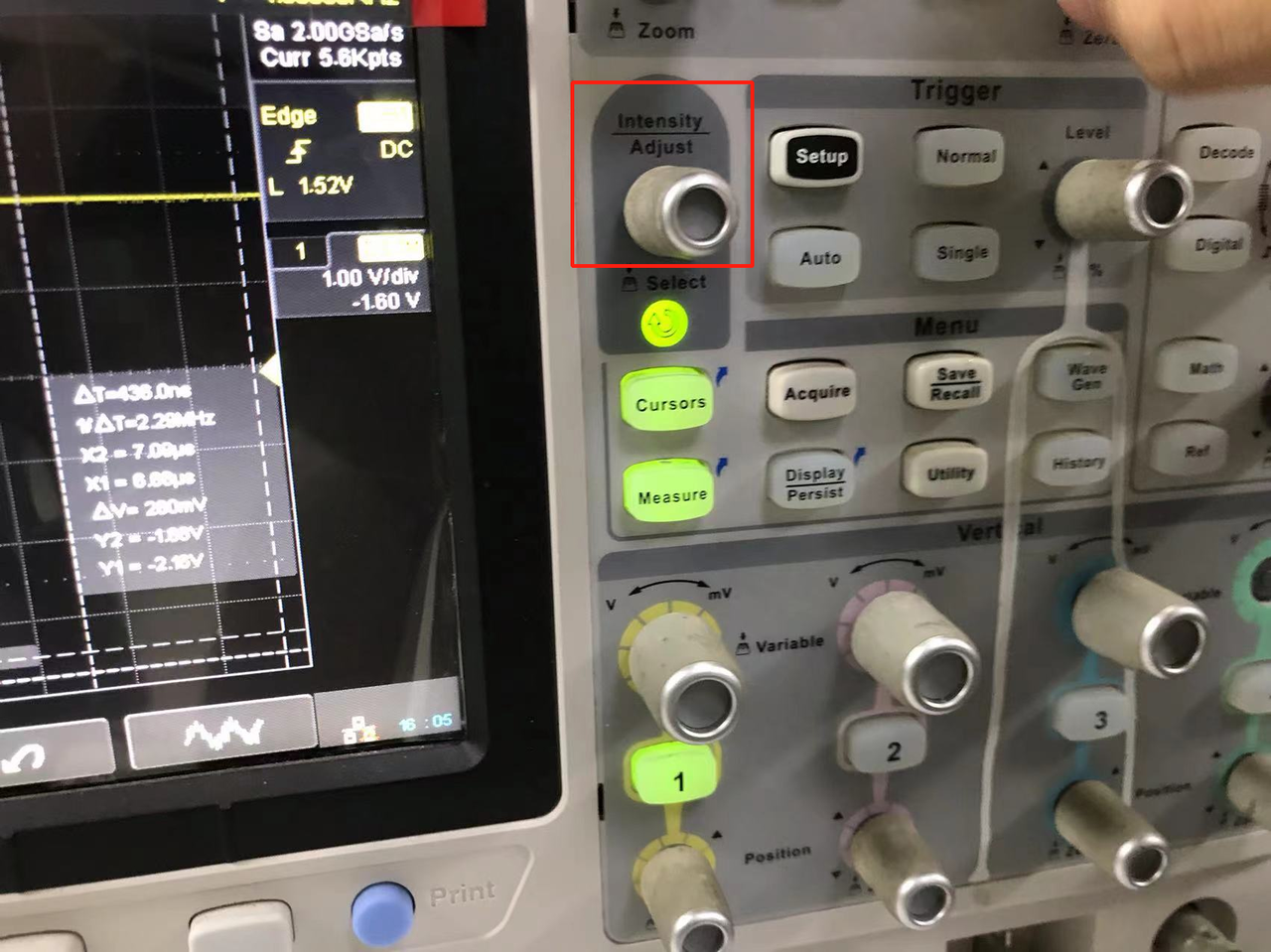

- 通过示波器调节X1,X2的位置,使△X的大小正好等于一个脉冲

计算 f = 1 / △T

波特率的计算: = f(PCLK2/1) / (16 * DIV)

如何从USART_BRR寄存器值得到USARTDIV:

例1:

如果DIV_Mantissa = 27,DIV_Fraction = 12(USART_BRR = 0x1BC——0001,1011,1100)

于是,

Mantissa(USARTDIV) = 27

Fraction(USARTDIV)= 0.75

所以,USARTDIV = 27.75

4.4 CTS/RTS,XON/XOFF工作原理

4.4.1 CTS/RTS

4.4.2 XON/XOFF工作原理

4.5 UART发送一个字节的完整波形,字长、停止位、奇偶检验位

4.5.1串口参数及时序

4.5.2 USART特性描述

4.5.3 奇偶检验

4.6 UART误差频率的考量

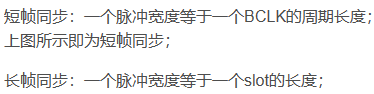

五、TDM——Time Division Multiplexing,时分复用

5.1 TDM总线组成和连接方式

5.2 SLOT

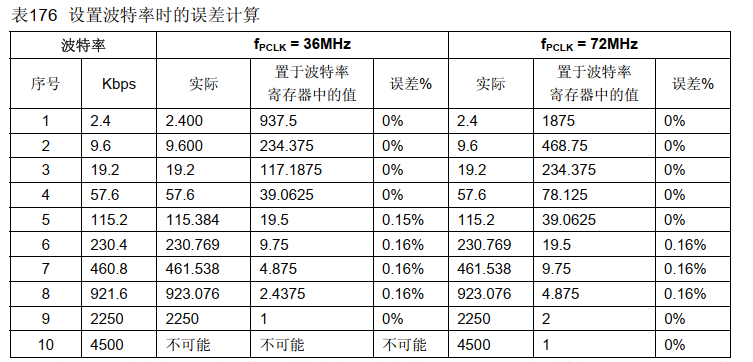

5.4 MODE A / MODE B

由于没有统一标准,不同厂商对FSYNC脉冲宽度及触发边沿的设置可能不同。如上图:

短帧模式,帧同步时钟宽度为一个位时钟周期,数据在FSYNC有效后,BCLK的第二个上升沿有效;

长帧模式,帧同步时钟宽度为两个位时钟周期,数据在FSYNC有效后,BCLK的第一个上升沿有效;

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/117789.html

![常见机内总线——I2C、SPI、I2S、UART、TDM插图3 [图片]](https://i-blog.csdnimg.cn/blog_migrate/9288617759126a4a50a994ea4c35096e.png)

![常见机内总线——I2C、SPI、I2S、UART、TDM插图5 [图片]](https://i-blog.csdnimg.cn/blog_migrate/1b8744798f9f12e0e10190f7c574e031.png)

![常见机内总线——I2C、SPI、I2S、UART、TDM插图7 [图片]](https://i-blog.csdnimg.cn/blog_migrate/3875bd3f8a25e6499ce6d2d2f4a5e9dc.png)