大家好,欢迎来到IT知识分享网。

1.什么是PERST#

PERST#作为 Fundamental Reset,是直接通过边带信号PERST#(PCI Express Reset)产生的。Fundamental Reset会复位整个PCIe设备,初始化所有与状态机相关的硬件逻辑,端口状态以及配置空间中的配置寄存器等(every state machine and all the hardware logic, port states and configuration registers)。但是,也有一个例外,就是属性为“Sticky“配置寄存器字段。此类寄存器在辅助电源Vaux存在时,不受Fundamental Reset影响。但是如果主电源和Vaux都被移除,则也会被重置。“Sticky“配置寄存器字段对于诊断“problems that require a reset to get a Link working again”很有用。

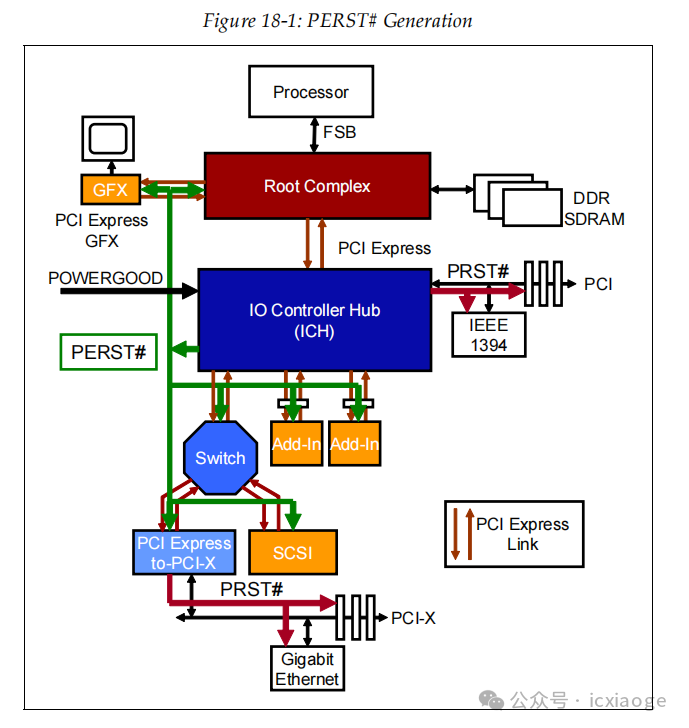

如图18-1所示,IO控制器中心(ICH)芯片可以根据系统电源信号“POWERGOOD”的状态产生PERST#,因为这表明主电源已打开且稳定。主机上电时和下电时,信号POWERGOOD的跳变会导致PERST# 复位和复位释放。如图所示,PERST#能够控制图中的多种设备,例如PCIE Switch、PCI Express to-PCI-X bridge,以及Add-In Card(Endpoint设备,常见设备类型有网卡和声卡)。

2.PERST#如何作用到EP设备

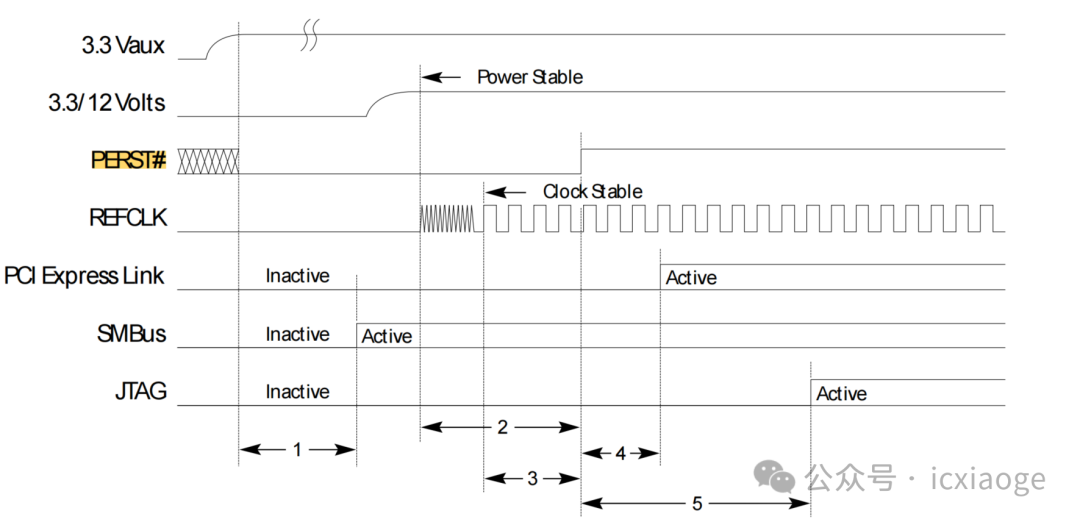

图2:PERST复位时序图

如图2所示为PERST#信号在主机上电时的时序图,初始状态(主机未上电)PERST#置为不定态(正常为0),一旦主机上电,马上PERST#置为0产生复位,保持一段时间(若干秒)后PERST#置为1表示复位撤销。不同主机上电时对PERST#信号的处理略有差异,有些主机存在两次PERST#复位。

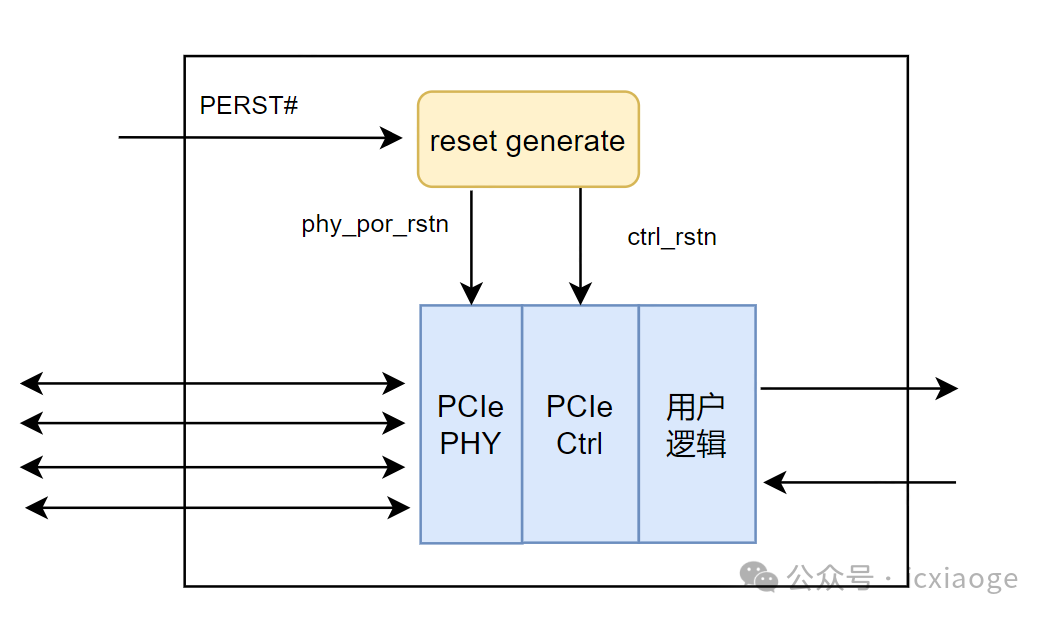

对PCIe Endpoint设备来说,PERST#信号来自PCIe卡槽,通过金手指传递到Add-In Card中的PCIe逻辑。如图3所示,当PERST#为0时,会通过复位产生逻辑(reset generate)产生phy_por_rstn和ctrl_rstn,phy_por_rstn用于复位PHY模块,ctrl_rstn用于复位controller模块。

需要注意的是,在主流的PCIe上电流程中,PCIe PHY需要加载firmware,为保证firmware加载正常进行会屏蔽PERST#,firmware加载完成后会解除PERST#屏蔽,并且后续的PERST#复位不会导致firmware二次加载(只要设备不断电)。

图3:PERST#作为范围

3.如何处理PERST#

作为EP设备,收到PERST#复位需要将PCIe寄存器和状态进行复位,在复位释放后重新进行PCIe链路训练,那么此时Add-In Card中除了PCIE之外的其他模块改怎么处理呢?也需要进行复位吗?

Add-In Card是否随着PERST#复位而进行整体复位需要根据芯片的应用场景进行选择。通常为了保证能够满足各类要求,至少要保证能够做到如下场景:

1)仅复位PCIE,其他模块不复位,PCIe链路协商成功后能够进行通信

2)复位PCIE以及耦合紧密的模块,其他模块不复位,,PCIe链路协商成功后能够进行通信

3)整个芯片均复位

以上3种处理方式可以根据配置进行选择。

4.参考文档

MindShare PCI Express Technology 3.0

PCI Express Base Specification Revision 5.0, Version 1.0

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/119491.html