大家好,欢迎来到IT知识分享网。

目录

前言

一个新东西来的时候,人们总是希望能够宏观的定性的认识它。一个问题是,手机上用的“软件”该如何定义呢?来自百度百科的定义是,软件是指一系列按照特定顺序组织的计算机数据和指令的集合,如果你是非专业人员,第一次听说“软件”并听到这样的定义应该不会有好的感知。另外一种回答是,类似手机里“微信”的就是一个软件,虽然仍然不知道软件如何标准定义,但这个回答显然能让更容易的感知“软件”这个名词。生活中往往需要从另外一个事物A认识事物B,这个A可能和B存在某种关系,由于A很简单从而对B有了宏观的感知。生活如此,学习一个新的技术也是如此,或者说,学技术如此,生活也是如此。那该如何宏观感知LVDS呢?

1.介绍LVDS

LVDS的标准定义是Low-Voltage Diffferential Signaling低电压差分信号,为了克服以TTL电平方式传输宽带高码率数据时功耗大,电磁干扰大等缺点出现了LVDS技术,它具有低功耗、低误码率、低串扰和低辐射等特点。LVDS接口使用1.2V 偏置电压作为基准(共模直流电压),其正负端的摆幅大约为350mV,即所谓的差模电压。在网络上检索LVDS会出现各种说法,LVDS接口、LVDS电平、LVDS协议、LVDS技术,到底该如何理解呢?从电气标准的角度,LVDS是一种电平标准,其他常见的电平标准还有TTL、LVTTL、SSTL、LVCMOS、RS232、RS485等,不同电平标准有不同的场景应用。在Xilinx的FPGA中,支持这个电平标准,并且有LVDS_25\LVDS\LVDS33等,后续会介绍xilinx LVDS使用注意事项。从接口的角度看,LVDS可以称作接口,侠义的接口例如USB接口,千兆网口,麦克接口都是指某个物理硬件,可以连接起来。而广义的接口包括API、Sockets、弱函数、虚函数等软件上的接口,二者有一个共同的特点就是要在接口两端实现信息的传递,从这个意义上讲,LVDS是一个侠义的硬件接口。关于LVDS技术,这个说法主要是指LVDS接收器和收发器的硬件上的组成部分,大多数低速数字逻辑电平(如TTL、CMOS)是以电压对参考地的幅值来判断是高电平还是低电平, LVDS却完全不一样,它是通过数据接收器同相端与反相端的电压相对大小判断高低电平的,而不是通过同相端或反相端对公共地(GND)。通过恒流源和全桥开关电路不同晶体管的通断形成电压摆幅。关于LVDS协议,这种说法应该是不对的,通常协议是指规定两个或多个通信实体之间进行交换的报文格式和次序,LVDS并没有做这些规定。因此当设备与控制芯片(如FPGA)通过LVDS接口相连时,如何正确传输数据,这是控制芯片去适配设备接口属性的,这也是本篇要解决的问题,即实现FPGA上的LVDS与外部设备通信,实例中用到的外部设备也是FPGA。同样这也是LVDS的本质意义,即如何通过硬件电路LVDS接口实现通信。文末附本例源码。

2.LVDS传输模型

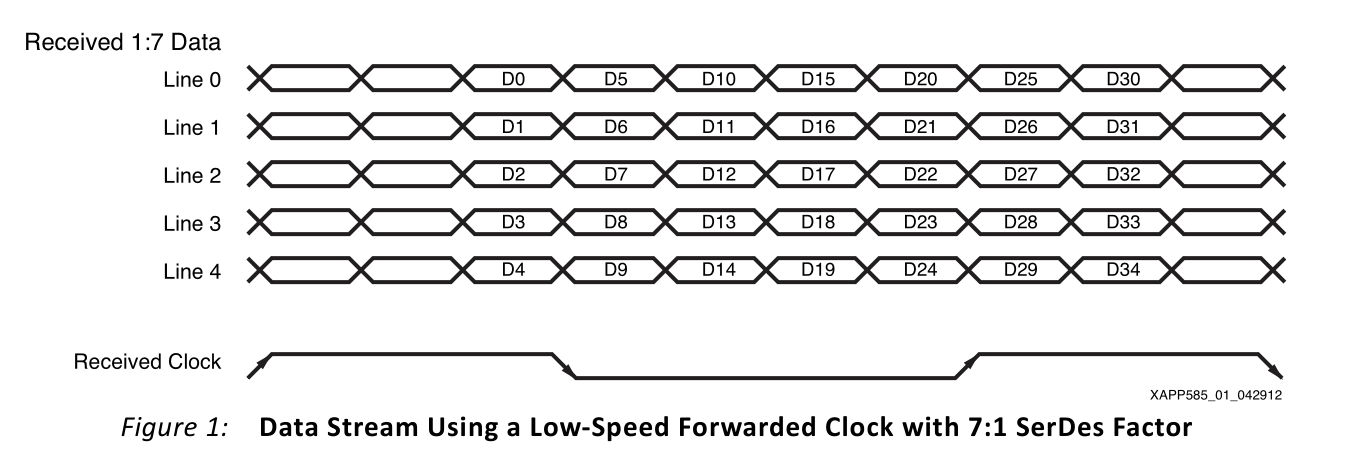

如上图所示,LVDS是典型的源同步传输模型,除此以外还有即将被淘汰的系统同步模型和现在应用广泛的自同步模型。源同步模型由数据线和时钟线组成,LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上,推荐最大速率为655Mbps,理论极限速率为1.923Gbps,具体还是要看硬件的支持,通常相关芯片手册会有介绍。这里的时钟通常称之为随路时钟,并没有规定这个随路时钟的时钟频率是多少,但通常是并行时钟或者串行时钟(SDR)或串行时钟除以2(DDR模式)。它存在的意义便是帮助接收端恢复数据。恢复的过程是同步于随路时钟,发送一个双方约定好的Pattern(即某个确定的值),当接收端恢复出pattern时,认为通道可以传输有效数据。当通信速率较小的源同步模型,例如cypressUSB3.0方案中,可以通过将随路时钟相移的方法满足cypress芯片的时序参数要求。但LVDS的线速度是比较高的,需要通过逻辑代码中微调来找到数据采样的中心点,这也是解决LVDS通信的核心问题!

关于LVDS接口通信的其他概念结合上图阐释,截图出自xapp585-lvds-source-synch-serdes-clock-multiplication.pdf,可以看到随路时钟采用的是并行时钟,一共有五个LVDS传输线同步于此时钟,此外还有通道的概念,通常是一个通道有一个单独的随路时钟,通道内有几个LVDS传输线。图中随路时钟的占空比并不均匀,在一个传输线高电平期间传输3bit,在低电平期间传输4bit,一个并行时钟周期单个传输线上传输的bit个数称为串化因子,图中串化因子是7。SDR模式和DDR模式是相对于串行时钟说的,DDR就是在串行时钟的上升沿和下降沿都发出数据。因此,一个并行周期将传输 7bit*5lines=35bit数据。上述提及的各个LVDS通信中的概念应该是通信双方已知的,就像串口传输通信双方应该协调好波特率等参数。

3.图像相关接口与LVDS

RGB TTL接口信号类型是TTL电平,信号的内容是RGB666或者RGB888还有行场同步和时钟,以及DE信号;LVDS接口信号类型是LVDS信号(低电压差分对),信号的内容是RGB数据和DE信号和时钟,本质是RGB的信号转换成差分串行的数据,不同的屏幕位组合通道组合的方式有所不同;VGA接口与RGB接口信号基本一致,但他是模拟信号,是传统的接口,现在也已基本淘汰。HDMI接口是速度比较快的接口,活跃于生活的各个角落,接口类型丰富,常用的HDMI1.4、2.0和2.1,分别支持最高2k60hz、4K60hz和4K120hz(8K60hz),采用TMDS电平标准,本质是RGB接口经过TMDS编码,该过程可以用编码芯片实现,也可通过支持TMDS标准的FPGA实现。另外,HDMI还可作为输入接口应用。MIPI-DSI接口信号类型是LVDS信号,信号的内容是视频流数据和控制指令,是消费类电子中常见的接口,例如手机、玩具等。此外MIPI还有用于视频采集的CSI接口,常见于各类CMOS图像传感器中。

4.LVDS与serdes

LVDS(低电压差分信号)和SERDES(串行器/并行器)都是用于数据传输的技术,它们各自有自己的优劣势,虽然serdes的速度很快,动辄10Gbps以上,但LVDS仍然以其独特优势活跃在市场上,高速传输:LVDS通常能够支持较高的数据传输速率,适用于高速数据传输的应用。低功耗:LVDS采用差分信号传输,能够在保持高速传输的同时降低功耗。抗干扰能力强:LVDS具有良好的抗干扰能力,能够在嘈杂的电磁环境下保持数据传输的稳定性。比起LVDS,serdes可以提供更大速率的传输,另外可以适配长距离传输的要求,可以适配多种协议有更好的灵活性,后面有Serdes接口系列,很快上线~

5.传送门

●我的主页

●FPGA通信接口汇总导航

●源码链接

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/122680.html