大家好,欢迎来到IT知识分享网。

相关文章

Verilog基础:task和function的使用(一)

一、前言

任务(task)和函数(function)即提供了从不同位置执行公共过程的能力(因为这样可以实现代码共享),也提供了把大过程分解成小过程的能力(因为小过程更便于阅读和调试)。下面将介绍task和funtion之间的不同点,介绍如何定义和调用task和function。

注意:函数和任务都是可以综合的,但是有诸多的要求和限制,所以要谨慎使用。

二、简述task和function的不同

下面列出了task和function之间的不同点。

- 语句限制:function不能包含时序控制语句(如#延迟、@事件、wait语句),只能在一个仿真时间点进行;而task可以包含时序控制语句,因此从task开始执行,到结束可能需要一段时间。

- 互相调用:function不能调用task(这很好理解,因为task可能包含时序控制语句);而task可以调用function。

- 参数传递:function至少要有一个input类型的参数,而不能有output和inout类型的参数(通过返回值传递输出,而不是输出端口);而task既可以没有任何参数(就像testbench一样),也可以有各种类型的参数。

- 调用限制:function调用相当于一个右值,就像C语言里面的函数一样;task调用只能作为语句使用。

- 功能限制:function只能对输入值返回一个结果值,而task可以支持各种用途,可以计算并返回多个结果值。对于task,只有使用output和inout才能把结果值传递回来。function可以在表达式中当做操作数使用,操作数的值就是function的返回值。

三、 task的声明和使能

task的使能(就是调用,但是在标准中对task使用的是enable,对function使用的是call),就是从一条可包含输入和输出的调用语句,控制从调用的过程转到task。当task完成时,控制再返回调用的过程,所以如果task包含时序控制的语句,那么调用task的时间和退出task的时间可能不同。task可以再使能(调用)其他task,没有数量的限制。

1、task的声明

task声明的语法如下:

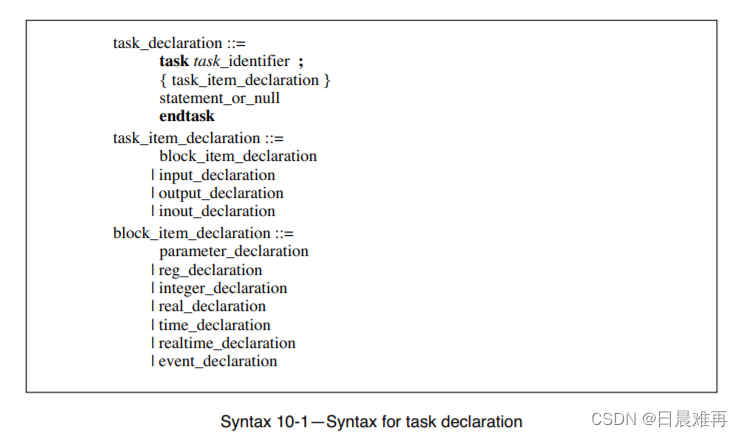

Verilog-1995:

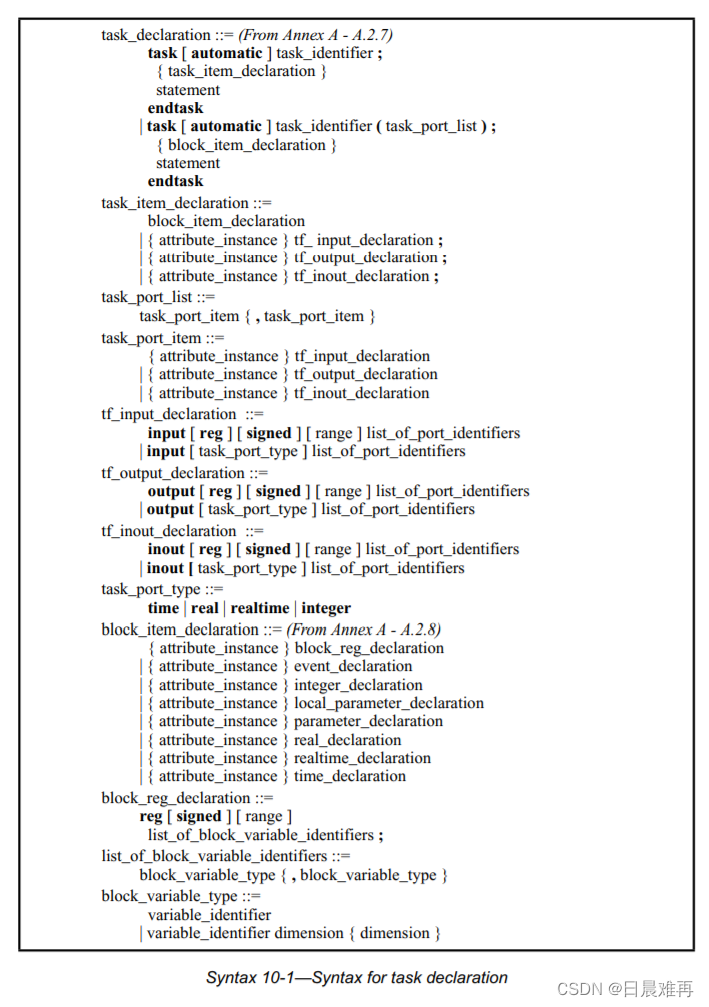

Verilog-2001:

task声明的说明:

1. 第一种是Verilog-1995的语法,传递的参数在task_identifier;后面依次声明。

2. 第二种是Verilog-2001的语法,传递的参数还可以在task_identifier();的括号内部定义,这是ANSI-C的风格。

3. 可以在task内声明各种类型的变量(reg、integer、real、realtime),parameter、local parameter以及event也是支持的声明的。

4. Verilog-2001新增了task的automatic特性,没有automatic的task是静态的,所有task声明的参数和变量都是静态分配存储空间,仿真器对所有并发执行的同一个task共享这些参数和变量。

5. 使用automatic的task是可重入的(Reentrant),仿真器对每个并发执行的task动态分配存储空间,即每个task拥有属于自己独有的一套变量,但在automatic task结束时,这些变量会被销毁。

2、task的使能和参数传递

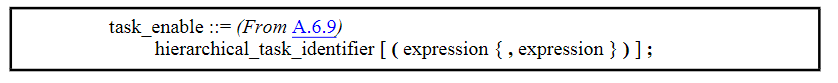

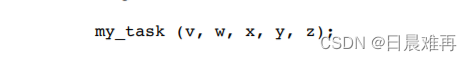

task的使能就是把括号内以逗号分隔的表达式列表作为实际参数传递给task,语法如下:

注意其中使用的是层次task名,这意味着在定义一个task的模块外,也是可以调用该task的,只要它能够在使用处利用层次名引用到,详见该文Verilog基础:标识符的层次名引用(一)。

task使能的规则如下:

1. 如果task没有参数,那么使能时可以使用task_identifier();或者task_identifier;

2. 如果task有参数,那么表达式(实参)的个数要与task定义的参数对应,不能出现未连接的端口(module可以出现未连接的端口)。

3. 表达式列表中表达式的计算顺序是不定的。

4. 如果task的形参是input类型,那么对应的表达式(实参)可以是任何表达式。

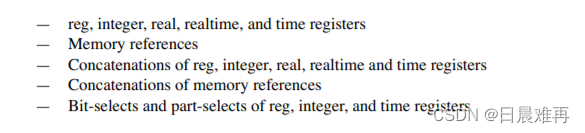

5. 如果task的形参是output类型,那么对应的表达式(实参)要符合过程赋值LHS的规则(这与module不一样,module的output端口只能连接外部的线网型信号)。

6. 执行task是使能语句时,对应表达式的值(实参)被传入到input和inout形参中(只在执行时传入一次,这和module输入端口的连接不一样)。

7. 从task返回时,output和inout形参的值会被自动传回对应表达式(实参)中(只在返回时传回一次,这和module输出端口的连接不一样)。

8. 所有的参数按值传递,而不是按引用传递。即task内对输入形参的操作,不会影响输入实参。

9. task语句没有返回值,因此相当于一个语句,而不是可被当作操作数的右值,如下所示。

module test; reg a; task test_task(); $display("This is a task"); endtask initial a = test_task; // 错误 initial test_task; // 正确 endmodule例子:task定义

上图以两种方式定义了task,下面的表达式使能task。

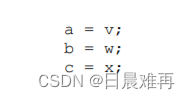

task使能语句的实参v,w,x,y,z对应task形参a,b,c,d,e,在task被使能的时刻,input和inout类型的形参a,b和c分别接受实参v,w,x传递的值,就好像执行了以下的赋值语句。

实际上,task的输入输出端口默认都是reg类型,这和module不同,module的输入端口默认也只能是wire类型,module的输出端口可以被定义为reg类型或wire类型。

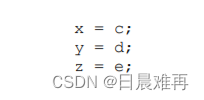

在task执行的过程中,task计算并改变形参c,d,e的值,在task结束时,将c,d,e的值赋值给实参x,y,z就好像执行了以下的赋值语句。

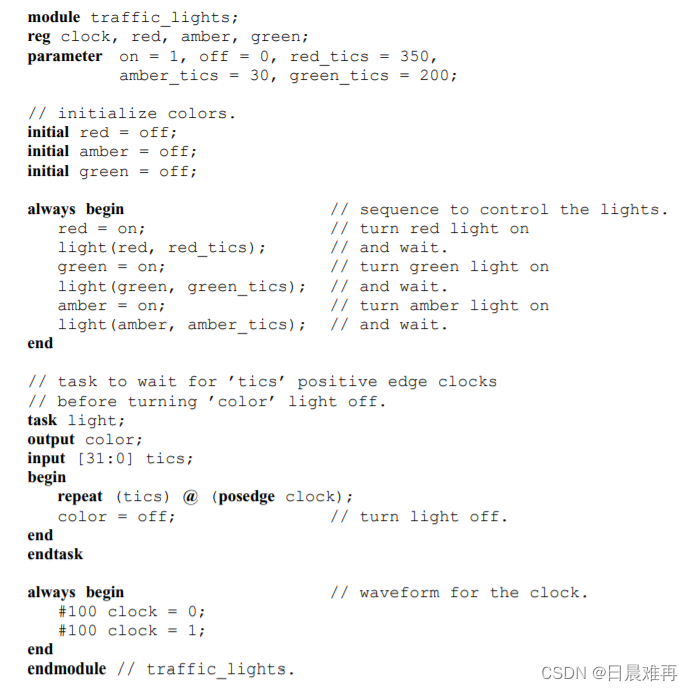

例子:使用task描述信号灯

3、task的内存使用和并发进程

可重入任务(Reentrance task)对验证工程师非常重要,因为这些工程师需要多次并发地调用同一个task。但是很多人并不知道,Verilog-1995的任务使用静态变量,这就意味着在第一次任务调用还在运行的时候,对这个任务再做第二次调用,那么这两次任务调用使用的是同样的一组静态变量,这会给testbench带来严重的问题。

Verilog-2001对task和function作了扩充,增加了一个可选的属性automatic,每次在task或function调用时,局部变量要用的存储空间才被分配,这样就可以实现task和function的重入。重入就是在一个task或function执行期间,可以再次调用这个task或function。

下面是关于static task和automatic task之间的对比。

1. 对于static task,它的所有参数和变量都是静态的,不管并发地使能task多少次。所谓静态是指,对于模块的每个实例,仿真器只在初始时为static task声明的参数个变量分配一次存储空间,然后就一直使用,在执行时不再分配。注意:对于模块的不同实例,每个static task还是使用自己独立的存储空间。

2. static task中声明的变量,包括input、output和inout参数,会保持最后一次使用时候的值(因为是reg类型)。

3. 对于automatic task, 当每次并发地使能它时,仿真器会为它的所有参数和变量分配新的存储空 间。因为automatic task声明的参数和变量在task完成时要释放,所以task完成后就不能再使用他们。

4. automatic task中声明的变量和参数,包括input、output和inout参数,在仿真开始时的时候被初始化为默认值(x),而input和inout在使能时被初始化为表达式列表传进来的值。

对于static task和static function,它们的参数和变量具有静态的生命时间,就是这些变量只是在开始的时候分配一次,然后就一直使用它。这就导致这些参数和变量始终保持最后一次使用时的值。但是综合工具不这么看,综合工具认为task和function不会依赖这些参数和变量以前的值,认为每次调用的时候都要重新初始化这些参数和变量。这就有可能导致仿真和综合不一致。所以为了得到一致的结果,为了每次都重新分配这些参数和变量,我们应该使用automatic。

图源IEEE Verilog-2001 Standard

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/125287.html