大家好,欢迎来到IT知识分享网。

一、CPU架构

Zeppelin

Naples(EPYC1)

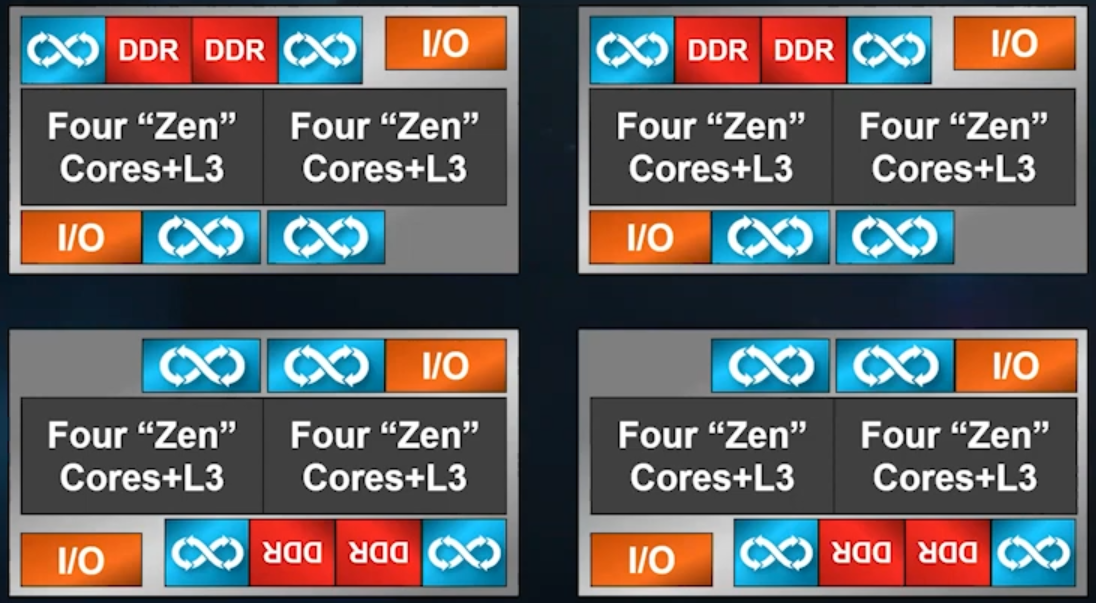

4 die SoC架构

- 32个zen架构core

- 8个DDR4通道

- x128 PCIe4

- 4*213 mm2

- GF14nm

单die架构:

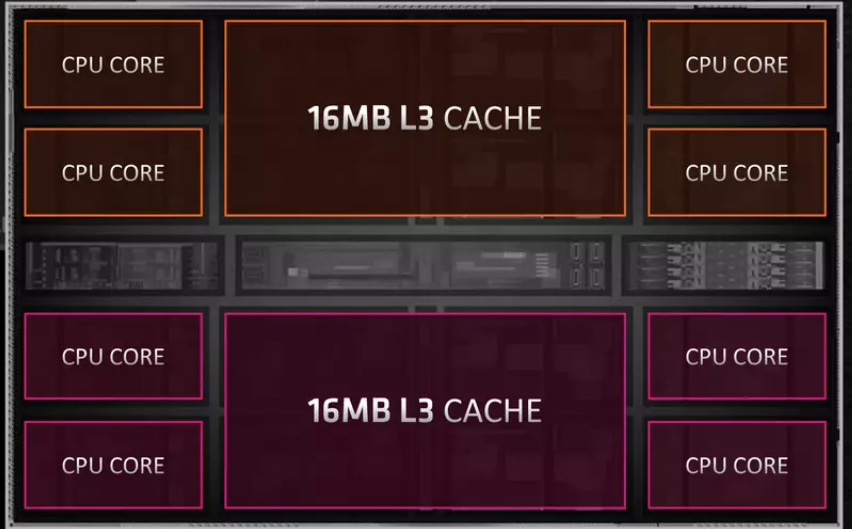

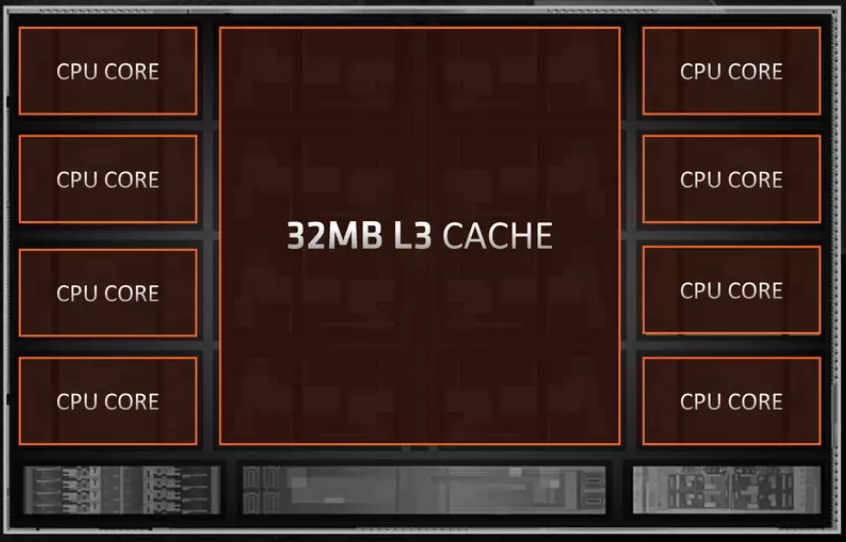

- CCX

CPU complex,每个CCX包含4个CPU core,CCX间可以通过Infinity Fabric通信(SCF+SDF)

CCX间任务的分配由cache-corherent non-uniform memory access(ccNUMA-aware)实现,确保线程不会从一个CCX迁移到另一个是很重要的,由于CCX间数据通信需要额外的延迟,线程的搬移会引起不必要的性能损耗。

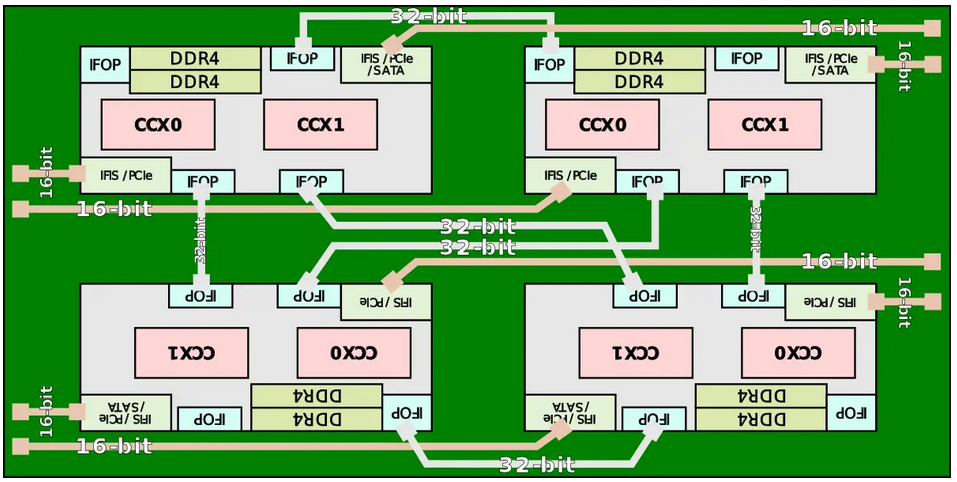

双die架构:

- GMI接口

die-to-die的IFOP接口,每个时钟cycle传输16B read + 16B write。

四die架构

- 每个die有四组GMI接口,但只有和其他die最近的三组接口被使用

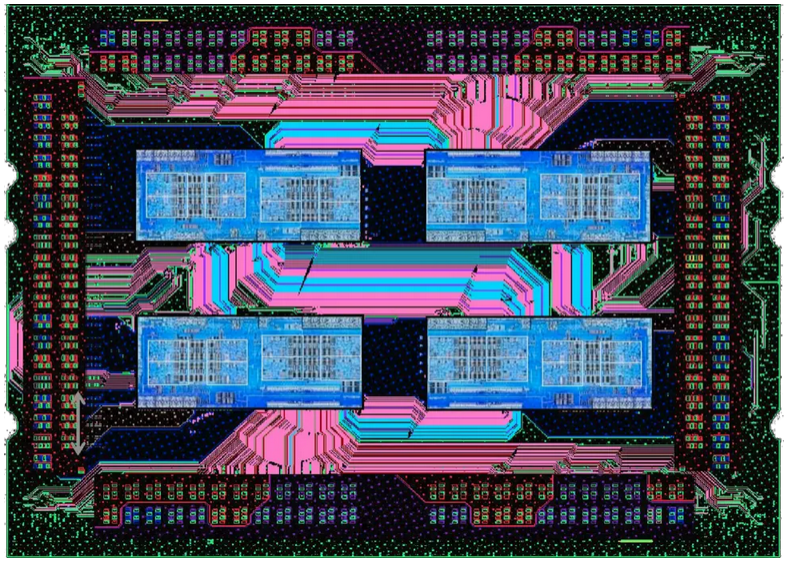

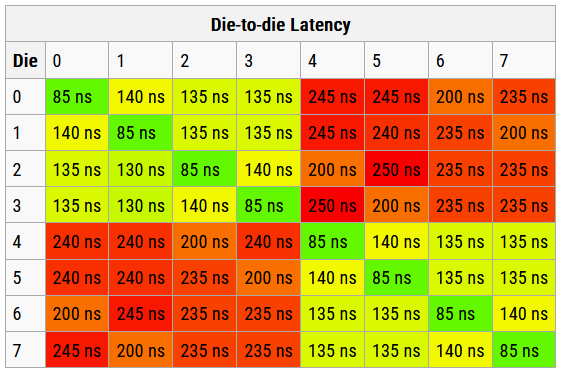

如图是EPYC系列die互连某层的布局布线图,视图上方和下方的粉色布线是die的UMC出来的接口,视图中间的粉色和蓝色布线是双向的GMI链路,左下和右上die的连接被隐藏了,左上芯片和右上芯片摆放位置相同,下面的芯片摆放旋转180度。 - die间延迟如图所示

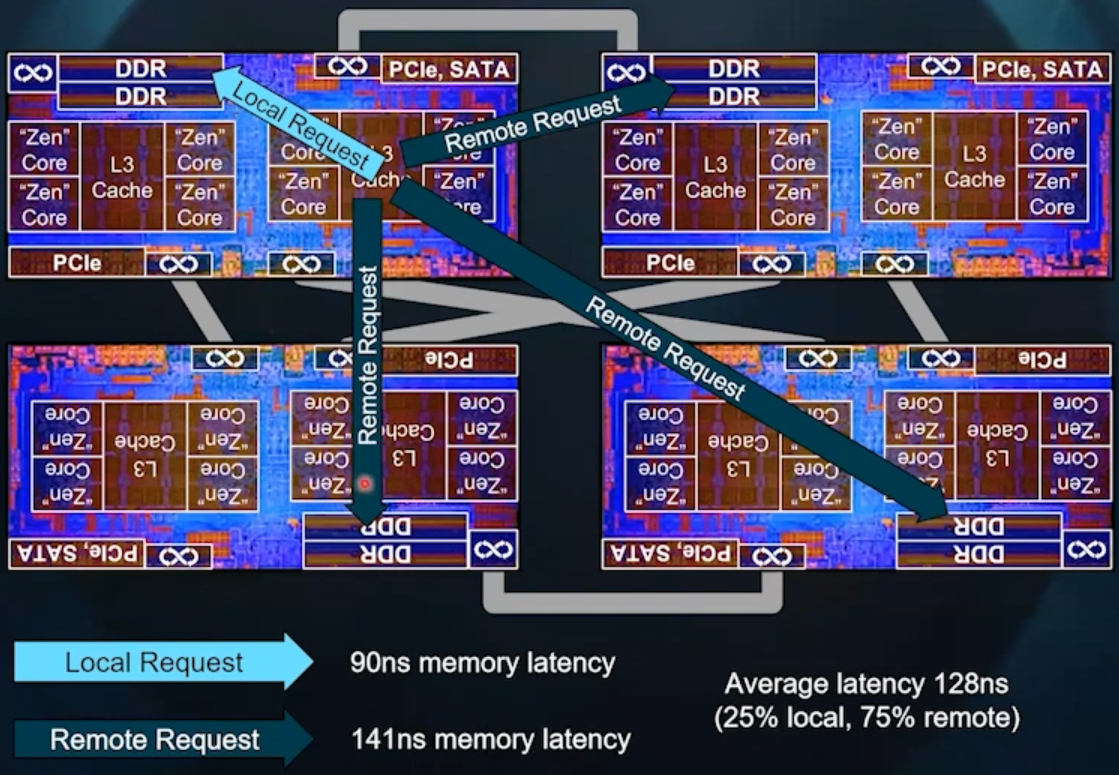

die0-3和die4-7分别为两路CPU。

- DDR访问延迟

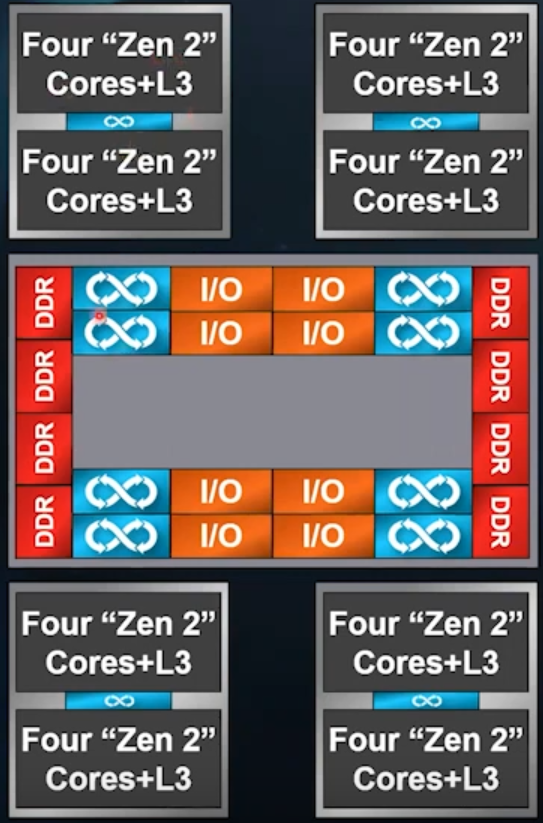

Rome(EPYC2)

- 8*DDR channel

- x128 PCIe

- 发布时间:2019年

- CCD (16~64 cores): TSMC 7nm

- IO die: GF 14nm (server) ; GF 12nm (client)

CCD

CPU die即为core complex die(CCD),每个CCD有两个CCX,一个SMU 和一个GMI2接口模块。

- SMU

system management unit,系统管理单元,读取温度、电压、电流数据,并调整CPU主频和电压,限制IO die的fast local closed loop和global loop。CCD和IO die间SMU的通信通过单lane的IFOP接口。 - GMI2

global memory interconnect version 2,GMI2在GMI的基础上扩展了CCD和IO die连接的数据接口,即32 lane的双向IFOP接口;同时传输带宽增加到每个时钟cycle传输32B read + 16B write。

IO die

- 8个DDR通道(所有CCD访问ddr的延迟均一样)

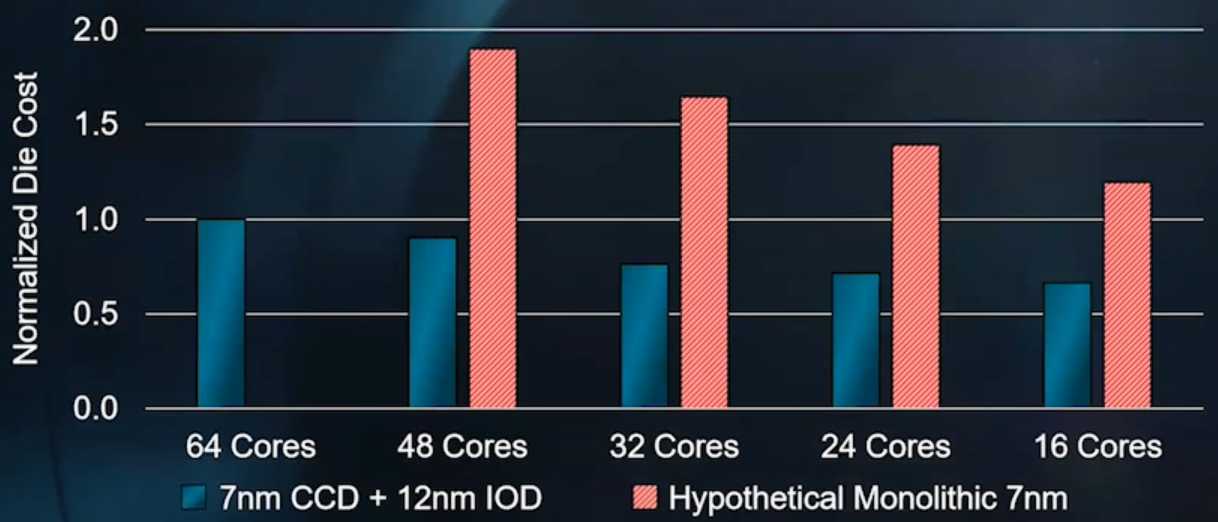

蓝色柱状图是7nm+12nm小芯片架构的成本,红色柱状图是7nm大芯片架构的成本,64core的大芯片架构由于芯片面积超过光刻掩模版极限(lithographic reticle limit),未有数据。

EPYC架构只需要两次tape-out,分别是CCD和IOD,根据核数需要选择构建CCD的数量,因此成本大大降低

Milan(EPYC3)

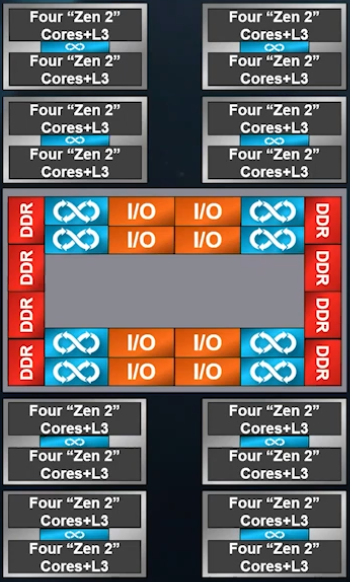

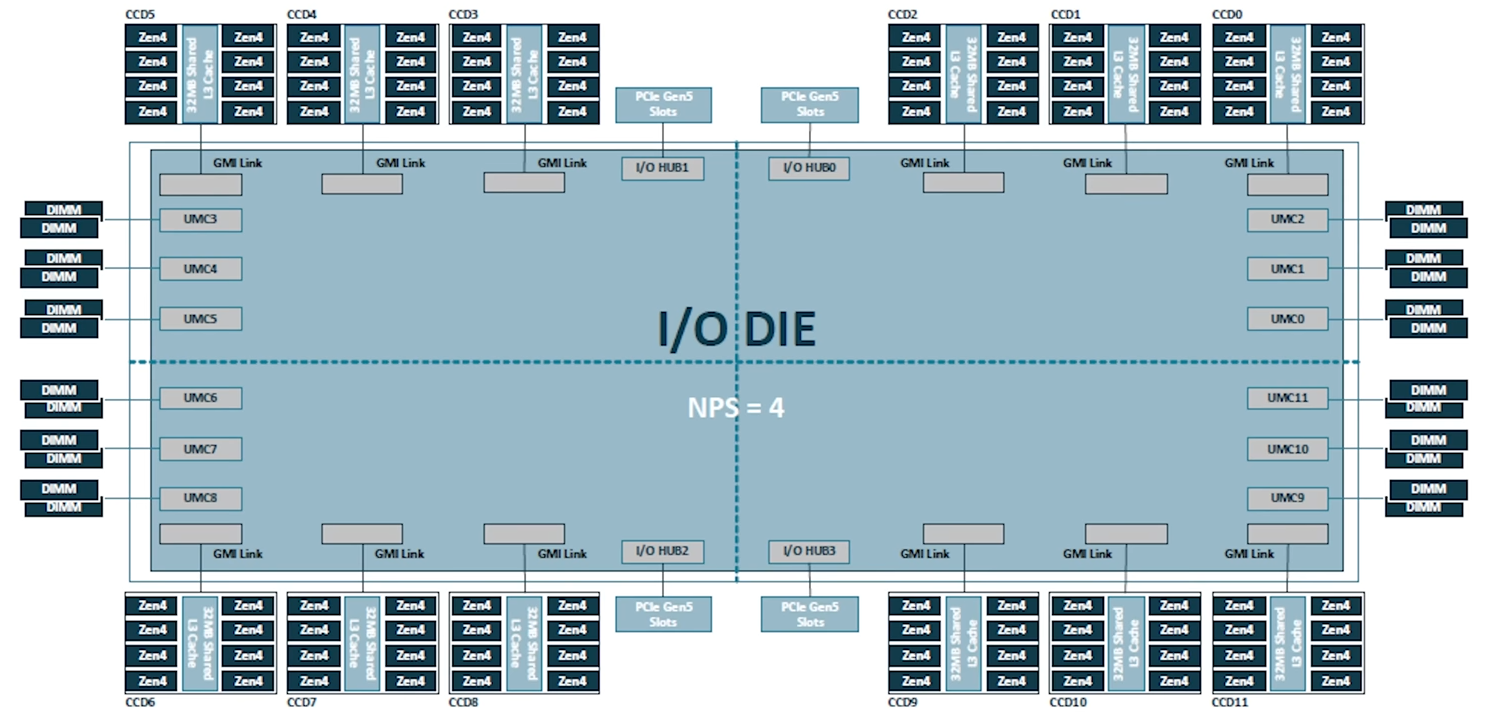

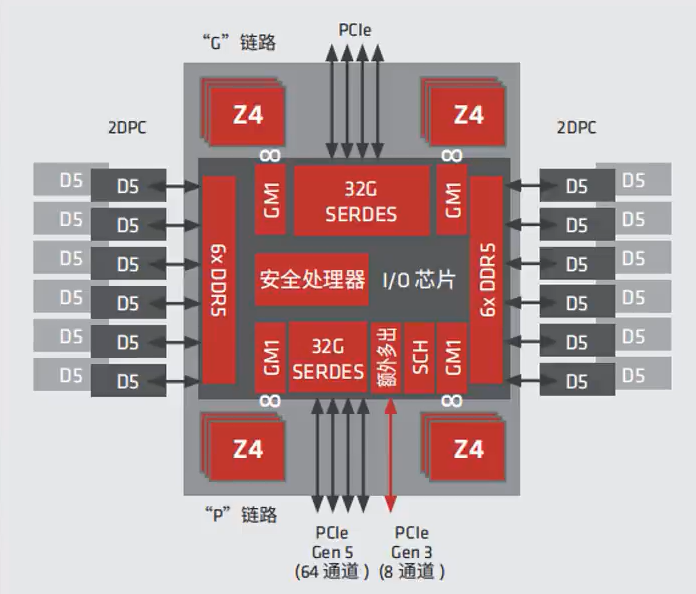

Genoa(EPYC4)

- 12*DDR5 channel

- 4/8/12* CCD (zen4 core) + 1 * IOD

超过4CCD使用GMI3-Narrow,少于4则使用GMI-Wide

IOD复用 - 8x16 + 2x4 = 136 Lane PCIe5

二、CPU Core架构

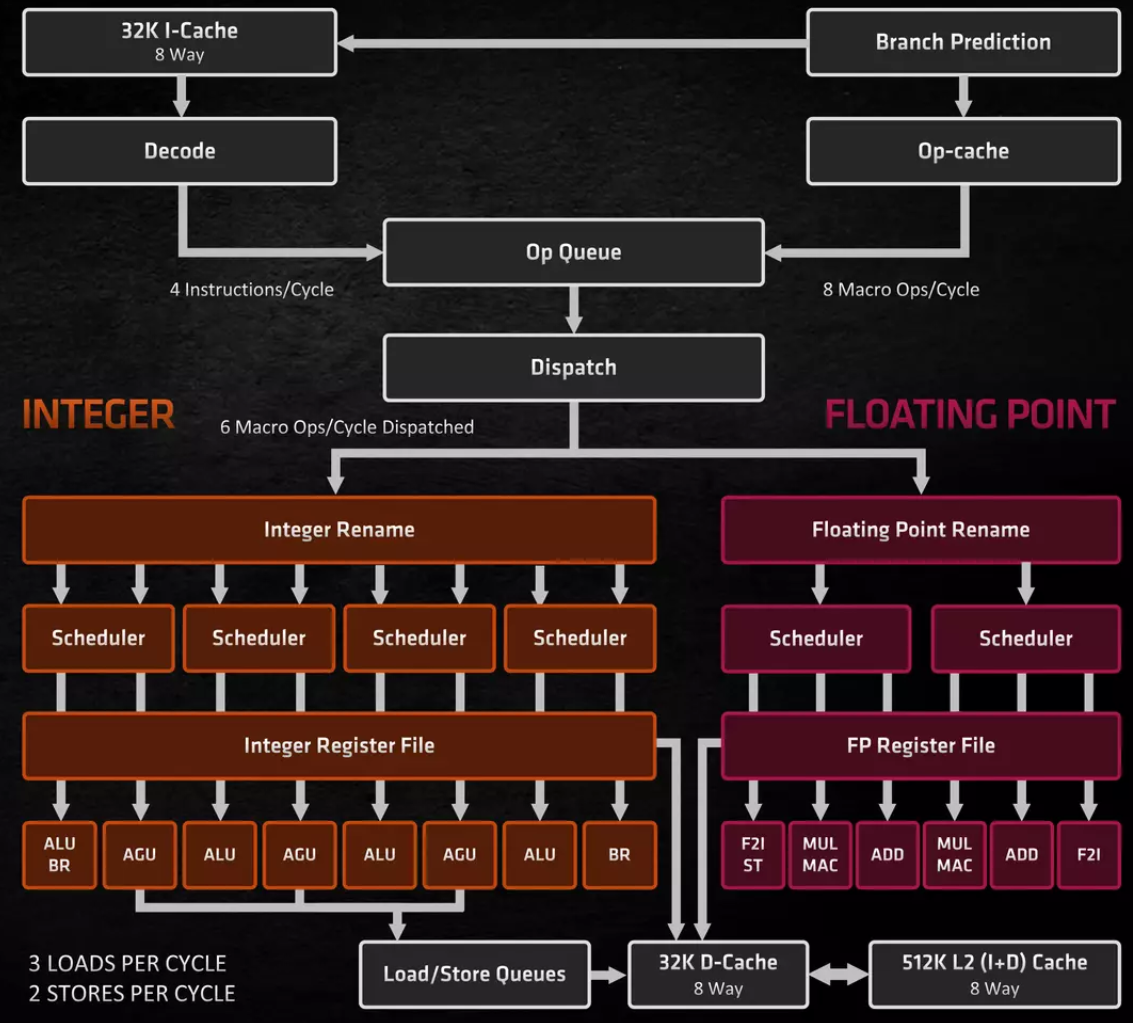

Zen

Zen系列是每一代AMD处理器芯片的core架构,包括取指、分支预测、cache架构等

Zen架构使用chiplet技术将多核系统划分为多个die互联封装的架构,单核整体还是一个SoC,包含4个CPU core(core complex,即CCX),南桥模块组(IO)和北桥模块组(DDR)。

- 发布时间:2017年3月2日

- 制成工艺:GF 14 nm

参考链接:wikichip:Zen

Zen+

Zen2

- CCD结构

Zen3

参考链接:AMD官网 Zen3架构

- CCD结构

三、互联方式

3.1 Die间互联

3.2 Die内互联

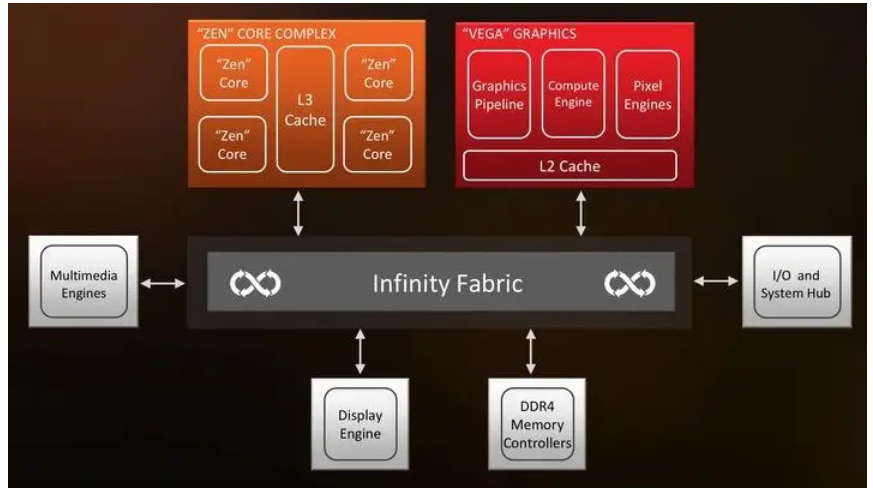

ONION (Fusion Compute Link)

GPU和CPU互联的一致性总线,用于cache snooping

GARLIC (Radeon Memory Bus)

GPU和Memory controller连接的非一致性总线,

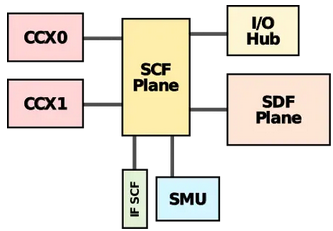

3.3 芯片互连架构Infinity Fabric

业务数据六模块 SDF

如图所示是一个点对点结构和中心岛结果混合的单die架构:

- 两个CCX通过CCM (Cache-Coherent Master)连接到SDF平台,CCM提供core数据一致性访问维护机制;

- IO Hub模块通过IOMS (I/O Master/Slave)接口和SDF相连。

- DDR4通过UMC (Unified Memory Controller)与SDF相连,时钟频率和DRAM memclk相同

- serdes接口通过CAKE (coherent AMD socket extender)与SDF连接,CAKE负责串行编码和解码,每个cycle发送128bit串行数据,时钟频率和DRAM memclk相同,serdes接口包括IFOP和IFIS。

- 在SDF模块中,只可以通过CCM和IOMS访问DDR

控制数据流模块 SCF

SCF通过单独的IFIS接口和外部的设备连接

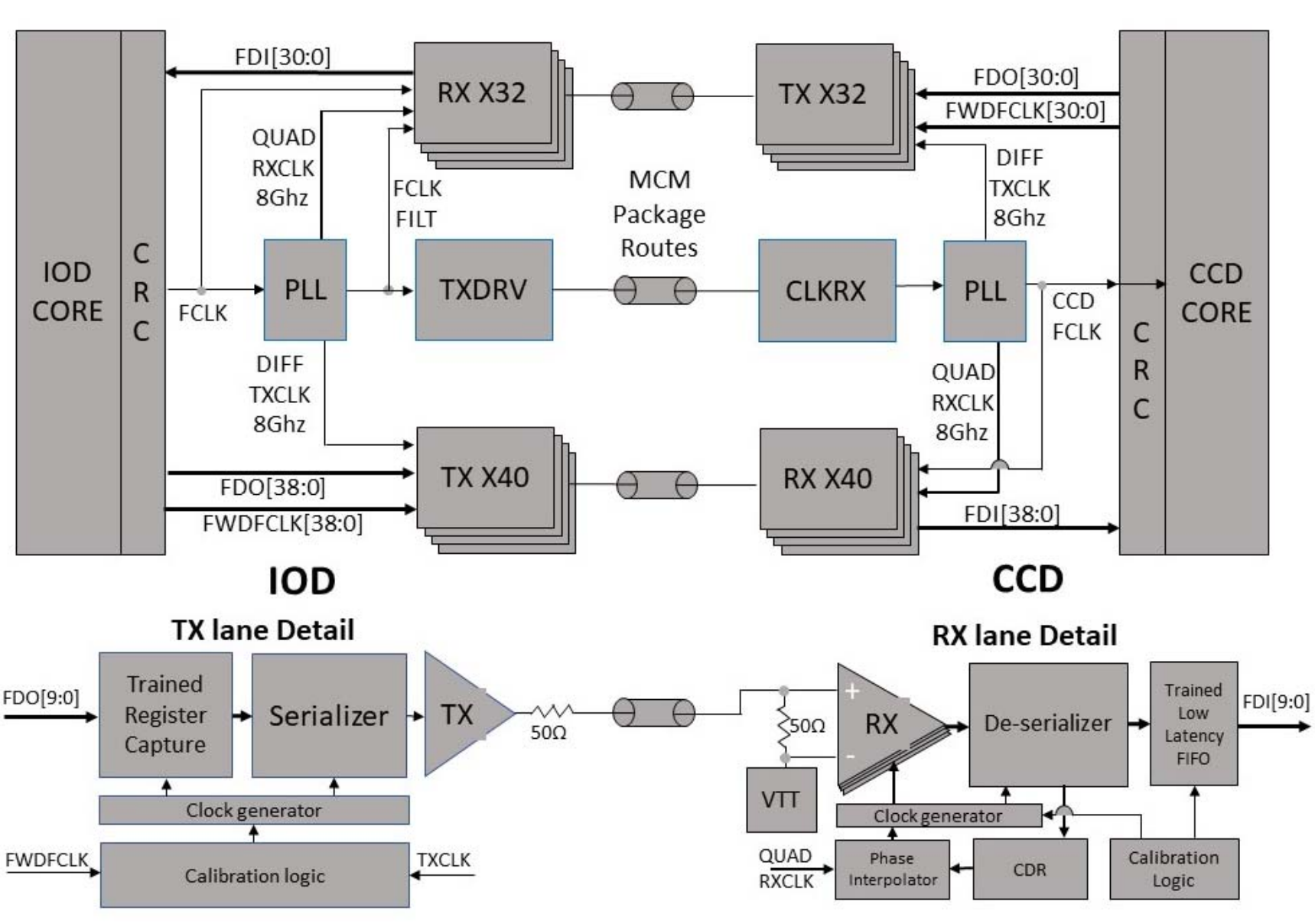

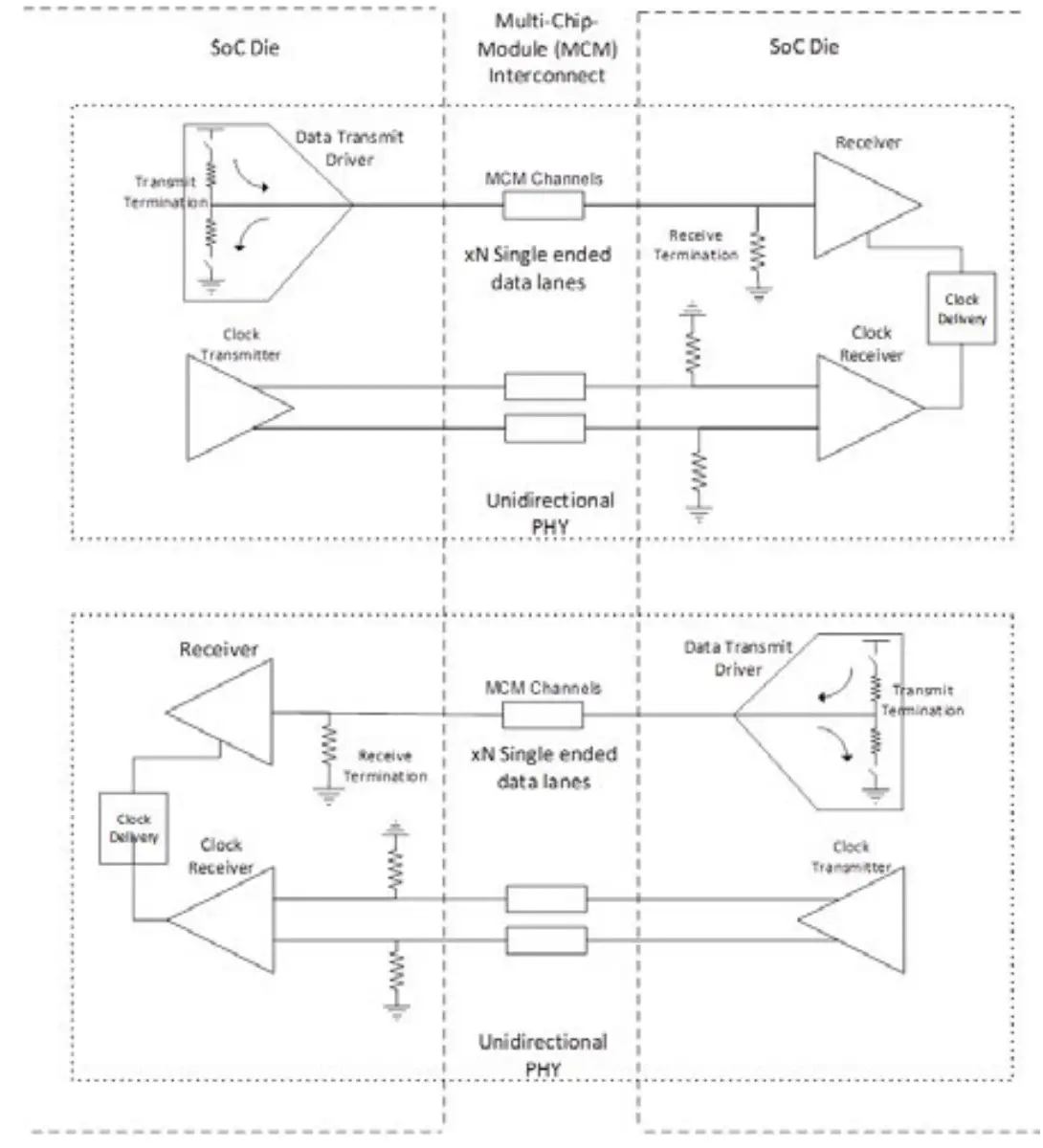

Die间总线接口 IFOP

- 32bit单端data信号

- 差分时钟

- 能耗2 pJ/b

- 串行全双工

非对称的RX/TX架构

上图来源于:

S. Naffziger, K. Lepak, M. Paraschou and M. Subramony, “2.2 AMD Chiplet Architecture for High-Performance Server and Desktop Products,” 2020 IEEE International Solid-State Circuits Conference – (ISSCC), San Francisco, CA, USA, 2020, pp. 44-45, doi: 10.1109/ISSCC19947.2020.9063103.

芯片间总线接口 IFIS

- 16位差分data,每个CAKE时钟周期进行8次传输

- 无时钟信号

- 能效11pJ/b

3.4 特征小芯片

3D V-cache

四、GPU架构

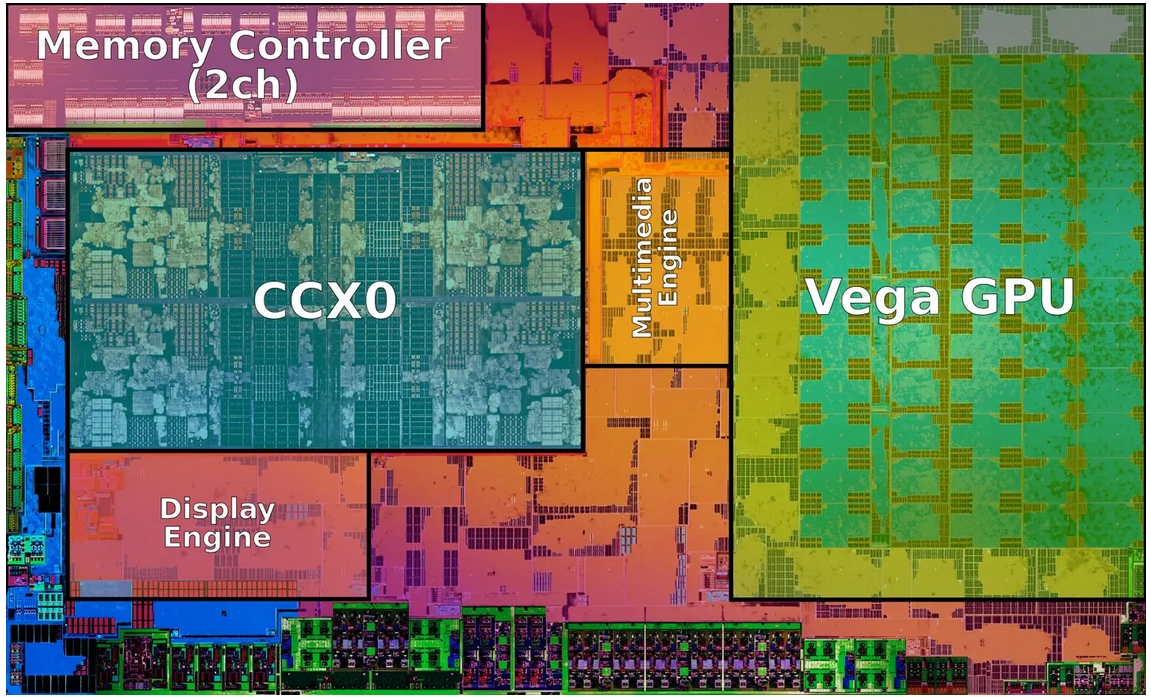

Zen-based APU

- GF 14nm

基于Zen架构的加速器处理单元是一个完整die,包括一个CCX、一个Vega计算核心和其他部件通过infinity Fabric互联组成的系统,

MI200

包含两个die,每个die包含了8个ACE(asynchronous compute engine),并通过Infinity Fabric总线连接

MI300

采用CPU die和GPU die集成的计算加速芯片,共享同一个内存地址空间,软件不必担心内存管理,编程更加容易。

参考文献

- “Amd cdna 2 architecture,” 2021. [Online]. Available: https://www.amd.com/system/files/documents/amd-cdna2-white-paper.pdf

- AMD官网:EPYC4

- AMD官网:AMD近几年发表的学术论文

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/125888.html