大家好,欢迎来到IT知识分享网。

光纤接口简介

学习自正点原子FPGA教程

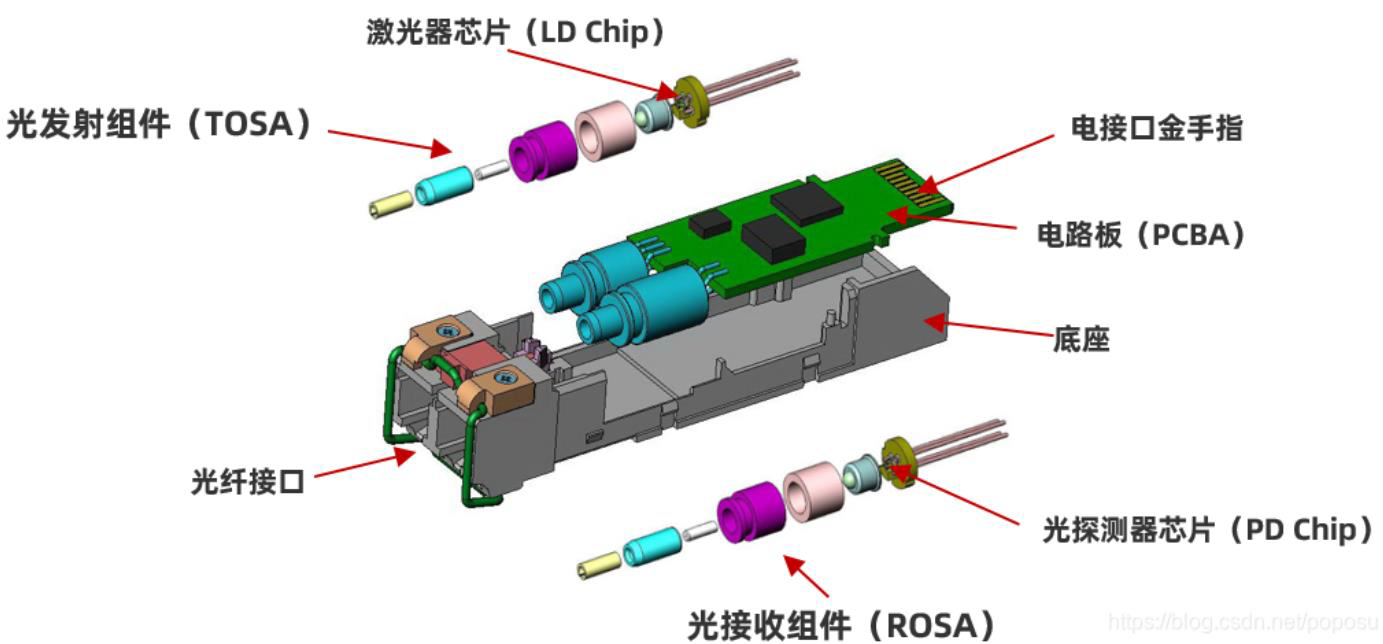

光模块组件

从上图中可以看到:一个光模块,通常由光发射器件(TOSA,含激光器)、光接收器件 (ROSA,含光探测器)、功能电路和光(电)接口等部分组成。其中在发射端,驱动芯片对原始电信号进行处理,然后驱动半导体激光器( LD)或发光二极管 LED)发射出调制光信号;在接收端,光信号进来之后,由光探测二极管转换为电信号,经前置放大器后输出电信号。

常见光模块的类型:

| 分类方式 | 类别 |

|---|---|

| 封装类型 | 1×9、GBIC、X2、XENPAK、XFP、SFP、SFP+、SFP28、QSFP、QSFP28、CFP、CFP2、QSFP-DD、OSFP等 |

| 速率 | 10Mbps、100Mbps、155Mbps、622Mbps、1.25Gbps、2.125Gbps、4.25Gbps、10Gbps、25Gbps、50Gbps、100Gbps、400Gbps等 |

| 波长 | 850nm、1310nm、1490nm、1550nm、CWDM、DWDM等 |

| 模式 | 单模(黄色)、多模(橙黄色、蓝绿色) |

| 距离 | 100m、300m、550m、10km、20km、40km、80km、120km、160km |

| 调制格式 | NRZ、PAM4、DP-QPSK/n-QAM等 |

| 是否支持WDM | 灰光模块(不支持WDM)、彩光模块(支持WDM) |

| 光接口工作模式 | 双纤双向(Duplex)、单纤双向(BiDi) |

| 激光器类型 | 垂直腔面发射激光器(VCSEL)、法布里-珀罗激光器(FP)、分布式反馈激光器(DFB)、电吸收调制激光器(EML)等 |

| 光探测器类型 | PIN结二极管(PIN)、雪崩光电二极管(APD) |

| 连接器接头 | FC、SC、ST、LC、MU、MTRJ |

| 使用性 | 热插拔(GBIC、SFP、XFP、XENPAK)和非热插拔(1*9、SFF) |

| 工作温度 | 商业级(0~70°C)、延展温度(-20~85°C)、工业级(-40~85°C) |

高速收发器 GTH

xilinx公司不同系列的高速串行收发器的类型和速率的对比:

| 器件系列 | GTP | GTR | GTX | GTH | GTY | GTZ | GTM | 最大收发器(个) | 峰值带宽(Gb/s) |

|---|---|---|---|---|---|---|---|---|---|

| Spartan 6 | 3.20 | / | / | / | / | / | / | 8 | 51 |

| Zynq 7000 | / | / | / | / | / | / | / | 16 | 400 |

| Zynq™ UltraScale+ | / | 6.00 | 12.50 | 16.30 | 32.75 | / | / | 4/44/28 | 3268 |

| Artix™ 7 | 6.60 | / | 12.50 | / | / | / | / | 16 | 211 |

| Kintex 7 | / | / | 12.50 | / | / | / | 28.05 | 32 | 800 |

| Virtex 7 | / | / | 12.50 | 13.10 | / | / | / | 59/96/16 | 2784 |

| Kintex UltraScale | / | / | / | 16.30 | / | / | / | 64 | 2086 |

| Virtex UltraScale | / | / | / | 16.30 | 30.50 | / | / | 60/60 | 5616 |

| Kintex™ UltraScale+ | / | / | / | 16.30 | 32.75 | / | / | 44/32 | 3268 |

| Virtex™ UltraScale+ | / | / | / | / | 32.75 | / | / | 128/48 | 8384 |

| Versal Premium 系列 | / | / | / | / | 32.75 | 112.00 | / | 28/70 | 9040 |

| Versal ACAP | / | / | / | / | / | 58.00 | 58.00 | 44/52 | 6032 |

UltraScale 架构中的GTH 收发器是节能型收发器,支持从500mb /s 到16.375 Gb/s 的线路速率。一般应用于PCIE、SFF、SFP+、XAUI、SATA 等高速接口设计。

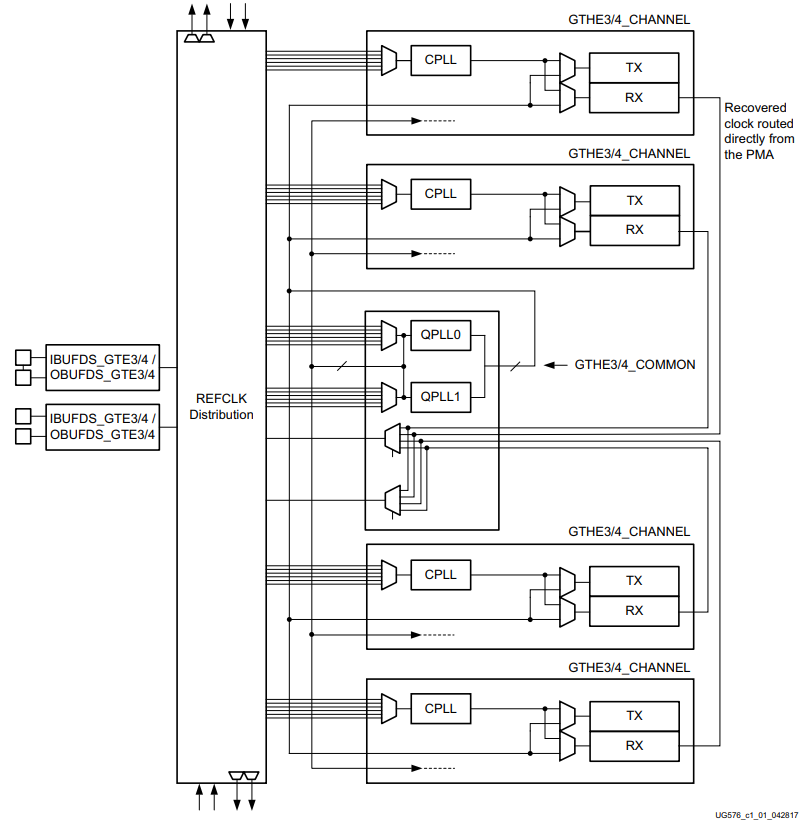

FPGA 开发板板载的FPGA 器件提供了一组高速收发器GTH。GTH 接口的结构图如下所示:

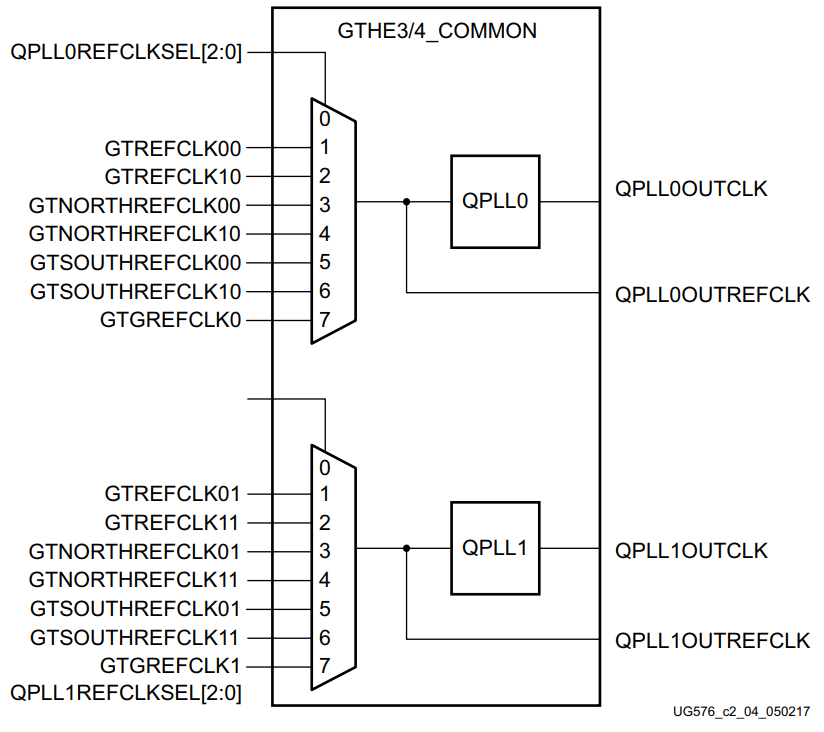

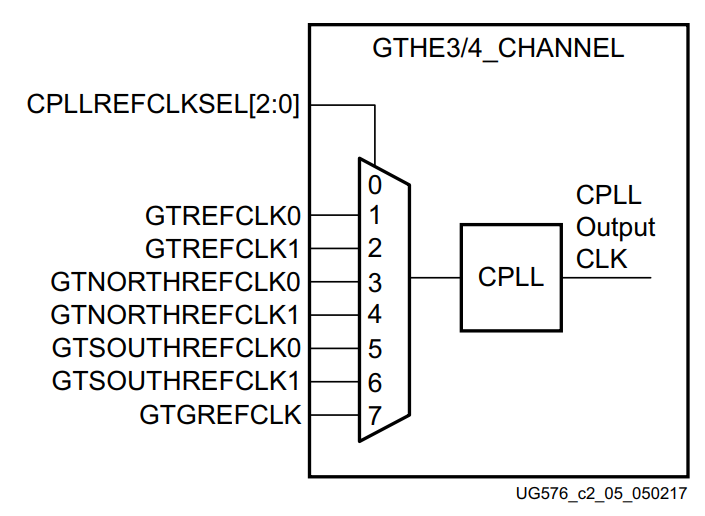

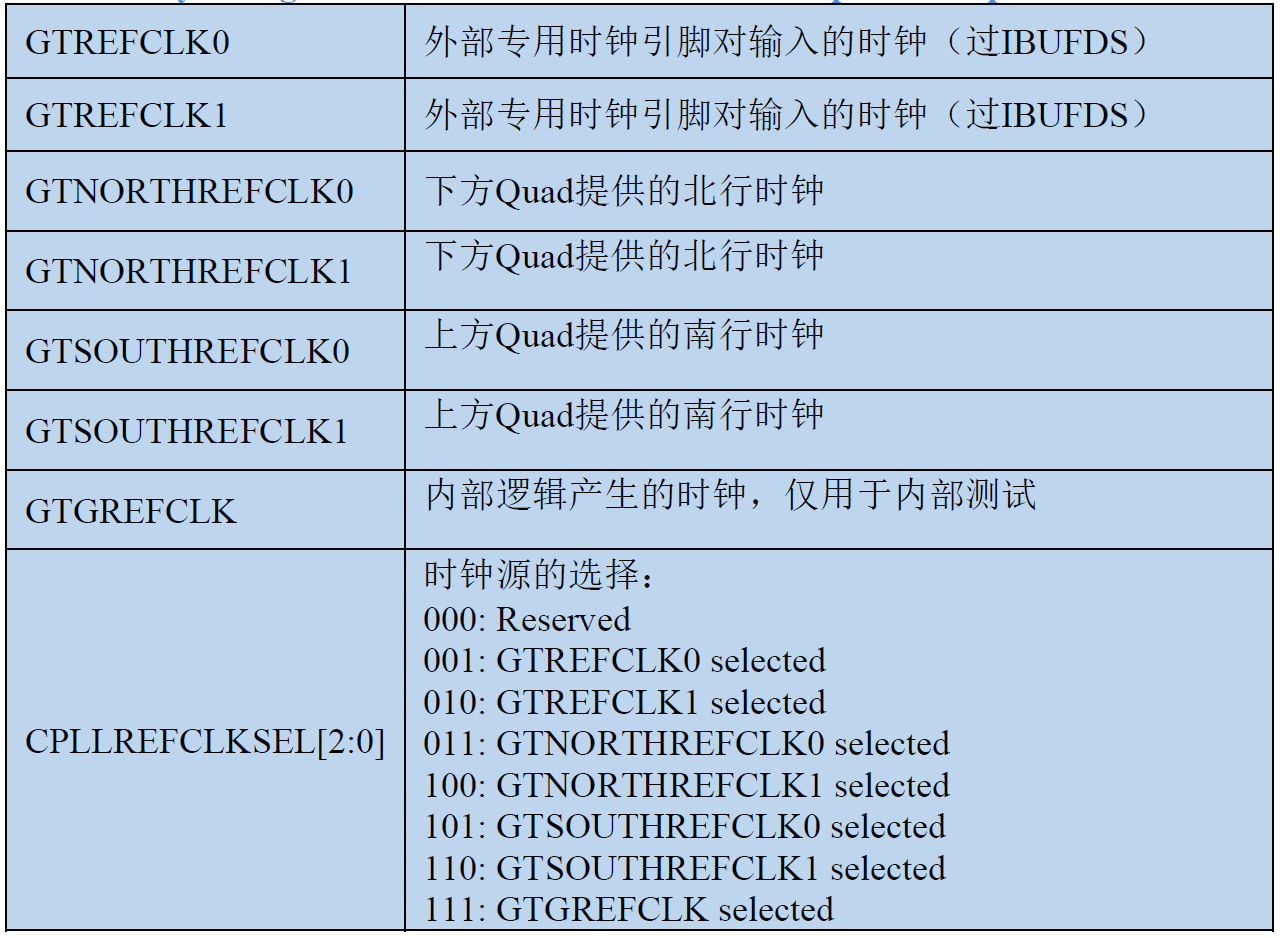

从上图中可以看到无论是QPLL还是 CPLL它的源时钟都有 7路来源,具体说明如下表所示(这里以CPLL举例):

从上表中可以看到对于CPLL来说总共七路时钟来源,两路来自外部时钟引脚对,经过 IBUFDS后转换成单端时钟信号就可以接入 CPLL;还有四路来自上下 Quad,当 FPGA中不止一个 Quad的时候当前Quad中的 GTH参考时钟可以来自上面的两个 Quad也可以来自下面的两个 Quad,注意最多只能跨两个Quad,最后一路时钟来源是内部逻辑产生的时钟,只能用作内部测试。

从上表中可以看到对于CPLL来说总共七路时钟来源,两路来自外部时钟引脚对,经过 IBUFDS后转换成单端时钟信号就可以接入 CPLL;还有四路来自上下 Quad,当 FPGA中不止一个 Quad的时候当前Quad中的 GTH参考时钟可以来自上面的两个 Quad也可以来自下面的两个 Quad,注意最多只能跨两个Quad,最后一路时钟来源是内部逻辑产生的时钟,只能用作内部测试。

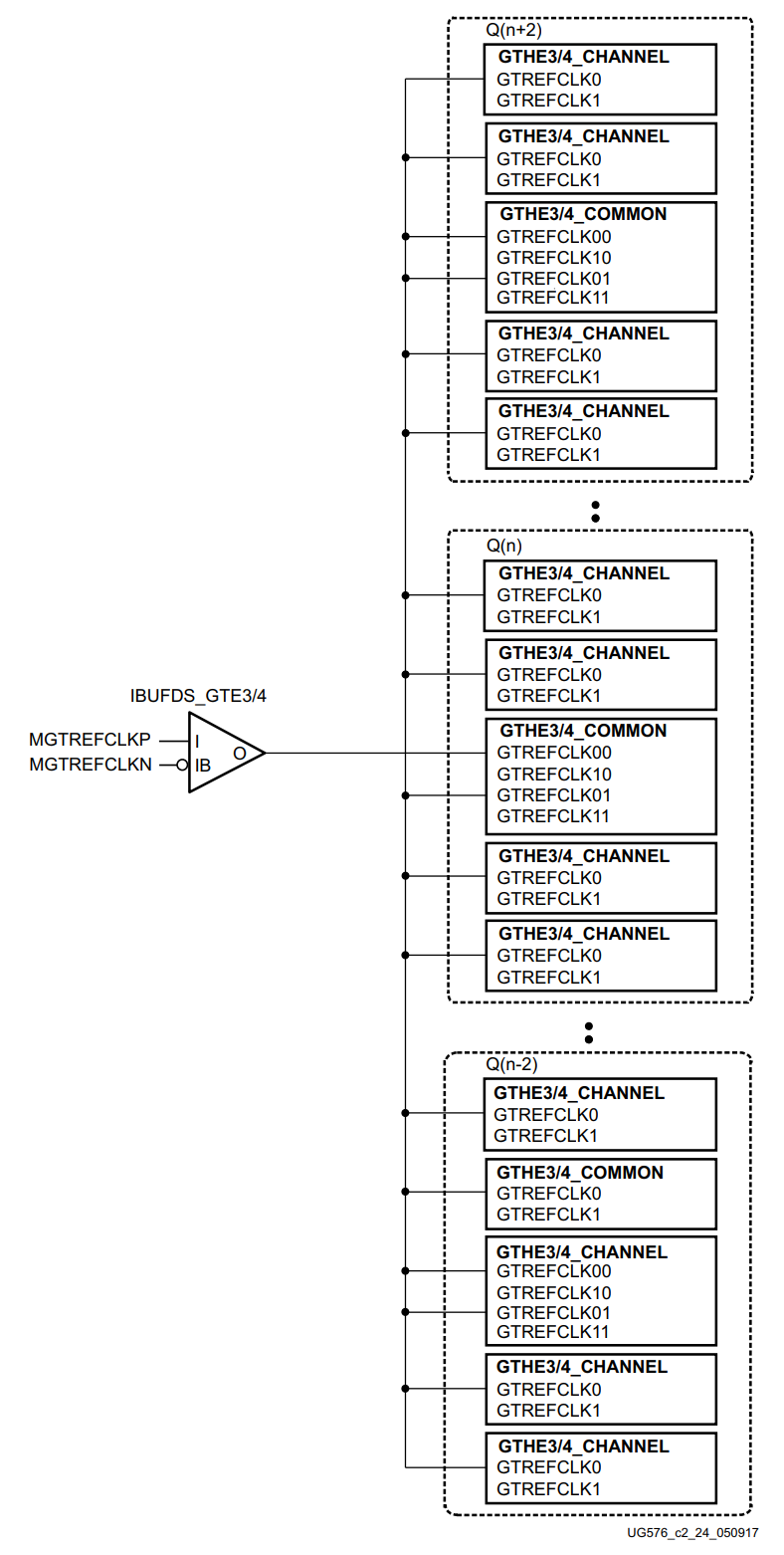

QPLL与 CPLL时钟来源图

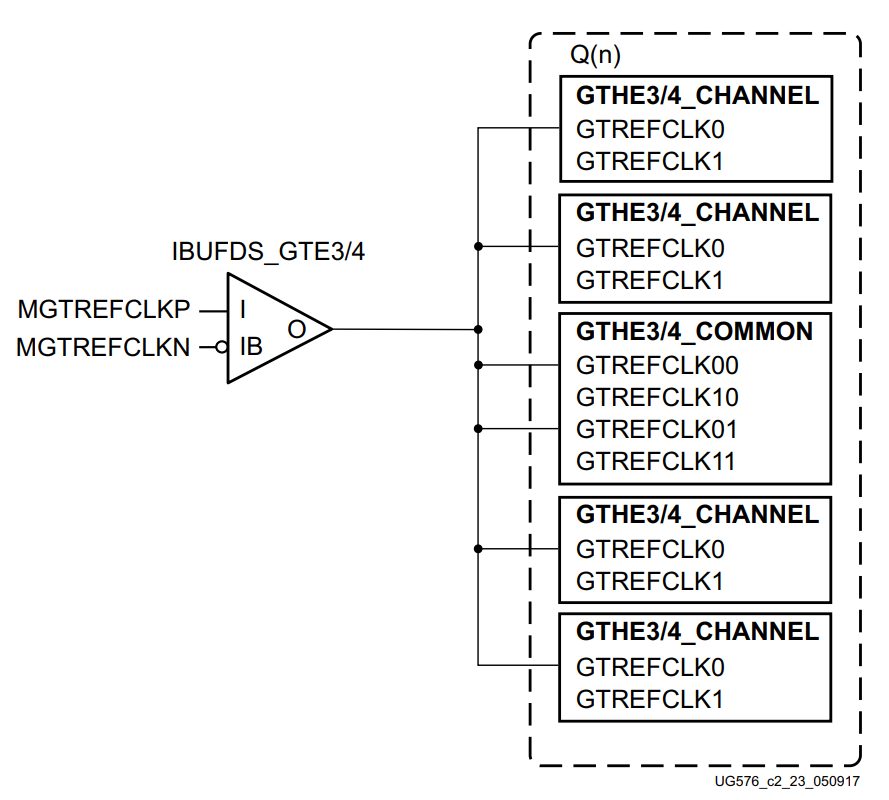

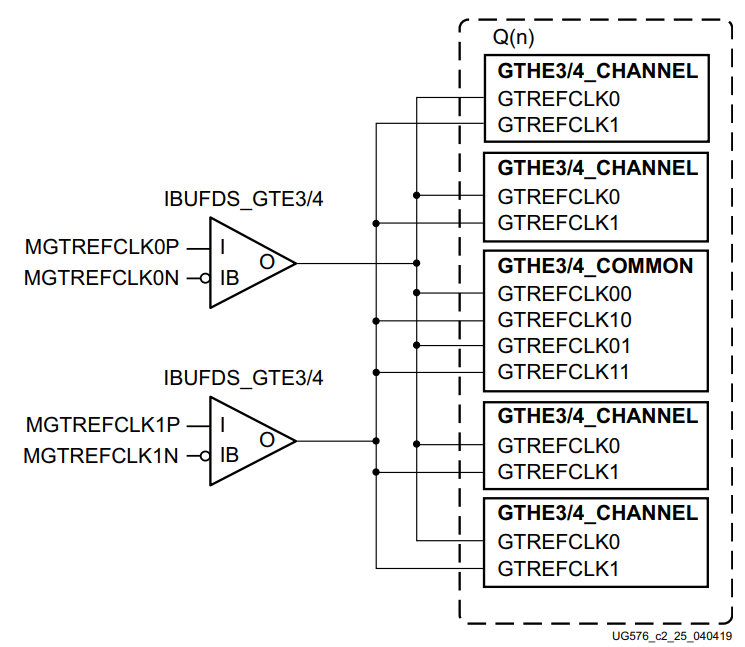

了解完整个Quad的时钟拓扑结构后我们再来了解一下时钟的使用模式,主要分为两种使用模式,一种是 Single外部输入模式,另一种是 Multiple外部输入模式,如下图所示:

Single外部输入模式

Multiple外部输入模式

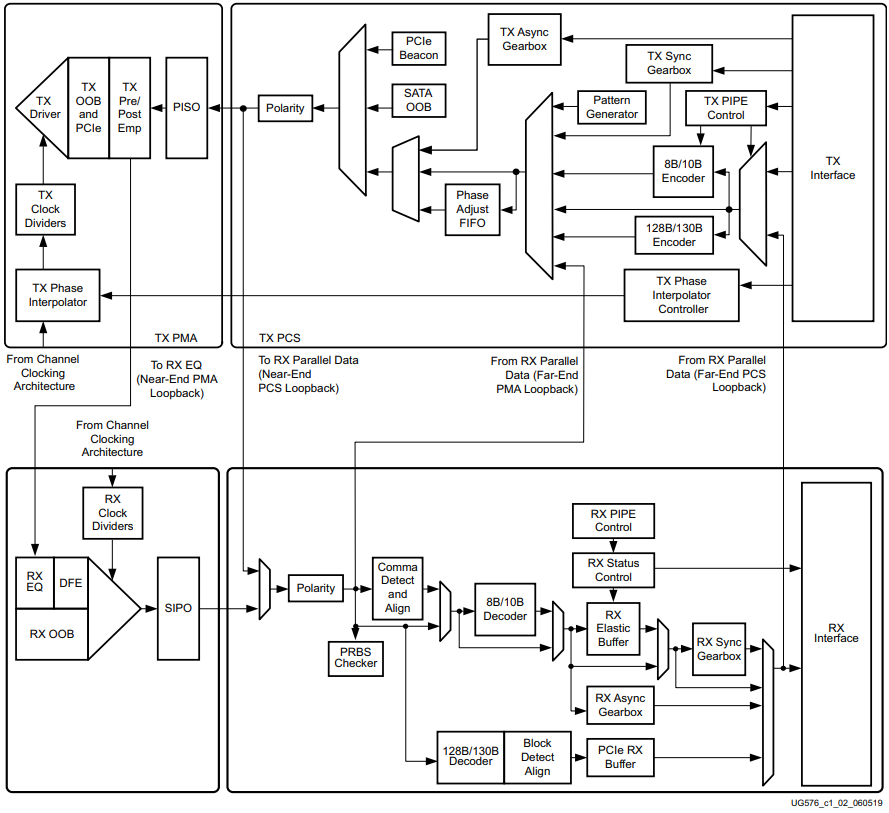

GTH Channel结构图

从上图中可以看到单个Channel由发送接口和接收接口组成,每个接口又分为两部分结构,这两部分结构分别是 PMA和 PCS。 PMA和 PCS内部又由许多功能模块构成,如下表所示:

PCS和PMA组的结构和功能

| Group | Structure | Feature |

|---|---|---|

| PCS | TX Interface | GTH收发器的发送数据通道(属性可配置) |

| TX 8B/10B Encoder | 8B/10B编码器 | |

| TX Synchronous Gearbox | TX同步变速箱,用于高速通信协议支持64B/66B编码 | |

| TX Phase | 相位插补器主要是对PMA数据进行微调 | |

| Phase Adjust FIFO | 相位调整的缓冲FIFO,主要用来处理数据跨时钟域的相位调整 | |

| TX Pattern Generator | 测试数据生成器,用于产生伪随机比特序列。伪随机比特序列(PRBS)是一种常用的高速链路信号完整性测试方法。 这些序列看起来是随机的,但是具有特定的属性,可以用来衡量链路的质量。 | |

| TX Polarity Control | TX数据极性控制,如果TXP和TXN差分走线在PCB上意外交换,则GTH收发器会相应调整以正确发送数据。 | |

| RX Polarity Control | RX数据极性控制,如果RXP和RXN差分走线在PCB上意外交换,则GTH收发器会相应调整以正确接收数据。 | |

| RX PRBS Checker | PRBS校验器,对RX端接收的PRBS序列进行校验。 | |

| RX 8B/10B Decoder | 8B/10B解码器 | |

| RX Elastic Buffer | GTH收发器包含一个RX弹性缓冲器,用来解决RXCLK和RXUSRCLK两个时钟域之间的数据跨域问题。 | |

| RX Synchronous Gearbox | RX同步变速箱,用于高速通信协议支持64B/66B、64B/67B编码。 | |

| RX Interface | GTH收发器的接收数据通道(属性可配置)。 | |

| PMA | RX DFE | 离散自适应高速滤波器 |

| PISO/SIPO | 串并转换 | |

| TX/RX OOB | 每个GTH收发器都支持生成串行ATA (SATA)、串行附加小型计算机系统接口(SCSI, SAS)规范中描述的带外 (OOB) 序列,以及PCI Express规范中描述的信标。 | |

| TX Driver | TX驱动器是一个高速差分输出缓冲器。 |

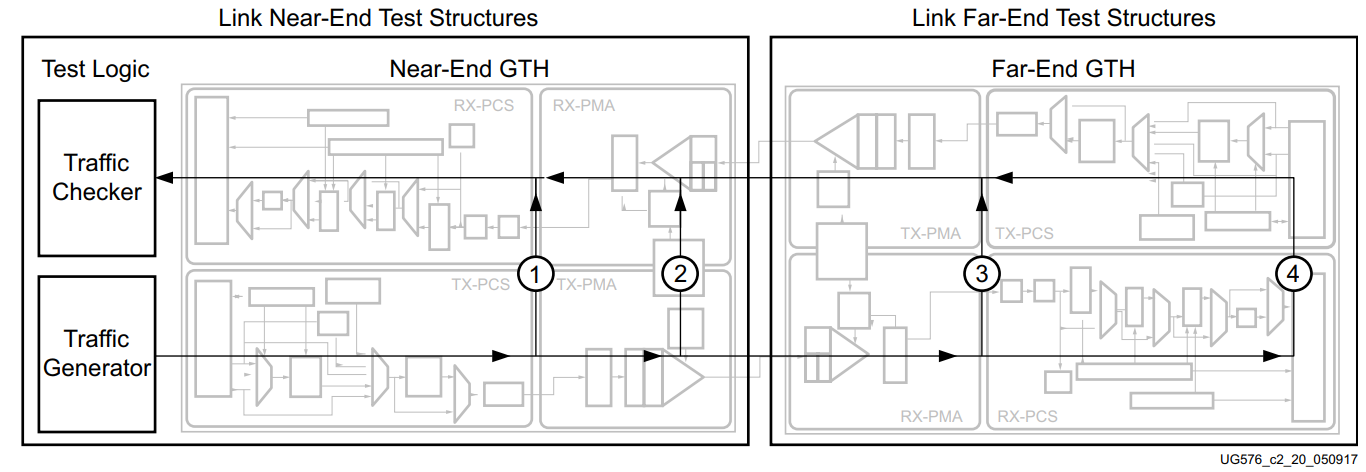

回环路径图

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/126733.html