大家好,欢迎来到IT知识分享网。

计算机组成原理之机器:存储器

Chapter3:存储器

3.1 概述

存储器可分哪些类型?

现代存储器的层次结构,为什么要分层?

没有哪一种存储器能同时满足高容量、高速度、低价格,为了同时满足这些需求,使用软件或硬件或软硬件方式将各种存储器“连接”在一起

3.2 主存储器

3.2.1 概述

主存的基本组成

主存与CPU之间的联系

MDR与主存(双向),数据的读和写

MAR与主存(单向),将MAR中地址传送给主存

主存中存储单元地址的分配

一根线有0和1两种状态,n根线共有 2 n 2^n 2n种状态,每种状态对应一个地址,一个地址对应存储空间基本单位1字节(1Byte=8bit)

1字(Word)=8字节(Bytes),1字节=8位(bit)

主存的技术指标

3.2.2 半导体存储芯片简介

3.2.3 随机存取存储器RAM

静态随机存取存储器SRAM

SRAM的工作原理是在存储单元中使用触发器存储数据,通过使一个触发器的输出控制另一个触发器的输入,可以将数据存储在SRAM中。—引自:day35-2 Sram 静态存储器

保存0和1的原理是什么?

双稳态触发器

基本单元电路的构成是什么?

对单元电路如何读出和写入?

SRAM读操作

SRAM写操作

典型芯片的结构是什么样子?

W E ‾ \overline{WE} WE低电平表示进行写操作,高电平表示读操作、 C S ‾ \overline{CS} CS低电平时该芯片被选中

A 0 A 9 A_0~A_9 A0 A9为地址信号,从中我们知道该芯片的存储单元个数为 2 9 = 1 K 2^9=1K 29=1K个, I / O 1 I / O 4 I/O_1~I/O_4 I/O1 I/O4为读写数据端口从中我们知道每个存储单元占4位,综上该芯片存储容量=存储单元个数1K × 每个存储单元所占位数4位

SRAM芯片如何进行读写操作?

行地址6位,经过译码产生0~63共64个行选信号

列地址经过译码后的0号线连接了第一组中第0列和第二组中第0列和第三组中第0列和第四组中第0列

对单元电路如何读出和写入?

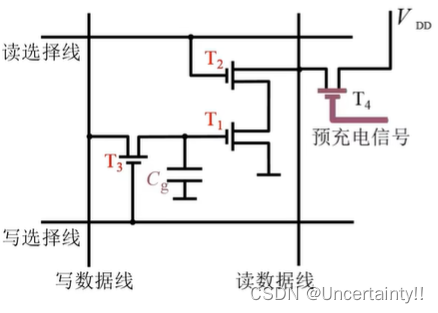

三管DRAM读操作

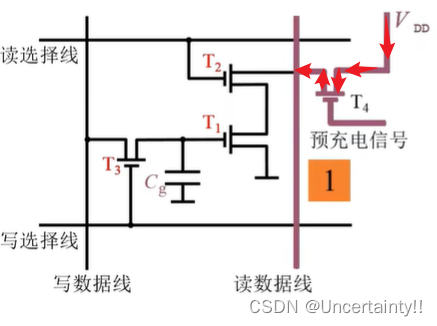

预充电信号有效,则T4被打开 预充电信号有效,则T4被打开 |

Vdd通过T4会对读数据线充电,读数据线变为高电平1 Vdd通过T4会对读数据线充电,读数据线变为高电平1 |

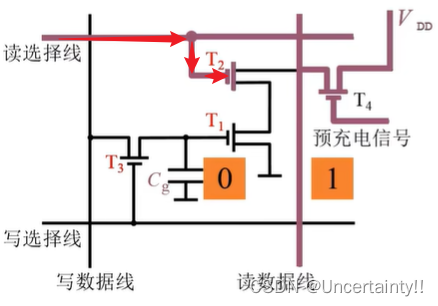

如果进行读操作T2导通,若Cg无电荷,则T1栅极为低电平0不会导通,读数据线保持高电平1,综上如果保存的信息为0,则读出为1 如果进行读操作T2导通,若Cg无电荷,则T1栅极为低电平0不会导通,读数据线保持高电平1,综上如果保存的信息为0,则读出为1 |

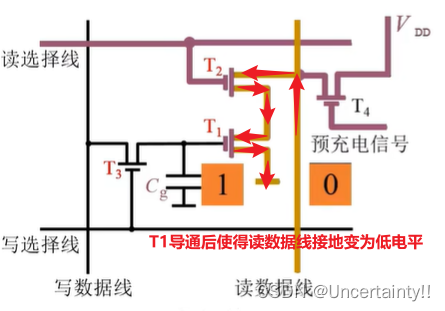

如果进行读操作T2导通,若Cg有电荷,则T1栅极为高电平1导通,读数据线变为低电平,综上如果保存的信息为1,则读出为0 如果进行读操作T2导通,若Cg有电荷,则T1栅极为高电平1导通,读数据线变为低电平,综上如果保存的信息为1,则读出为0 |

综上在读操作中,读出的信息与电容中存的信息相反,所以需要在读出后加一个非门来保证读出信息与原存信息的一致性

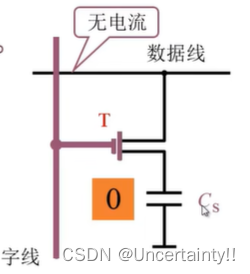

若Cs保存的为0,数据线上不会有电流 若Cs保存的为0,数据线上不会有电流 |

若Cs保存的为1,数据线上就会有电流 若Cs保存的为1,数据线上就会有电流 |

综上,读出时数据线有电流为1,无电流为0 写入时Cs充电为1,放电为0

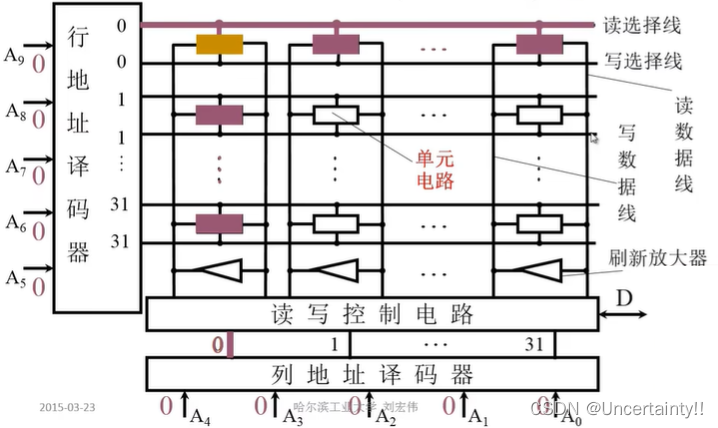

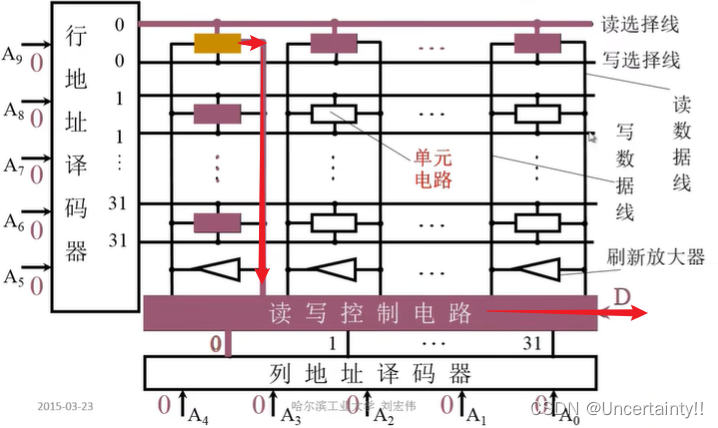

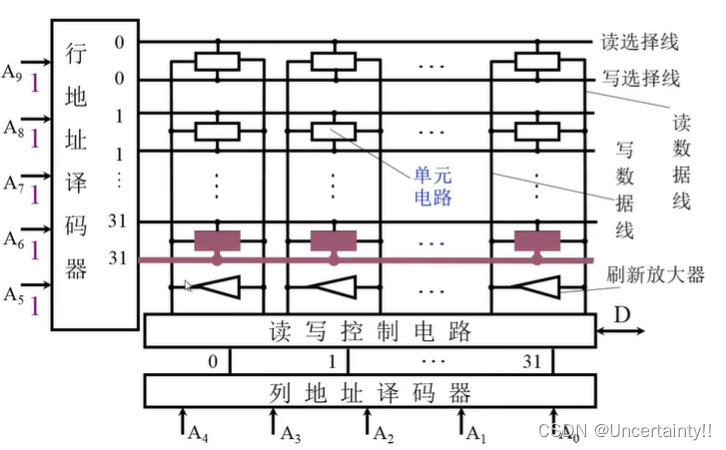

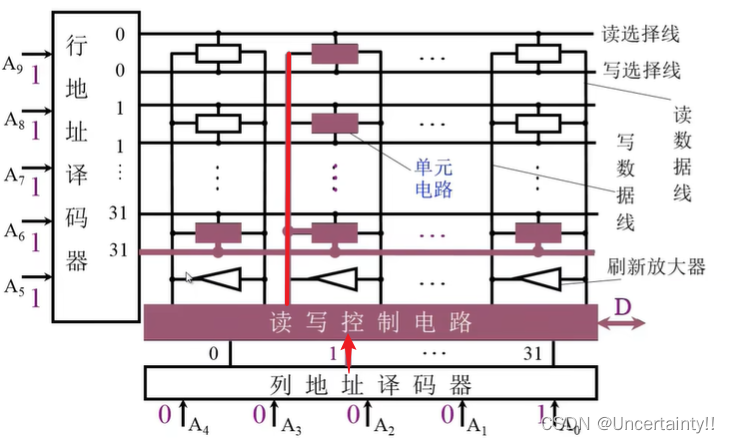

典型芯片的结构是什么样子?

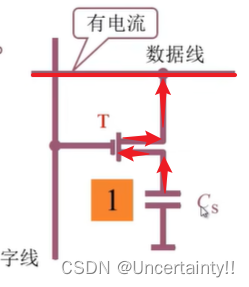

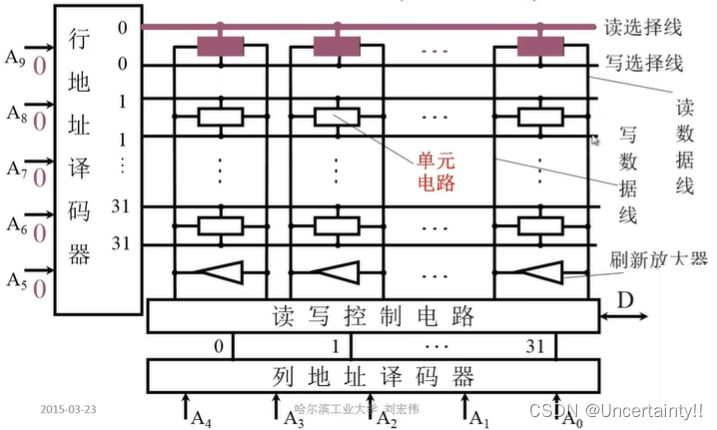

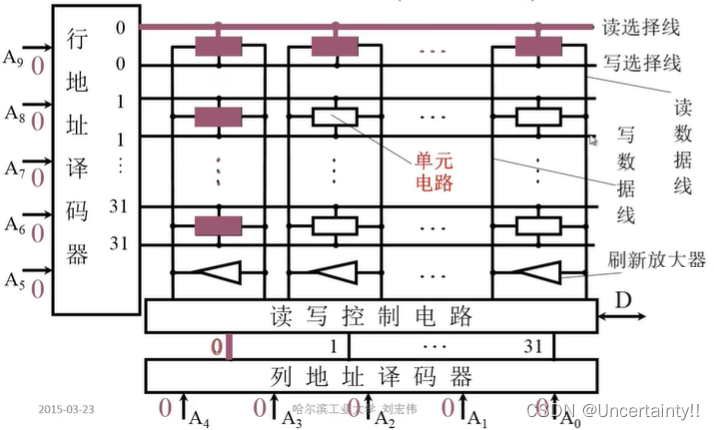

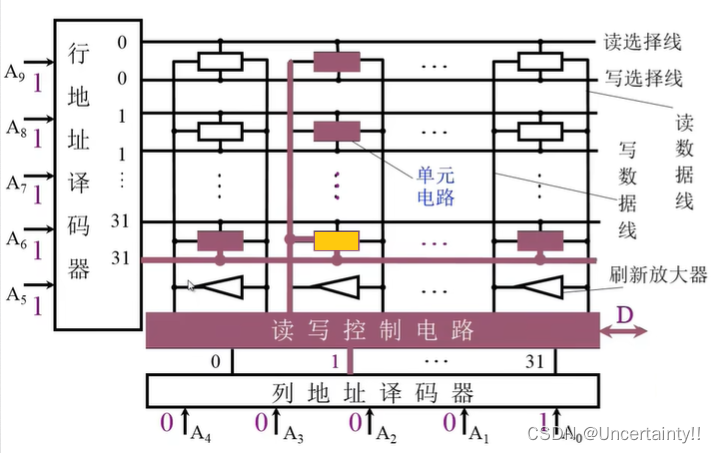

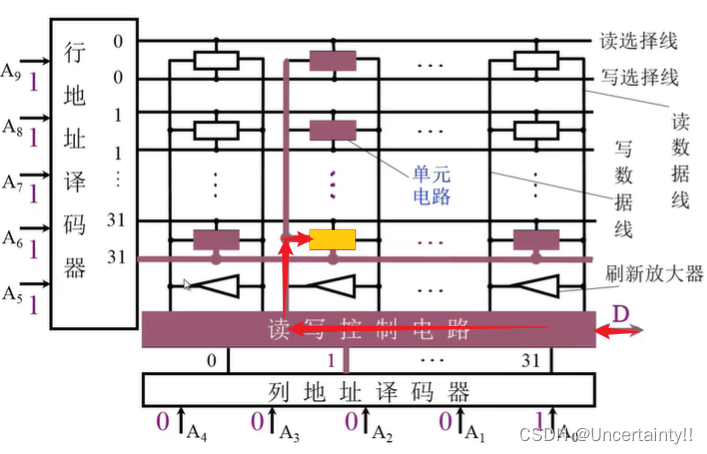

参加译码的不仅是地址同时还有读写控制信号,如果是读信号,则读选择线有效,如果是写信号,则写选择线有效

DRAM芯片如何进行读写操作?

三管DRAM读操作

若行地址全零且为读操作,第0行读选择线有效,第0行所有单元被选中 若行地址全零且为读操作,第0行读选择线有效,第0行所有单元被选中 |

若列地址全零且为读操作,第0列被选中 若列地址全零且为读操作,第0列被选中 |

第0行和第0列交叉点单元被选中 第0行和第0列交叉点单元被选中 |

被选中单元通过读数据线将数据送入读写控制电路向外输出 被选中单元通过读数据线将数据送入读写控制电路向外输出 |

三管DRAM写操作

若行地址全1且为写操作,第31行读选择线有效,第31行所有单元被选中 若行地址全1且为写操作,第31行读选择线有效,第31行所有单元被选中 |

若列地址为1且为写操作,第1列被选中 若列地址为1且为写操作,第1列被选中 |

第31行和第1列交叉点单元被选中 第31行和第1列交叉点单元被选中 |

数据通过读写控制电路送入被选中单元 数据通过读写控制电路送入被选中单元 |

单管DRAM读操作

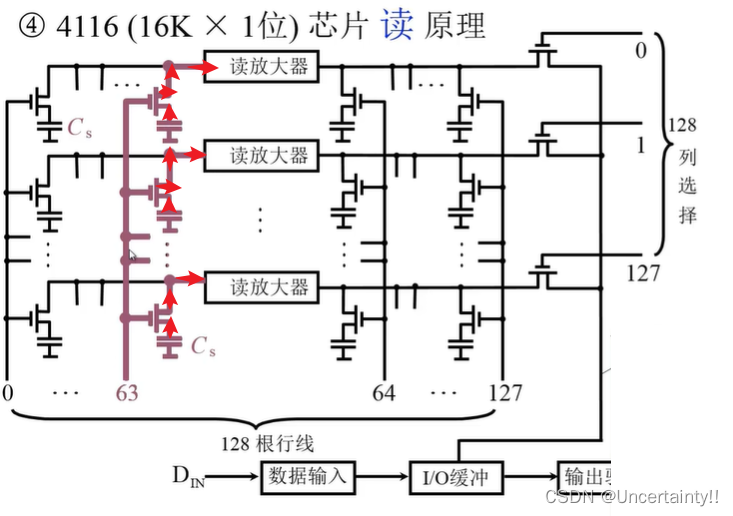

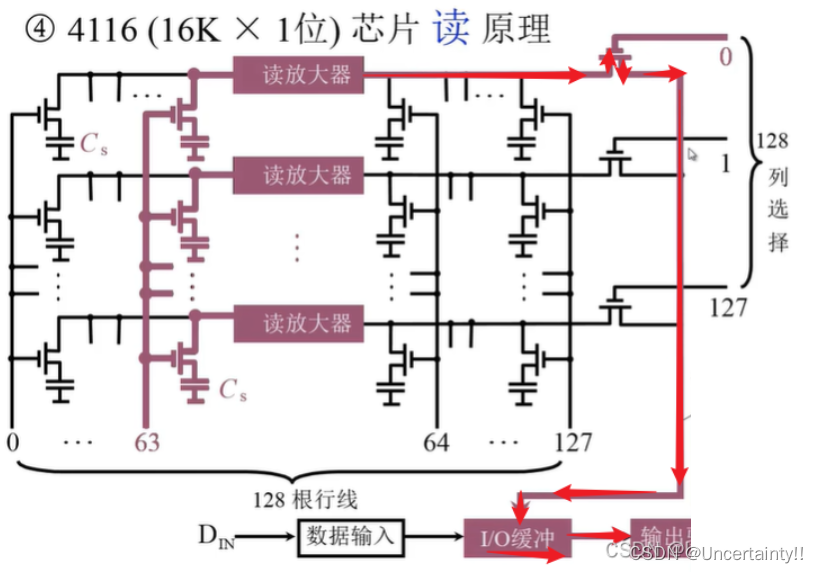

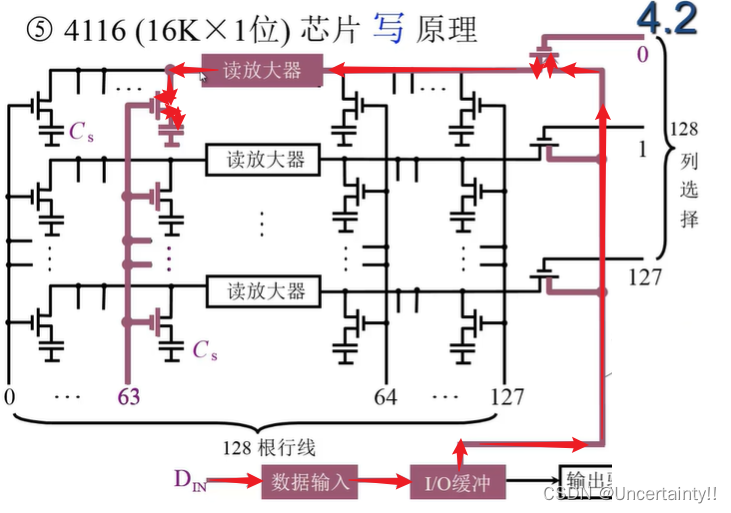

我们关注一下第63行线和第64行线中的读放大器,若读放大器左侧为0,则右侧为1,反之亦然,这是一个“跷跷板”电路

若行地址1个0,6个1即对应第63根行线 若行地址1个0,6个1即对应第63根行线 |

若第0列被选中,则数据经由读放大器到I/O缓冲最终输出 若第0列被选中,则数据经由读放大器到I/O缓冲最终输出 |

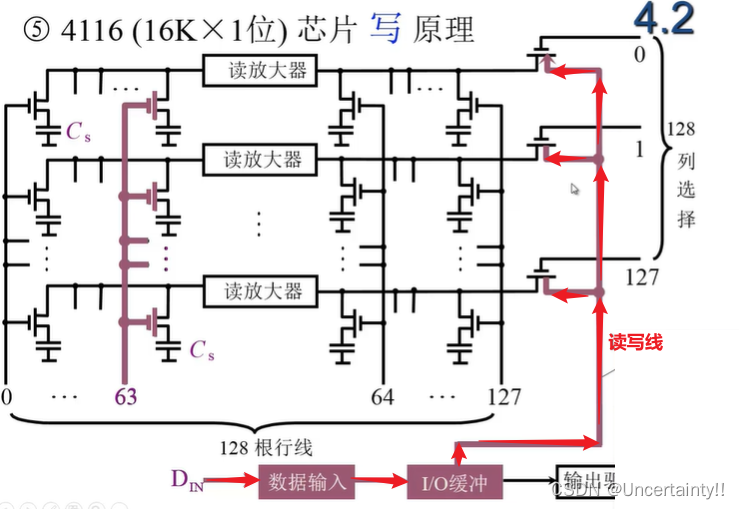

单管DRAM写操作

数据经由I/O缓冲和读写线进入 数据经由I/O缓冲和读写线进入 |

若行地址1个0,6个1即对应第63根行线,第0列被选中 若行地址1个0,6个1即对应第63根行线,第0列被选中 |

综上由于读放大器做了反相,所以读写数据与原存信息一致

DRAM为什么要刷新?刷新的方法是什么?

因为电容会漏电所以我们需要刷新放大器来进行刷新信号防止信号消失

要刷新的话是一行一起刷新,刷新只与行地址有关,与列地址无关

SRAM和DRAM的比较

3.2.4 只读存储器ROM

3.2.5 存储器与CPU的连接

3.2.6 存储器的校验

为什么要对存储器的信息进行校验?

若内存所处电磁环境复杂,空间环境下受到带电粒子打击可能造成电容的充电放电或触发器的翻转,存放在其中的信息会出错

为了能够校验出信息是否正确,如何进行编码?

第一行合法代码集合用3倍冗余方式表示计算机中存储的一位数字,也就是说三位编码000表示计算机中存储的0

第一行合法代码集合中,如果其中一个合法代码的某一位翻转了,则它又变成了另一个合法代码,故无法检测出它发生了错误。

第二行合法代码集合中,如果其中一个合法代码的某一位翻转了,则它没有变成任何另外一个合法代码,故可以检测出1位错误,如果其中一个合法代码的某两位翻转了,则它又变成了另一个合法代码,故无法检测出它发生了错误,综上该编码仅有1位检错能力和0位纠错能力

第三行合法代码集合中,三位编码000表示计算机中存储的0,111表示计算机中存储的1,假设现在收到编码100(显然不在合法代码集合中),而正确编码只能是000或者111,现在出现100,我们猜大概率是1位错且是第1位错了,我们把100纠正为000。假设现在收到编码110(显然不在合法代码集合中),而正确编码只能是000或者111,现在出现110,我们猜大概率是1位错且是第3位错了,我们把110纠正为111。

第四行合法代码集合中,假设现在收到编码1100(显然不在合法代码集合中),而正确编码只能是0000或者1111,现在出现1100,到底是前两位1发生错误了还是后两位0发生错误了,我们不得而知。假设现在收到编码1000(显然不在合法代码集合中),而正确编码只能是0000或者1111,现在出现1000,大概率是第1位发生错误了,我们将1000纠正为0000

纠错或检错能力与什么因素有关?

第一行合法代码集合中,只要其中一个合法代码改变1位就会变成另一个合法代码,无法检测错误代码

第二行合法代码集合中,要想把一个合法代码改变为另一个合法代码,至少需要改变2位。若在存储过程中代码发生1位改变我们就能检测出来

第三行合法代码集合中,要想把一个合法代码改变为另一个合法代码,至少需要改变3位。若在存储过程中代码发生1位改变我们就能检测出来,并知道哪一位错了。{000,111} 假设收到110,大概率1位发生错误,对比正确代码,我们知道第3位错了

第四行合法代码集合中,要想把一个合法代码改变为另一个合法代码,至少需要改变4位。若在存储过程中代码发生2位改变我们就能检测出来,并知道哪一位错了。

任意两组合法代码之间二进制位的最少差异数

检验处信息出错后如何进行纠错?

相关文章:汉明码(Hamming Code)底层原理

3.2.7 提高访存速度的措施

随着计算机应用领域的不断扩大,处理的信息量越来越多,对存储器的工作速度和容量要求越来越高。因CPU功能不断增强,I/O设备数量不断增多,致使主存的存取速度已成为计算机系统的瓶颈。可见,提高访存速度成为迫不及待的任务。为解决此问题,除了采寻找高速元件和采用层次结构cache-主存以外,调整主存结构也可提高访存速度。—引自《计算机组成原理》唐朔飞

单体多字系统

在一个存取周期内,从同一个地址取出4条指令,然后再逐条将指令送至CPU执行,前提是指令和数据在主存内必须是连续存放的,一旦遇到转移指令或操作数不能连续存放,这种方法效果就不明显

多体并行系统(多个独立存储模块并行)

(1)高位交叉 顺序编址

前两位地址是对存储体进行编号,00对应第1个存储体,01对应第2个存储体,10对应第3个存储体,11对应第4个存储体。其余位数的地址对存储体内进行编址。

若某程序的数据连续存放,则首先会存入第一个存储体,可能其他存储体均未存入数据,这就造成第一个存储体忙碌,而其他存储体空闲,无法实现并行工作

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/127096.html