大家好,欢迎来到IT知识分享网。

一、软件介绍

二、设计流程:

1.元件符号原理图

2.焊盘,封装

3.原理图转PCB

4.画PCB

三、Capture CIS画元件符号

打开capture后在想要的位置建立工程文件夹

工程文件结构如下

之后在Capture里建立工程 file-new-proj,给原理图起名字,路径选择工程文件的原理图文件路径

建立原理图库 file-new-library-保存

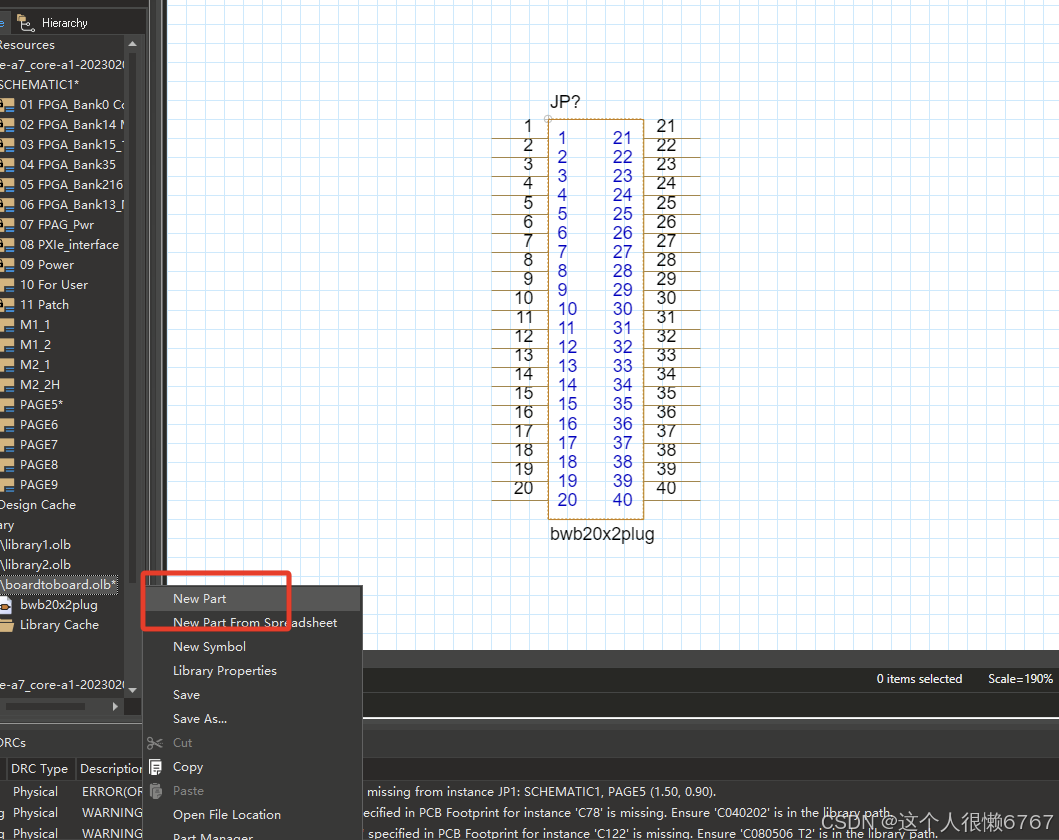

右键原理图库 new part 新建器件

名字和位符

ok后出现如下界面

点击菜单栏place放置引脚

添加矩形边框place

设置参数

四、 制作焊盘

打开·padstack,两种常用焊盘过孔和表贴

文件新建焊盘

R0603的焊盘为0.806*0.864,我们就输入名字smd_0m806_0m864 ,下面那个选择SMD Pin,然后选择路径为PCBLIB文件夹,然后点击OK 记得将路径添加到工程文件PCBLIB中

选择矩型

单位改成毫米

设置焊盘大小

保存 焊盘制作完成

制作过孔 新建 thrupin

设置过孔表示符号

设置过孔参数

保存到pcblib

五、画原理图

回到orcad 新建原理图页

右侧元器件有刚才画的原理图

双击-放置 -esc w连线

双击器件R1 添加封装名字

全部器件填好后导出网表或者转换PCB

首先在SCH文件中建一个Allergo文件

之后在orcad中 导出网表

选择allergo路径

六、画封装

Pcb Editor软件 新建图纸 封装名称0603 选择package(封装)路径放在Allergo里

把刚才画的焊盘路径添加进来

下图三个都改

点击确定后 点击addpin 出现右侧界面

单位换成mm 图纸大小设置200*200 中心点00

应用-确定

设置格栅0.1

选择之前画好的焊盘 设置参数

设置好参数后输入命令x -0.75 y 0 回车 就会在远点附近防止两个焊盘

鼠标右键-取消 可以退出放置界面

之后切换到 package Geometry下的Place_Bound_Top层

点击Add添加矩形

先用鼠标找一个差不多的左下点

然后再切换到Silkscreen_Top层,然后点击add,添加Line,并设置线宽0.2mm,转角90

然后选择合适的点添加线头

查看线头位置-直接输入对角点回车

之后闭合线 然后右键完成done

之后在assembly——top层再添加一个矩形覆盖第一个矩形就行

之后 点击layout-标签-参考位号

电阻封装制作完成

凡yi cadence学习笔记

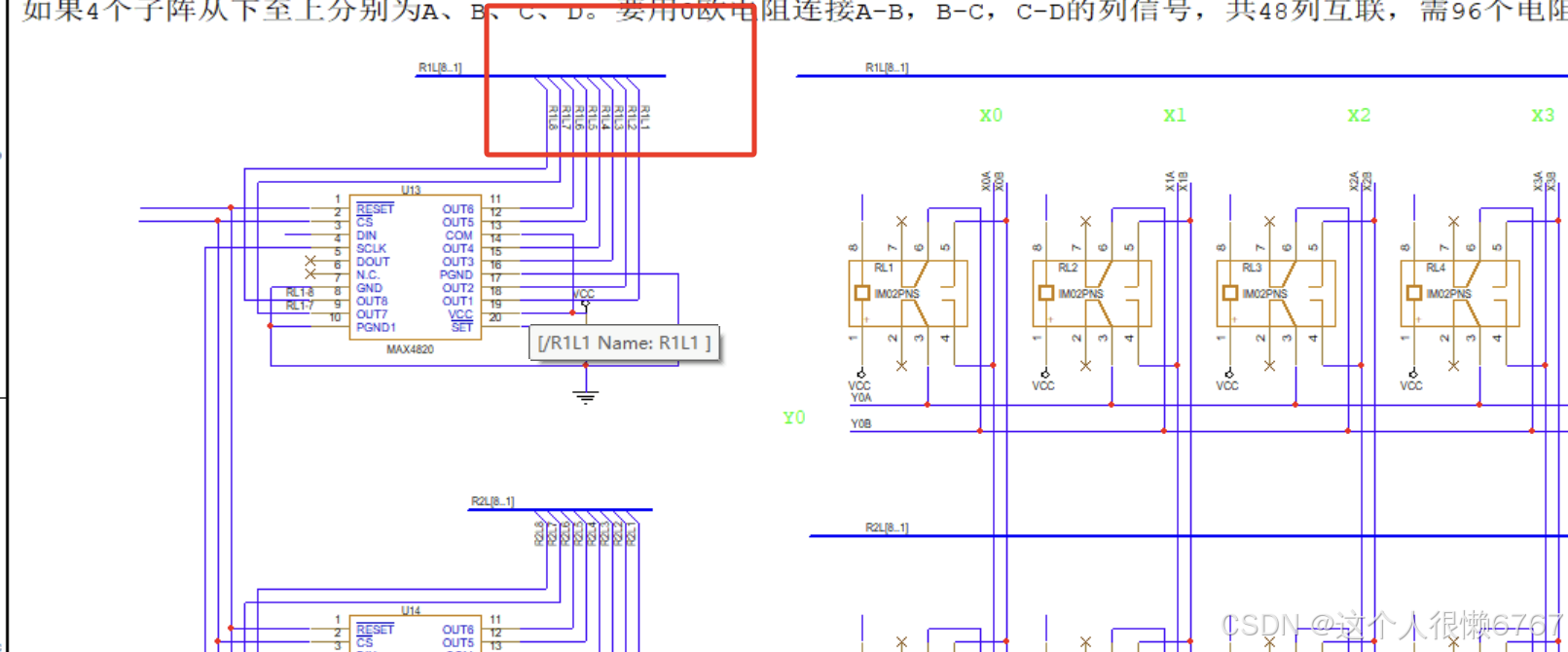

画MAX4820原理图封装

D:\Cadence\SPB_17.4\tools\capture\library 这是自带库的文件位置

新建工程文件结构-orcad添加原理图-添加原理图lib(file-new-lib)-在原理图lib添加newpart

画外型 place retangle

放管脚(放大缩小图纸快捷键 o i)place pin

管脚名称 管教号 放置 放好后点击管脚右侧会出现管脚属性设置

一般就两个type常用 电源引脚和无源引脚

不太好看

也可以place pin arry

之后编辑引脚

完成 保存出现报错

原因是PGND有两个 重复了 解决方法 将 GND网络的tpye全改成Power这样就可以重复name了

保存到SCH路径

在原理图添加本地库

再画一个继电器

隐藏pinname 画线

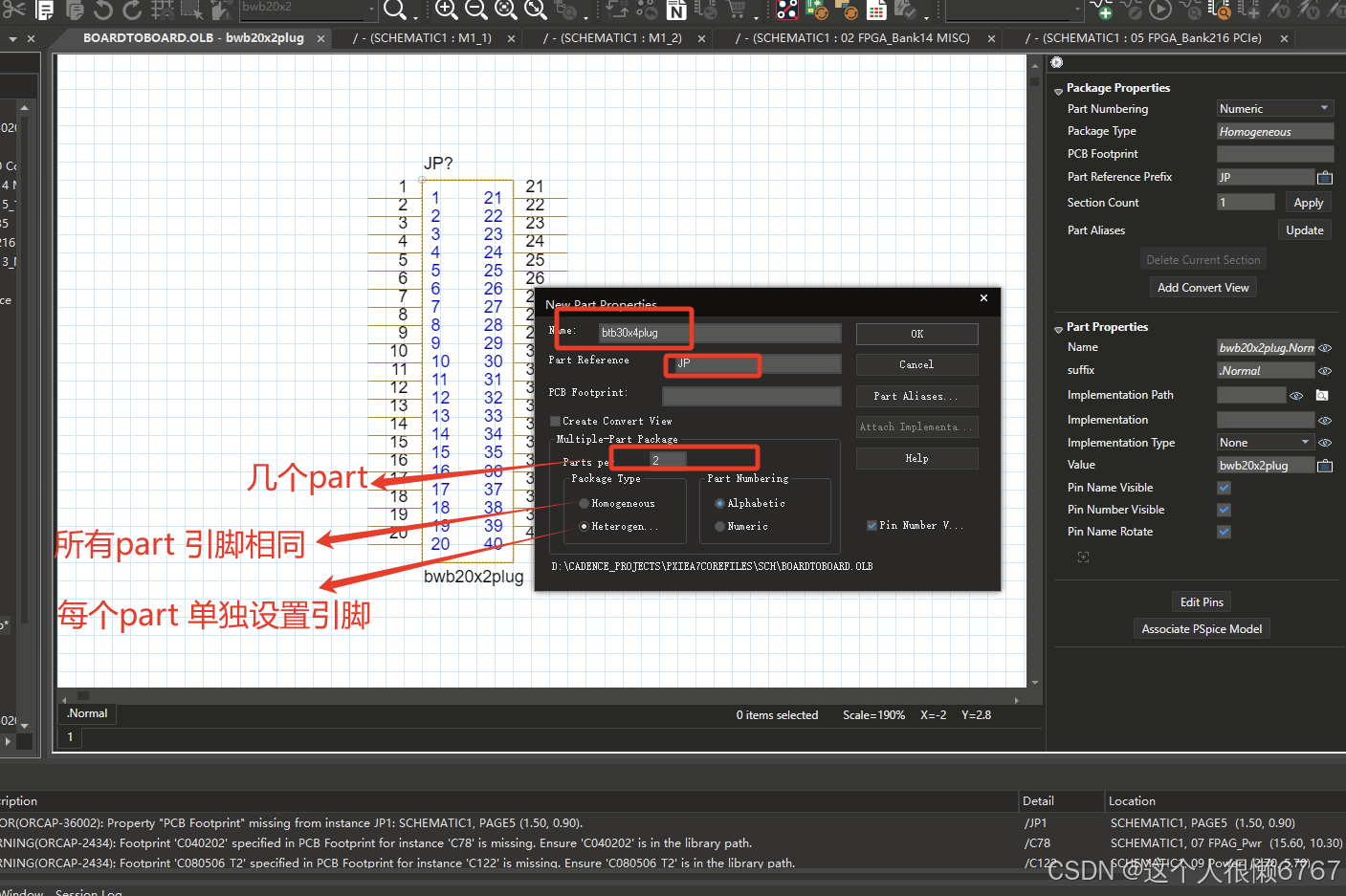

多part封装

画原理图

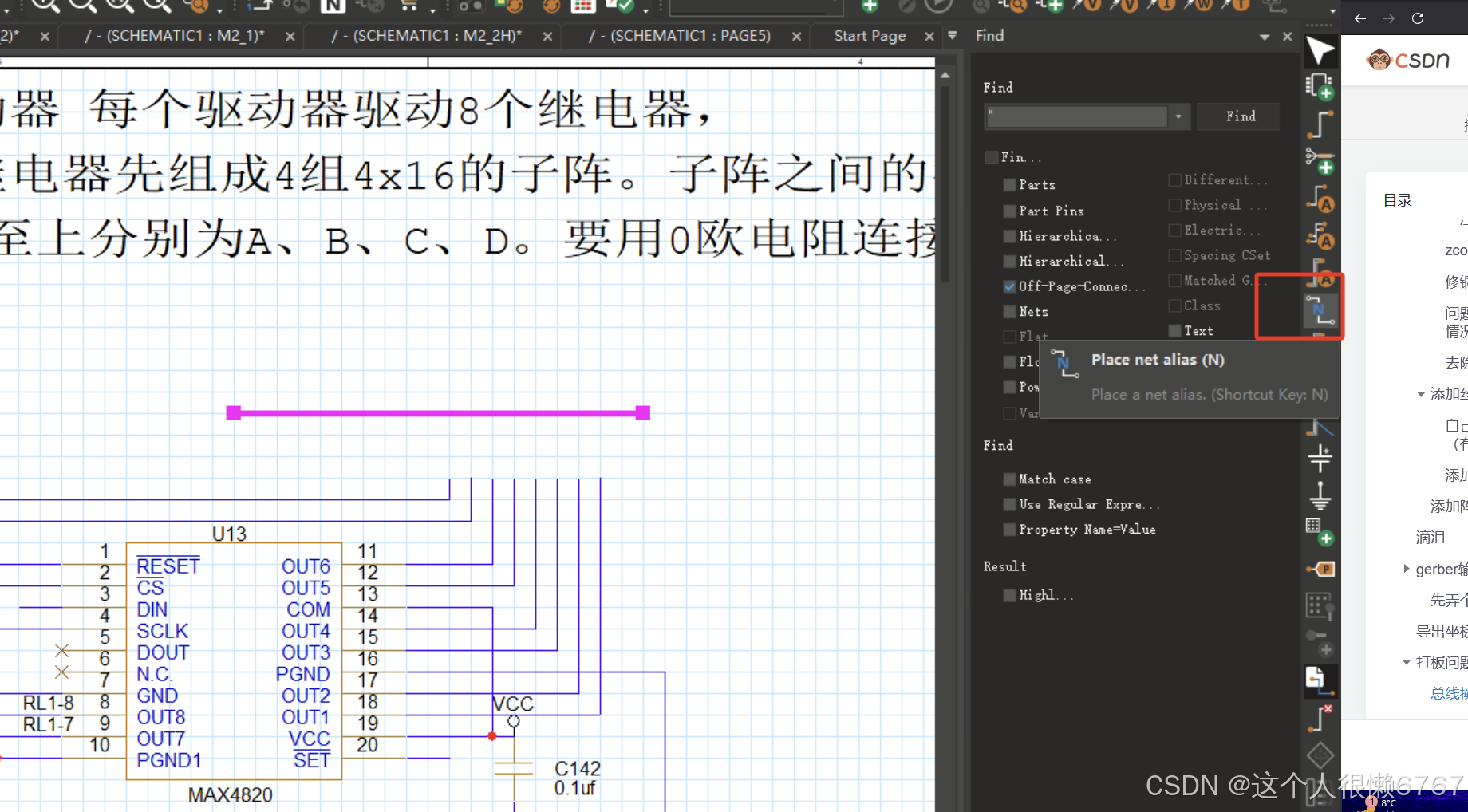

在修改某元件schlib之后再放置会出现报错

ERROR(ORCAP-1228): Cannot place part ‘lM02PNS” from library”D:\CADENCE PROJECTS\RELAWSCH\LIBRARY1.OLB’ because the librarypart is newer than the part in the design cache. Select the part in thecache and choose Design -Update Cache, and then place the part again.

解决办法 updata cache

设置纸张大小

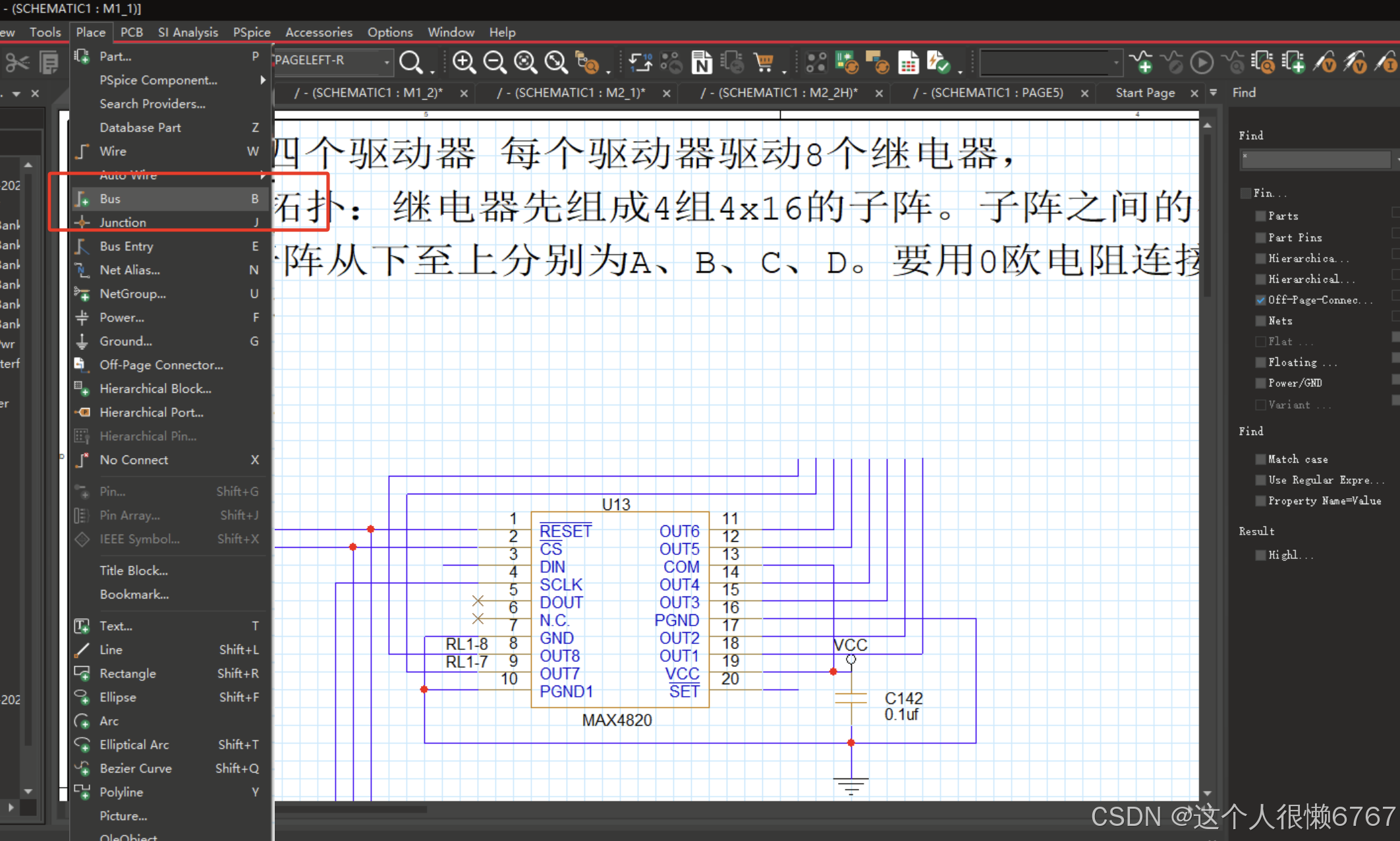

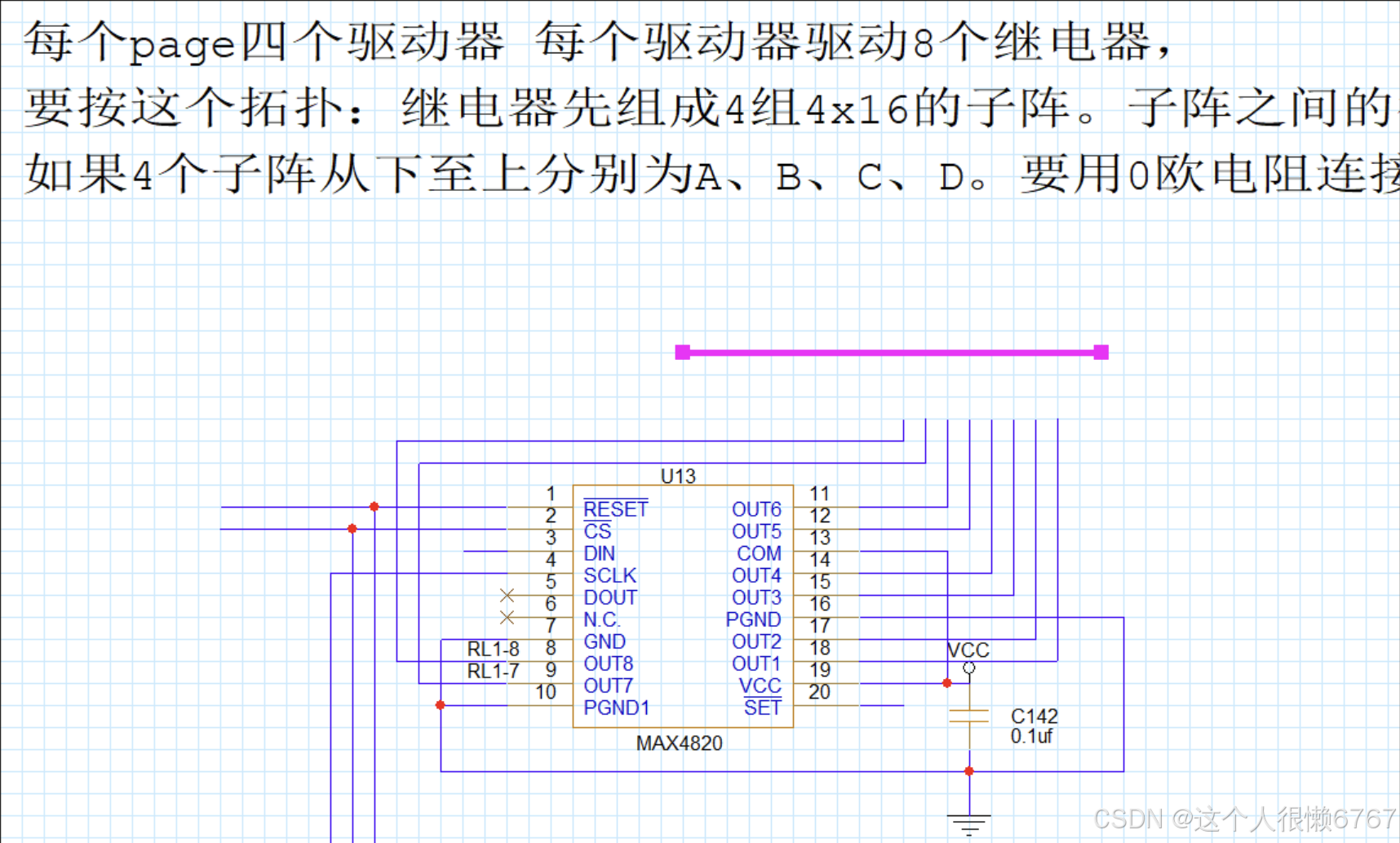

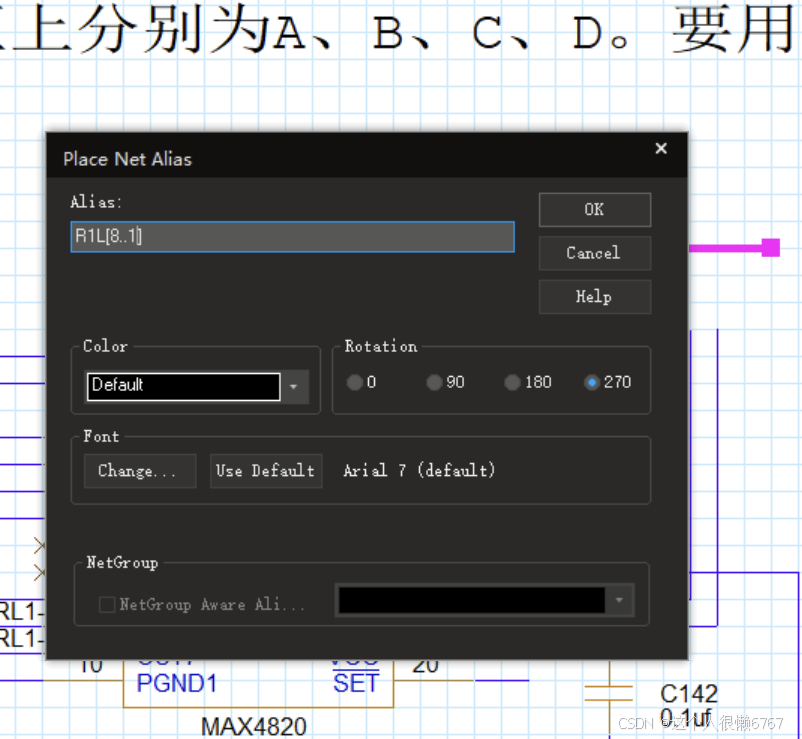

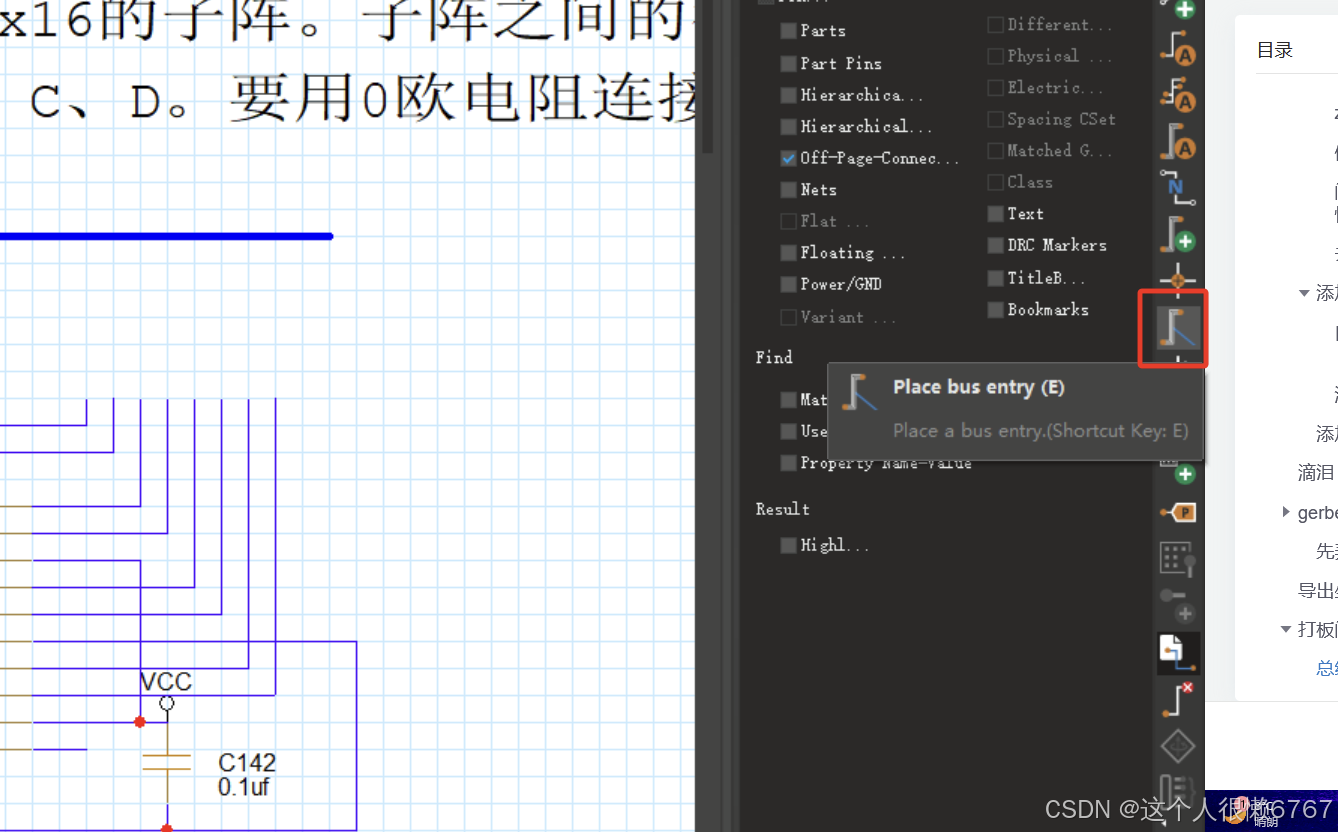

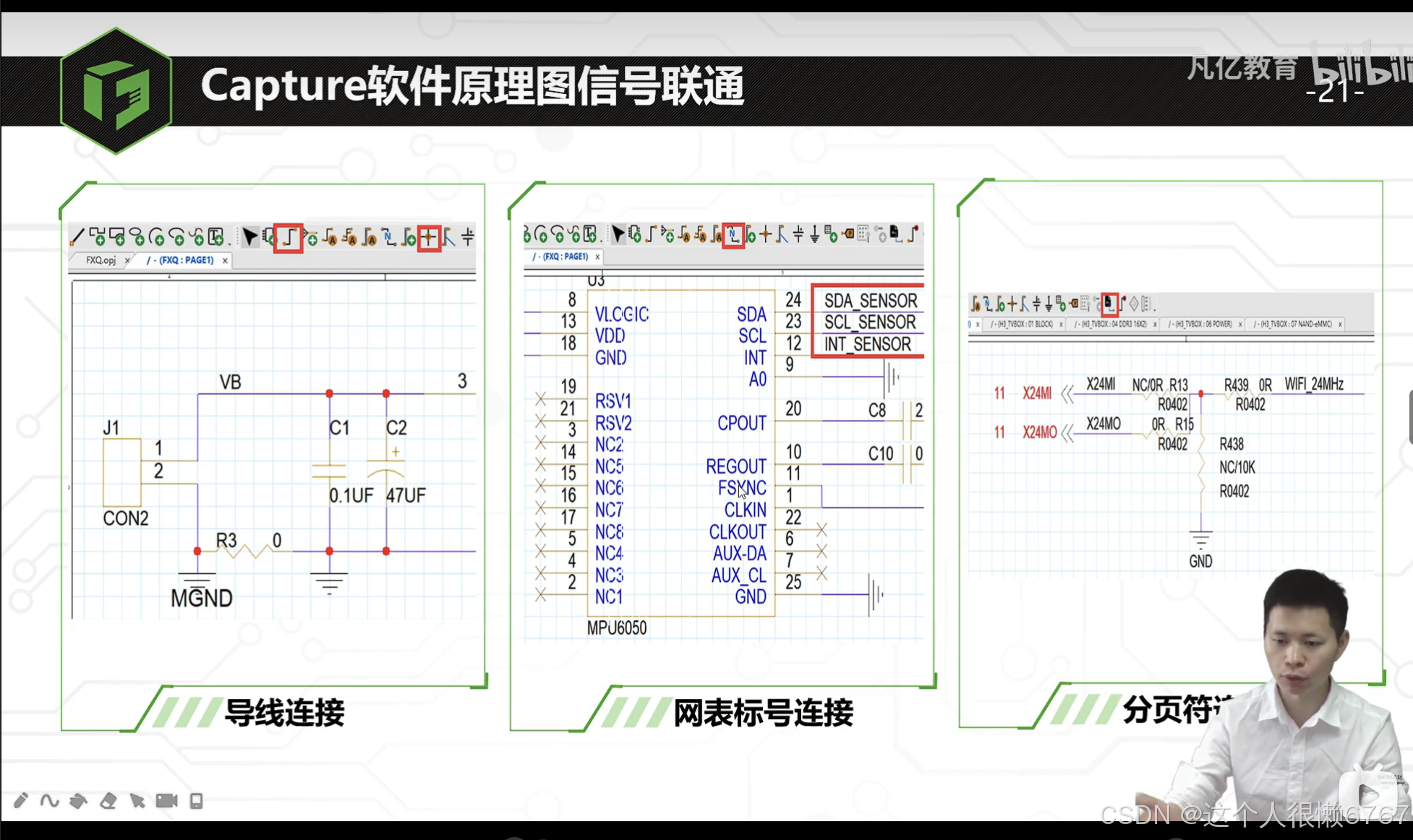

导线连接 网表标号连接 分页符连接

添加差分对 选中原理图页 上边导航栏 tools 添加差分对

绘制好原理图后 进行footprint处理 添加footpin name 一定要记住 后期画焊盘要对应上名字

注意 footpin命名不能有.\`之类的奇奇怪怪的符号 否则DRC报错ERROR(ORCAP-36071): Illegal character “Dot(.)” found in “PCB Footprint” property for component instance

之后DRC

DRC奇怪的报错 PGND短路报错WARNING(ORCAP-1589): Net has two or more aliases – possible short

解决方法 再SCHLIB中把所画的芯片PGND引脚改成passive属性,不用power了,并且将多个PGND分别标号PGND1\PGND2……否则会出现重复pinname报错。。。

输出PDF

BOM表

需要手动添加 PCB Footprint 格式是 \tPCB Footprint 以及\t{PCB Footprint} open in excel打勾 然后点击ok

输出网表

这个用于后续画pcb

路径放在SCH 的allergo里

画PCB

创建贴片封装

SMD引脚焊盘

填写引脚焊盘参数 即单个引脚的长宽,并且适当补偿,选取最大值就完事了

阻焊宽度一般是常规焊盘尺寸+0.15mm 0.1mm也行

贴片不用管soldemask bottom PASTEMASK TOP是钢网 可以添加一个 尺寸就是常规焊盘的尺寸

制作完成 保存到工程文件的PCBLIB中

之后制作中间大焊盘

中间大焊盘直接用尺寸最大值就行、

阻焊和钢网

之后打开PCBEditor 绘制max4820封装

新建图纸 选择路径为PCBLIB

设置参数

添加刚才画好的焊盘

通过封装PDF计算1引脚的起始位置(中心点对0,0的相对位置)

之后画装配线 丝印线

SMD 丝印画拐点就行 照着装配随便画一下就行

添加位号字符

位号 #REF

装配号 #REF

VALUE值 #VAL

占地面积

比芯片稍微大两个grid就行

器件最大高度

点击器件边框 添加最大高度完成

保存 生成 psm文件 在 PCBLIB路径

画通孔封装

直径 是0.4

这个 可填可不填

中间层 和结束层 一样0.8

左侧热风焊盘 右侧反焊盘

为了方便正负片都能用 一般做通孔会把 热风和反焊盘加上 (只需要中间层加)

反焊盘的规则 drill size + 0.8

热风需要用PCBEditor 制作flash文件 flash 规则 重点内径和外径

打开 PCBEditor 新建 flash symbol

保存后 在 PADEditor中调用

如果刷不出来热风焊盘 回到 PCBEditor中重新指定一下path 然后保存 再回到 PADEditor中查看

阻焊层 比钻孔焊盘大0.15mm

比如说regular pad 0.8

那么 阻焊就是0.95 由于是插件 top bottom都要阻焊

保存

新建PCB文件

导入网表

导入完之后都是192警告,可以先忽略,因为没有指定封装。

no errror就行

查看状态

有这个信息说明导入成功,

下一步 把元器件从后台放过来

下一步 把元器件从后台放过来

指定封装库路径 用户偏好设置 path

重点 SCH中的footprint 一定要和画封装后导出的PSM文件名字对上 建议都是小写

正常来说点击放置后的这个界面 未放置的symbol和放置的symbol数量应该是一样的 这里面少了一个 看一下导入网表后的报错

在网上找的allergo封装 可以打开dra文件导出库 在PCBLIB路径 这样放置时就不会报错了

下面这个报错 是在IC封装网导入了一个4p的排针,并且已经在dra文件中导出焊盘文件了 还是报错

不太清楚为什么,因此自己画一个4p排针注意命名 完成后再次导入网表 没有报错

放置

放置不了 出现报错

查看日志

解决: 图纸太小了 把图纸改大一点

效果

修改原理图更新布局

在sch中添加器件修改布局后,将新添加的元器件footprint填好,生成网表。然后弄新器件封装(画或者下载)之后将封装dra文件命名为footprint同名,然后进入封装dra文件中 文件-创建symbol-导出封装psm文件(命名也是footprint)

之后进入layout的工程中(之前已经导入过旧版网表)点击更新布局

新的器件就会生成 然后点击放置 就会发现有新的未放置symbol

画板框 在Design outline层

隐藏地或电源网络操作

最后的效果是这样

要是想显示出来

3v3网络同样

几个有用的显示层

移动 旋转 对齐 等间距 镜像

对齐

布局模式开启或关闭

布局模式开启或关闭

信号线上百M之后需要控制阻抗 需要根据层叠做阻抗计算

pcb结构文章

http://t.csdnimg.cn/UXN4i

设置叠层 1mm =39.37mil

mil单位数据如下 一般都用mil单位 需要注意 gnd和pwr设置成plane 选择 1oz cooper

加一起差不多1.6mm就行

调节线宽计算阻抗 阻抗都控制在50ohm左右就行

右侧是差分线线宽 阻抗一般控制在100ohm

过孔设计

贯穿层-换层

1、通孔 (贯穿)2、盲埋孔

下图过孔选择是内径

外径(焊盘)

过孔lib下载下来了 做项目直接调用就行

带f的是常规盖油过孔 不带f的是开在焊盘上的过孔

allergo添加过孔需要指定flash焊盘路径,在用户偏好设置下 path 这两项 添加过孔文件路径

之后

进入之后找到physical中的vias

往下翻

选个10F和12F(10mil 12mil) 双击就可以移到右边

然后点击ok

之后 点击走线命令 在右侧选项处就可以看到添加过孔的选项

拉到位置双击左键添加过孔

过孔扇出方式

删除线 删除过孔 选择不了目标的问题

选项中勾选 右键就可以删除了

allergoPCB中也能添加差分对

针对比较多的差分管脚 采用差分对模糊添加的方式 但是需要原理图比较规范 有同样的后置结尾

布线规则添加

在这里选择驱动 如果修改Default规则就不用再选取驱动 因为默认的走线规则都是Default

有时电源需要宽线宽 因此添加电源规则POWER

命名为POWER线宽最小15mil

之后在Net中给电源网络添加驱动(gnd vcc vdd 。。。。。)

这样走Vcc时就是15mil了

NACK规则是用来走BGA等比较密集的器件

添加到default就行

nack一般比常规走线细一点 长度不超过100mil

走线的时候需要nack模式时 右键选择即可

差分规则

创建新规则 命名deff_100

线宽4.1 线距8.5

之后给差分线选择deff_100驱动

间距规则添加spacing

一键修改所有间距 6mil为例

特殊的再单独修改

line to line 8mil

铜皮shape to all 10mil

line to xxx shape to xxx是重点需要关注的

另外 有些走线需要单独设定的 创建新的规则就可以了 比如说创建一个差分信号线距离其他元素20mil的规则

之后在NET处将spacing规则驱动添加进去

添加class 统一设置驱动规则

进入规则管理器 的phy 或者spacing 的NET

按住Ctrl鼠标选择要归为一个class的网络 如电源网络 右键creat class

这里要勾选

创建后 class中的内容通用一个规则

颜色分配 方便布线分析 不同网络不同颜色

先选择网络(引脚) 点击调色盘选择颜色

区域规则添加

区域规则用处是,在整个板子的规则线距12mil时,可能有些器件引脚出线小于12mil,若不添加区域规则DRC会报错。添加区域规则可解决这种问题。

添加方法略,暂时用不到。

走线修线

1.走线

参数面板

alt模式下 上边是默认走线层,下边是打过控制后的走线层

一般走线设置就这样

修线(推挤)

查找面板也很重要,比如说推挤想要过孔不动,那么需要在查找面板取消过孔勾选。许多操作都可以修改查找面板,他是选择操作面向的对象。

开始走线,记录一些细碎的操作

由于四层板电源GND不用连,电源pin旁边打个过孔就可以,注意过孔层TOP-PWR/TOP-GND

另外,过孔大小多添加几个电源15mil线 过孔内径至少也要15 在规则里改过孔大小

测量命令

查询操作

删除板框删除不了

板框添加了锁定属性 解锁就好了

z-copy操作 画package keepin 和route keepin

首先 打开zcopy操作

调参数 先画route keepin

跳完参数之后 点击 design outline 的线 route keepin自动就画好了 黄色就是 route keepin

同样的 package keepin 只需要在参数处选择package keepin就行 剩下的操作和 route keepin 一样的 。。。 package keepin 是放元器件区域

内缩量看实际需求 板子宽松就内缩量大一点

z copy还有一个功能就是 覆铜的铜皮顶层和底层一样的话也可以copy 参数先记一下 还没画铜皮

铺铜操作

动态参数设置

这个是铺网格铜用的 暂时用不上

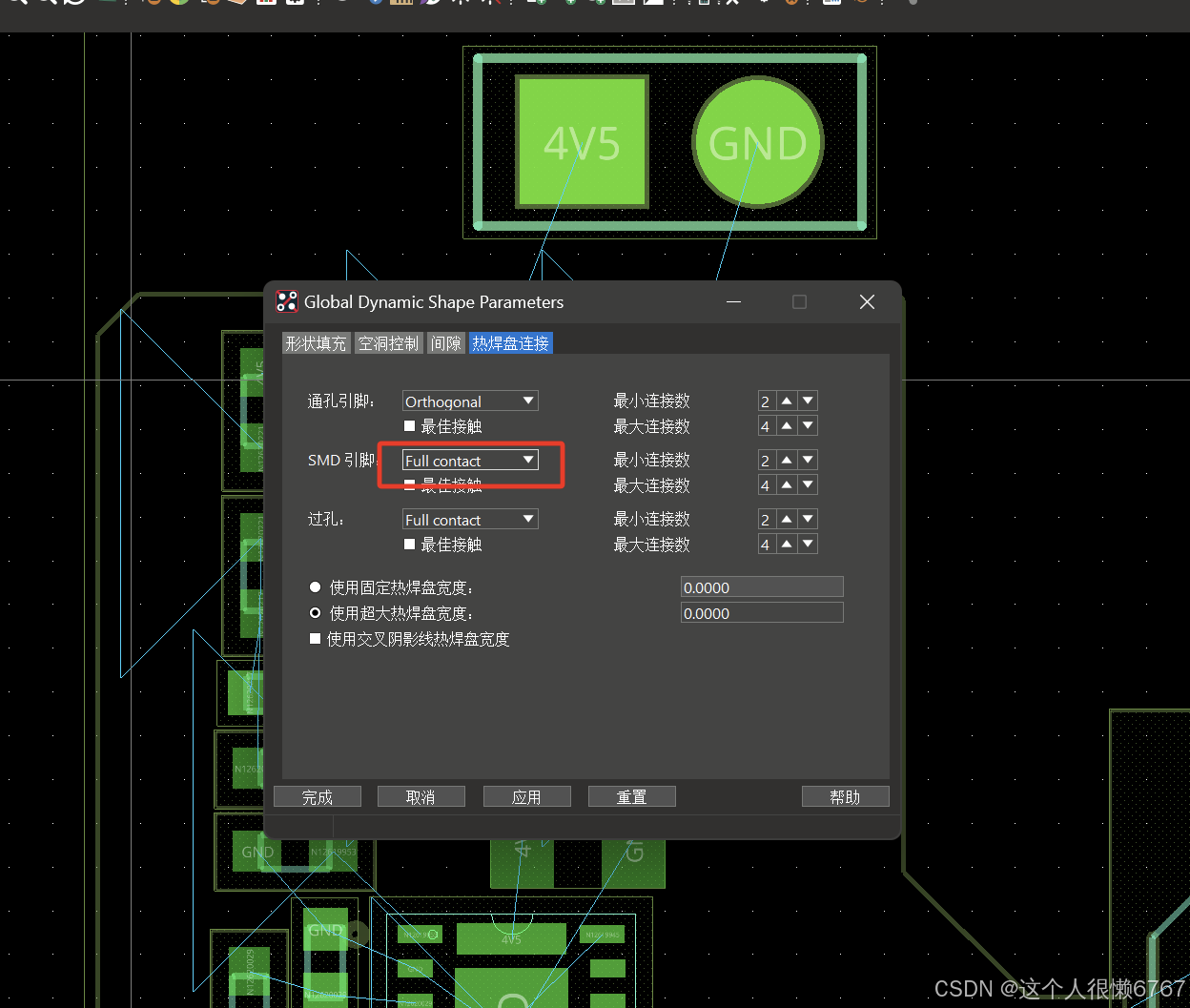

过孔以及铺铜边缘处理

热风焊盘

SMD全连接

表层电源模块(3v3 5v)需要单独铺铜

铺铜命令在这里

以gnd为例

如果先画形状 后指定网络的话 需要在shape – 指定模式下选择铜皮然后赋网络

电源网络铺铜后需要打过孔以增加连通性 过孔后续再说

注意 过孔焊盘不显示问题

之前是这样的

zcopy操作大面积铺铜

之后选择 package keepin (也可以选别的线 )

下一步为铜皮选择网络

进入shape select模式后(在这之前动态参数都已经设置好了) 调参数(网络 层之类的)

点击刚才画好的铜皮 完成

同样的zcopy 底层铺铜 底层铺铜的时候有时候选择不到底层的铜皮

可以在调色盘里先把etch层的top层先取消勾选(不显示)

另外 不要额外给gnd或者power加颜色 画出来的铜皮会非常奇怪

顶层和底层的etch(电器走线层)铺完铜之后的效果

修铜(挖铜)操作

这种铜可以修一下

问题:如果出现挖铜没反应的情况(并且伴随着画了很多shape 没反应 留下了白色的shape框)

1. 不能挖铜:

选择平滑

2.之前画的shape如何删除 打开手动的delete模式

把鼠标放在要删除的shape上 直到出现下图黄字,然后左键两下就删除了。

除孤岛 删除后会有绿线 void bottom(top) gnd

改为静态铜皮就没有了 最后都要改为静态铜皮

static

铜皮合并

铜皮分割(anti etch)

假设说gnd和agnd要做电源分割 addline

一般来说 电源分割所有层都要分割 所以选all 也可以选择单独层

画好分割区域

创建分割平面

可以先不选网络 一会儿再赋

之后赋网络

选择区域

右键 分配网络

注意 有的时候点击shape select选择不到plane层的铜块 总是选到top层

解决办法:在可见性中将所有层全部关闭 只开plane层(gnd02 或power03)

之后删除anti etch

删除铜皮操作

选择 要删除的层的形状 delete(快捷键c)就行了

另外内电层不需要分割的直接铺铜就可以了。

去除孤岛时报错

并且状态中 无法更新

先去除孤岛再更新

画完power层 未分配形状增加了

这个问题没找到解决办法

把四层每一层都重铺了一下 每铺一层都检查一下状态 最后没有未分配形状了

添加丝印

预先设置字体

编辑-更改

选项中选择文本块2

框选板框

自己额外给元器件添加丝印(有些封装没有ref des的丝印标号 导致画完板子没有丝印层的ref)

调参 注意我们要给元器件添加标号丝印因此选择ref des 的silkscreentop

这个丝印文本不能随便添加 需要点击symbol 然后弹出输入框后 输入丝印

添加图形 线 自定义的文字

添加图形 线 自定义的文字

自定义的一些内容添加到board geometry 的丝印top

添加阵列过孔

几个需要注意的参数

选好铜皮 右键 放置

tips:阵列过孔放置完之后可以单独删除某个过孔

并且 放置空旷的地方可以自己复制单个过孔 粘贴到想要的位置

滴泪

一滴泪覆铜炸了

太扯淡了

gerber输出

gerber文件所需的内容

fany skill一键输出gerber

先安装

上面参数不用动 点击set

点击 参数和光绘层叠

然后点击creat就行 出现这个警告 点击yes就行

导出gerber文件会在PCB文件里有一个文件夹 里面是这样的 最重要的是CAM文件

点击制造-光绘-查看日志发现有很多警告 一共是这两种

1. 出现在top和bottom层

WARNING: Segment with same start and end points at

(544.535 919.291) will be ignored. Increasing output

accuracy may allow segment to be generated.

2.drill文件

WARNING: 0 width line found at (600.000 -1750.000) in MIL

… using undefined line width of 6.000 MIL

不知道怎么回事

先弄个cam350查看一下

cam350有点抽象

用华秋DFM看一下

cam文件里的全部打开就行了

跑dmf有错误

按照报错修改一下 重新输出gerber文件就好了

导出坐标文件

注意 画元器件封装时,操作规范是将原点画在器件中心,这样导出坐标文件的时候只需要选择symbol origin就行了

打板问题

fanyskill输出gerber没有design outline 打板的时候嘉立创说没有边框 华秋dfm也检测不出来边框

自研解决办法

前提是用凡亿的fanyskill已经输出了光绘文件(CAM)文件已经存在 就是里面少了outline.art

保险起见 先点击design outlin的边框选择上 然后点击编辑-更改(change)把线宽改成6mil或者0.1mm

然后

调色盘全关 只开design outline

然后点击制造-光绘

在这里新加一个文件叫outline 建完之后会发现outline文件里边有board gometry的design outline

然后在outline的左边白框打个勾 然后创建光绘 注意 修改右边的未定义线宽为8mil(非0就行)

然后点击查看日志 能看到文件输出在哪里了

找到这个文件 剪切到fanyskill输出的光绘文件中的CAM文件夹

这个文件夹就是最后的gerber文件

过一遍华秋dfm

有板框尺寸了

使用SMT功能时

PCB输出的place文件不用改.TXT直接上传就行

orcad输出的bom表是.BOM型文件需要手动改成.xlsx文件 然后按照下图修改一下excel文件就行了

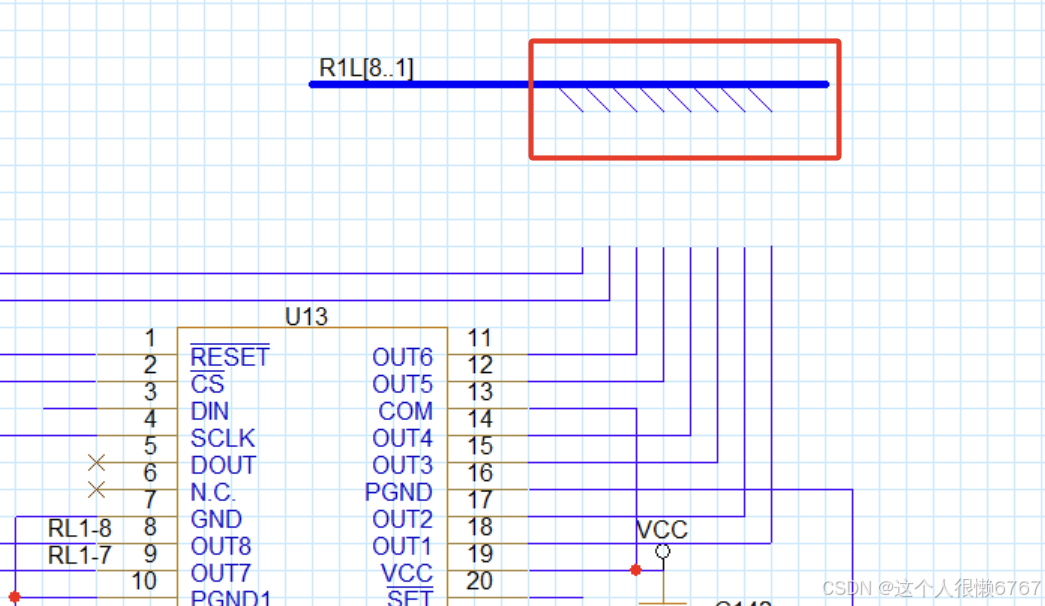

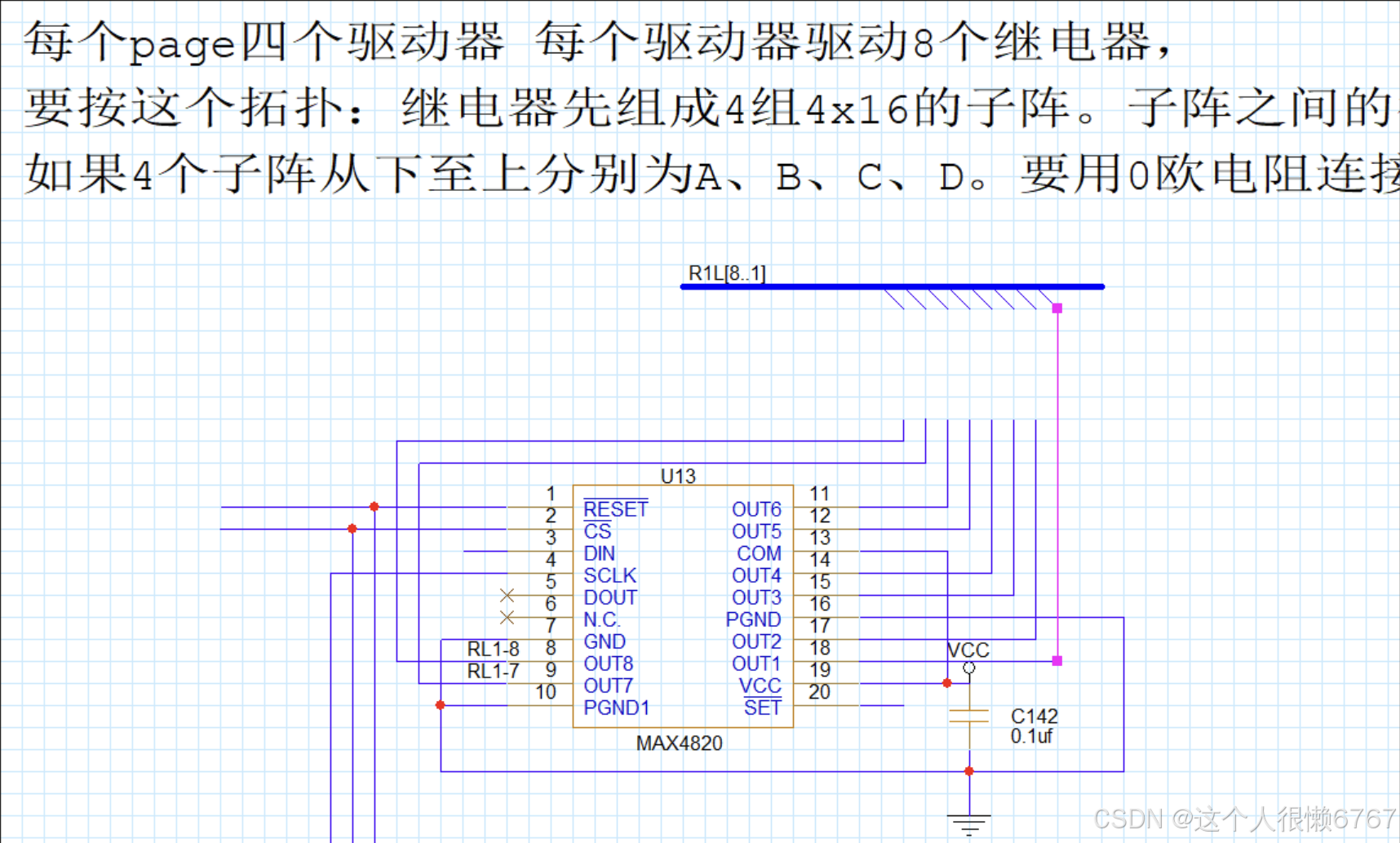

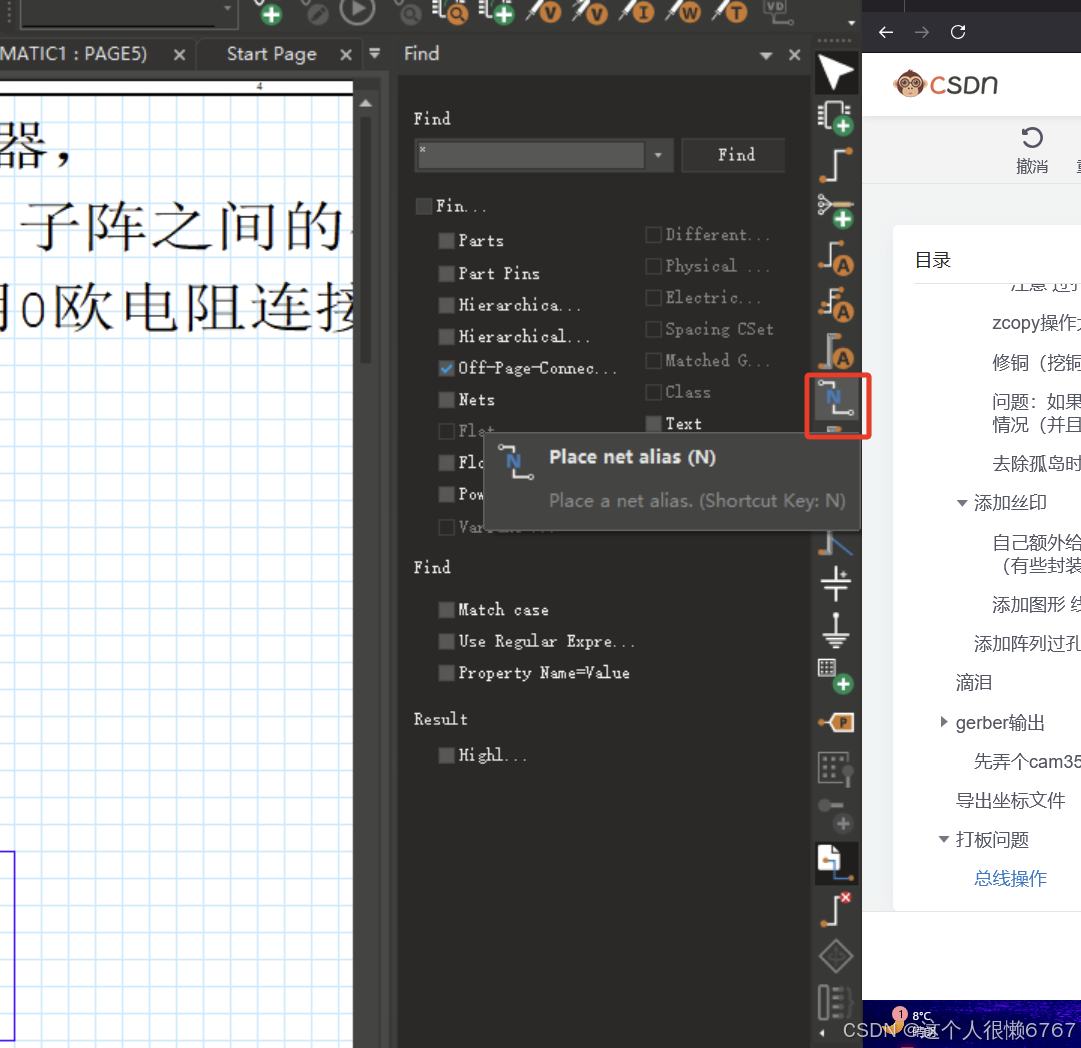

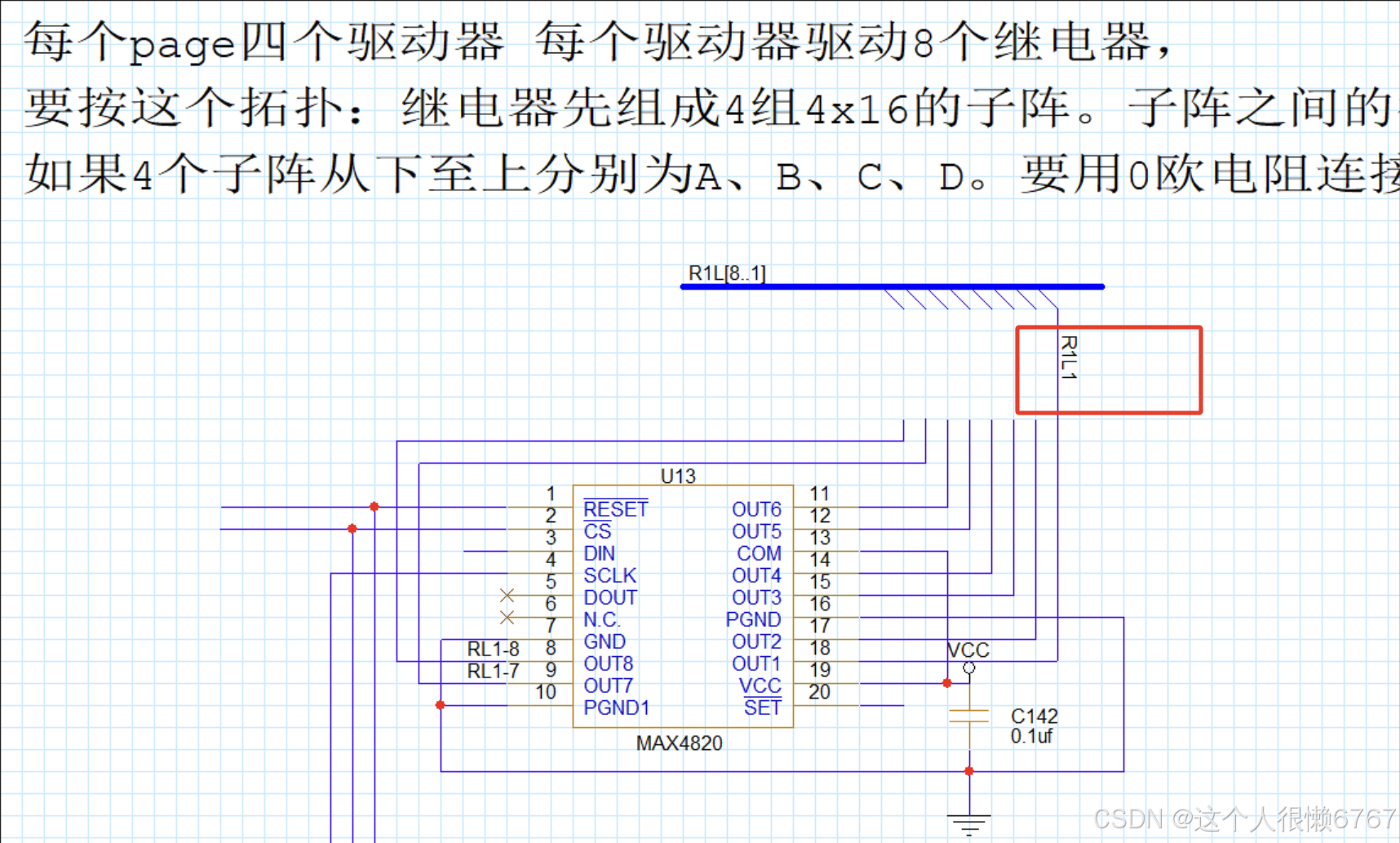

总线操作

命名规则1.不能以数字结尾 2.[大到小]

用w 连一根

给上标签

之后按住ctrl托R1L1

注意 有的网上下载的SB封装lib 不给画soldmask,

得亏我用DFM软件看了一下焊盘

解决方式 ,在原理图或者Pcb文件上找到该封装的文件地址,将该封装的dra文件中对应的pad文件修改一下,手动加上soldermask层,smd一般就是长宽全加0.15(相对于常规焊盘尺寸)

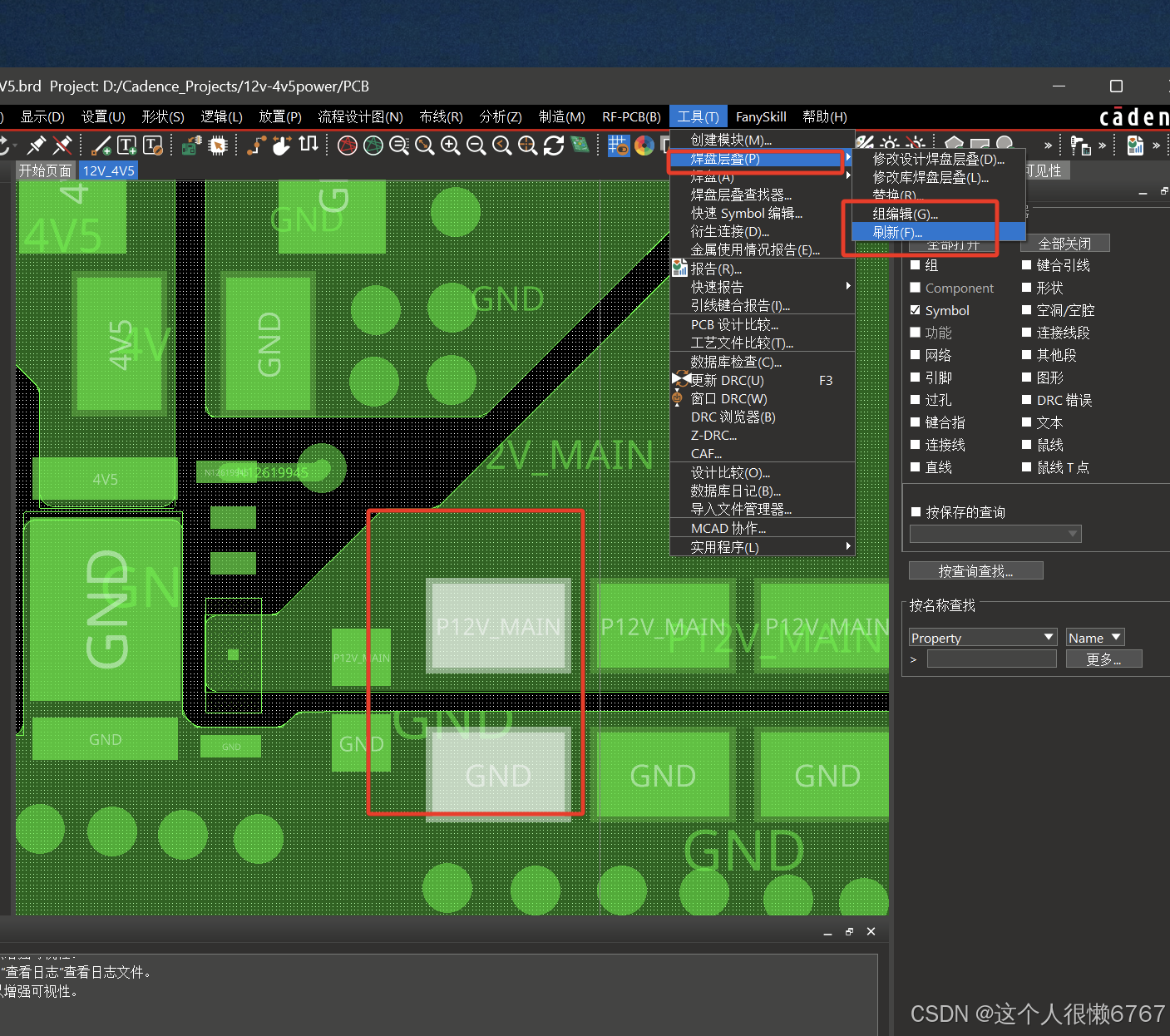

然后进入allegro 点击该symbol 刷新

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/132761.html

下一步 把元器件从后台放过来

下一步 把元器件从后台放过来

布局模式开启或关闭

布局模式开启或关闭

添加图形 线 自定义的文字

添加图形 线 自定义的文字