大家好,欢迎来到IT知识分享网。

SpyGlass,这是一个很强大的RTL验证级工具。它不仅仅能检查sdc的错误,还能做以下各种检查:Low Power, DFT,CDC(Cross Domain Check)。

一、基本概念

1、方法学相关

- Rule: 是SpyGlass 进行RTL分析的最小单位.

- Goal: 是一系列相关Rule的集合,组合起来完成RTL分析的某个特定任务. user可以用GuideWare定义好的Goal, 也可根据工程项目要求来选择一系列rule的集合形成自定义Goal. GUI里面点Goal的button来选择设定, 当然也可在Prj file 里定义.

- Sub-Methodology: 是一系列相关Goal的集合, 用以达成某方面特定目标, 如完成CDC check.目前包括 SpyGlass CDC/Constraints/DFT/Power/TXV Methodology2

2、 其他

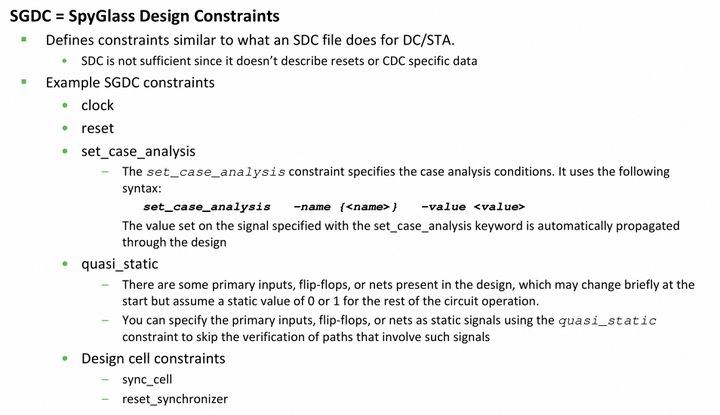

- SGDC : Constraint 文件, 主要包含clock和reset等约束信息.

- Waiver : 用以过滤一些结果的文件.

- Severity : report结果中分Fatal, Error, Warning和INFO四等级信息.

- parameter: 可以在进行RTL分析之前设定某些参数, 对检查过程进行一些约束

二、流程简介

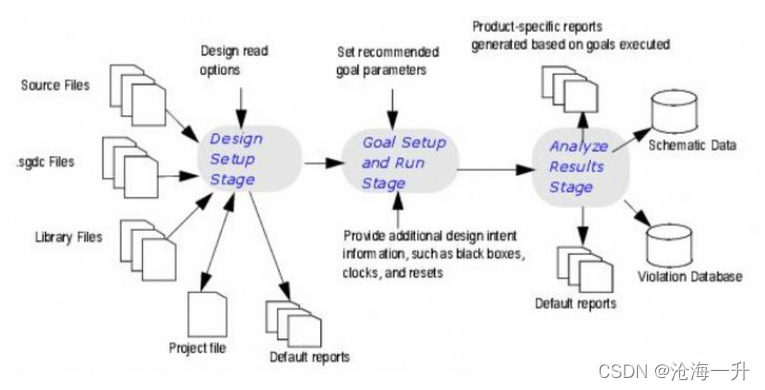

SpyGlass的功能模型总结如下图:

1、设置阶段(setup stage)

设置阶段的主要工作是:

- 添加设计文件、SGDC文件、预编译文件和技术文件。

- 指定影响SpyGlass运行的各种设计读取选项。例如,你可以在设计中指定顶层模块、更改语言、指定宏等等。。

- 运行design-read流程来执行第一级的HDL分析。在进入下一阶段之前,必须解决此阶段报告的致命错误(FATAL)。

Spyglass 可以运行在BATCH 或者 GUI 模式。通常模式下是在batch模式下执行分析,在GUI模式下进行debug。使用命令如下:

spyglass -gui& spyglass -project xxx.prj -designread -batch 1)工程(Project)文件

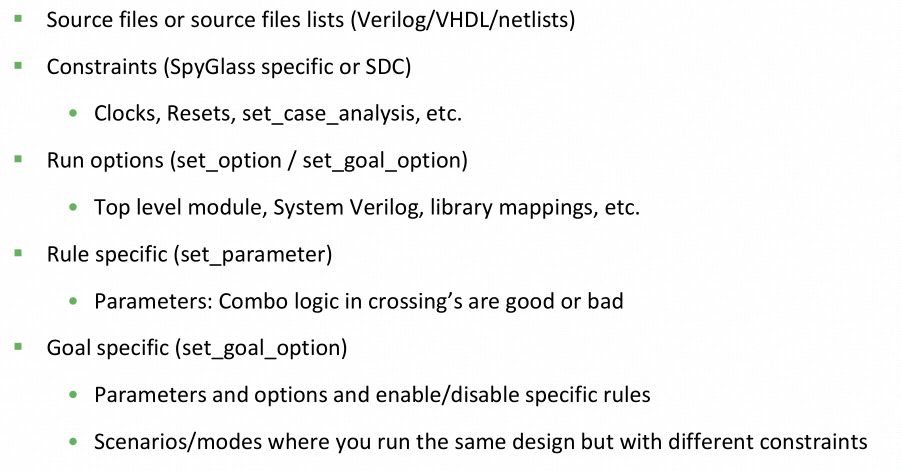

采用BATCH模式,这些设置都会添加到工程(Project)文件中,Project一般定义了以下内容:

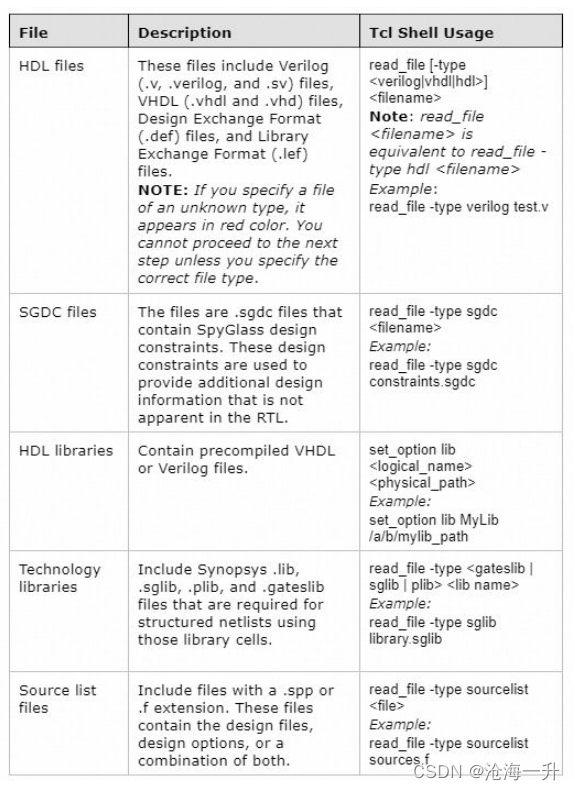

需要读入的文件及命令如下:

下面提供一个脚本范例:

#!SPYGLASS_PROJECT_FILE #!VERSION 3.0 -------------------------------------------------------------- # This is a software generated project file. Manual edits to this file could be lost during the next save operation # Copyright Synopsys Inc. # Last Updated By: SpyGlass SpyGlass_vL-2016.06 # Last Updated On Mon Dec 2 17:25:10 2019 ------------------------------------------------------------- Data Import Section read_file -type sourcelist cmd_files_ic read_file -type sgdc xxx.sgdc Common Options Section set_option top xxx set_option projectwdir . set_option language_mode mixed set_option designread_enable_synthesis no set_option designread_disable_flatten no set_option enableSV yes set_option disablev2k yes set_option 87 no set_option sdc2sgdc yes set_option top xxx set_option active_methodology $SPYGLASS_HOME/GuideWare/latest/block/rtl_handoff set_option sdc2sgdcfile xxx_sdc2sgdc.sgdc set_option extractDomainInfo true set_option stop { saradc_10bit_5vp15 reg_1p5_5vp15 por_lvd_5vp15 pch_5vp15 sensoradc_5vp15 osc800k_trim_5vp15 crystal_32k16m_5vp15 pll_800kto48m_5vp15 pad_cp pad_vdd pad_vss RASP256X9 RASP1536X9 pfm_1110skh32kx32_v1a0 gpio_ana_pad_5vp15 pad_vpp pad_avdh pad_avs por2_5vp15 } Goal Setup Section current_methodology $SPYGLASS_HOME/GuideWare/latest/block/rtl_handoff #current_goal cdc/cdc_setup_check -top xxx set_parameter enable_generated_clocks yes set_parameter write_sdc yes set_parameter report_indirect_port_clock yes set_parameter report_detail Clock_check10,all set_parameter allow_combo_logic yes set_parameter debug_proc yes set_parameter enable_glitchfreecell_detection yes set_parameter show_sdc_progress yes set_parameter strict_sync_check no set_parameter use_inferred_clocks yes set_parameter show_all_sdc_violations yes #set_parameter gen_block_sgdc -default set_parameter allow_clock_on_output_port yes set_parameter clock_gate_cell "ICG_V ICG" set_parameter enable_sync_cell "sync_level, Sync_Pulse" 2)约束(SGDC)文件

SGDC包含的内容一般如下:

SDC文件可以直接被SpyGlass读取,自动转换成SGDC,需要设置以下内容完成sdc2sgdc的转换:

set_option sdc2sgdc yes在.sgdc 文件中只需要写入下面语句就可以

current_design sssss sdc_data -file sssss_src.sdc在目录/constraints/sdc_check/spyglass_reports/sdc2sgdc/会有转化后的sdgc 文件。在sdc2sgdc 时,sdc 和sgdc 可以混合,如下:

current_design sssss clock -name clkA -period 10 -edge 0 5 //时钟约束 include ssss.sgdc set_case_analysis -name "sssss.atpg_test_en" -value 0 set_case_analysis -name "sssss..osc_sel" -value 1 //设置路径分析 sdc_data -file sssss_src.sdc //综合时使用的约束文件 reset -name "sssss.uAnd2.Z" -async -value 0 reset -name "sssss..POR_SRC" -async -value 0 //设置异步复位信号2、目标(Goal)设定和运行(Run)阶段

在此阶段将选择并运行目标。目标是规则的集合。可以选择规则,也可以指定规则执行的顺序。

在SpyGlass CDC分析期间可以在不同的阶段运行不同的SpyGlass CDC目标。在每个阶段中,修复所报告的违例并转移到下一个阶段。如果不遵循这个分步骤的方法,可能会看到大量违反CDC的情况,其中大多数是由于不正确的设置或没有修复前几个阶段的违例引起的。

这里我们以GUI界面为主进行介绍。

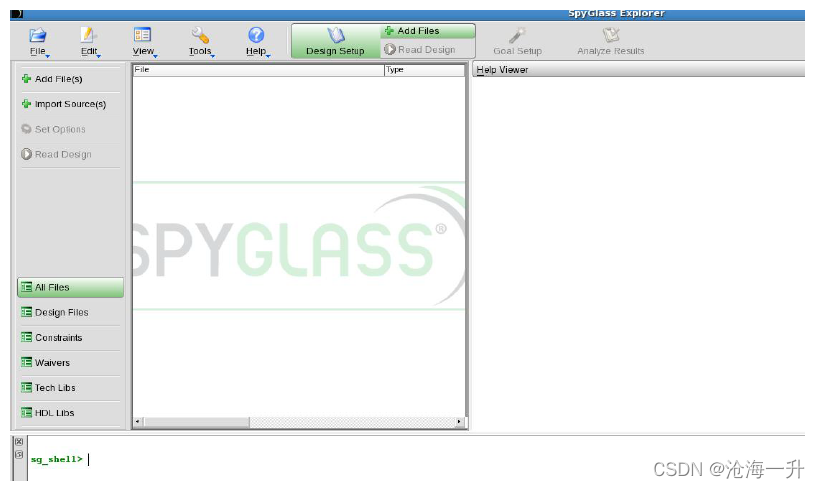

输入命令进入gui 界面如下:

spyglass 类似pt,是静态验证工具。特点就是不需要编写testbench,就可以验证。

1. Adding Design Files—-加入rtl 和sgdc 文件。这里需要通过set optin对Top Level Design Unit 进行设置。

2. Viewing and Changing Design Read Options

3. Running Design Read

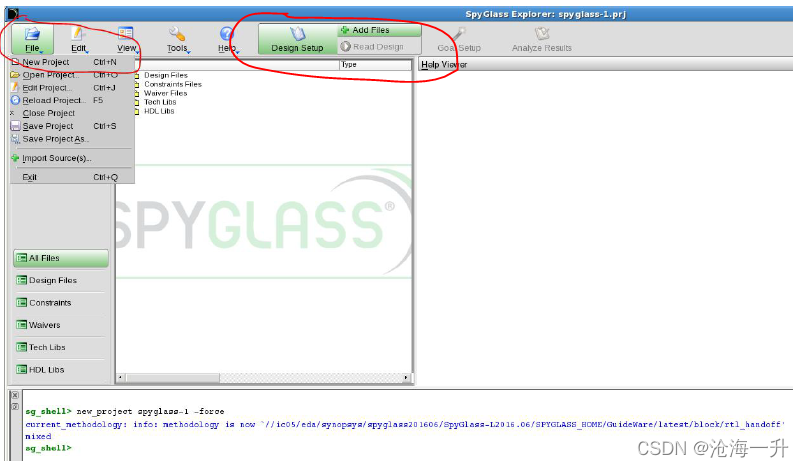

点击file -> new_project (对应sg_shell>new_project spyglass-1 –force 命令)

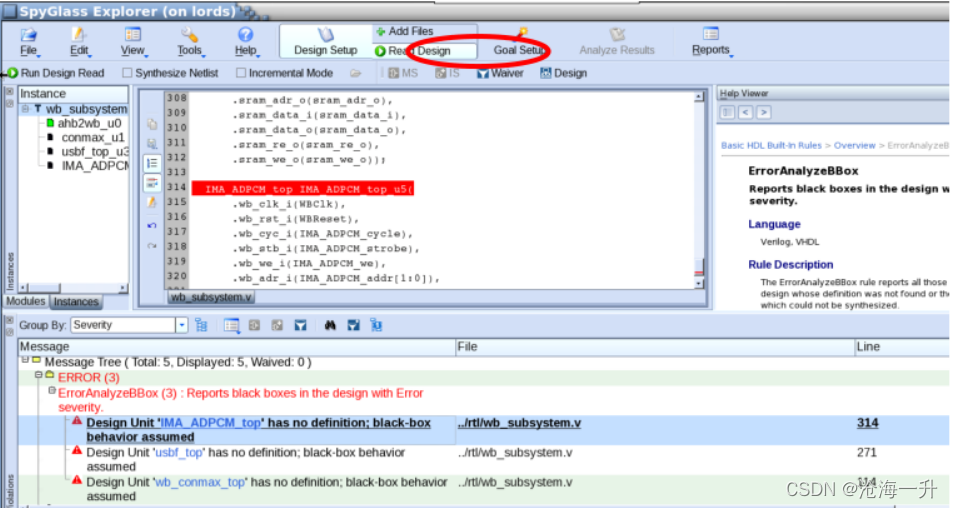

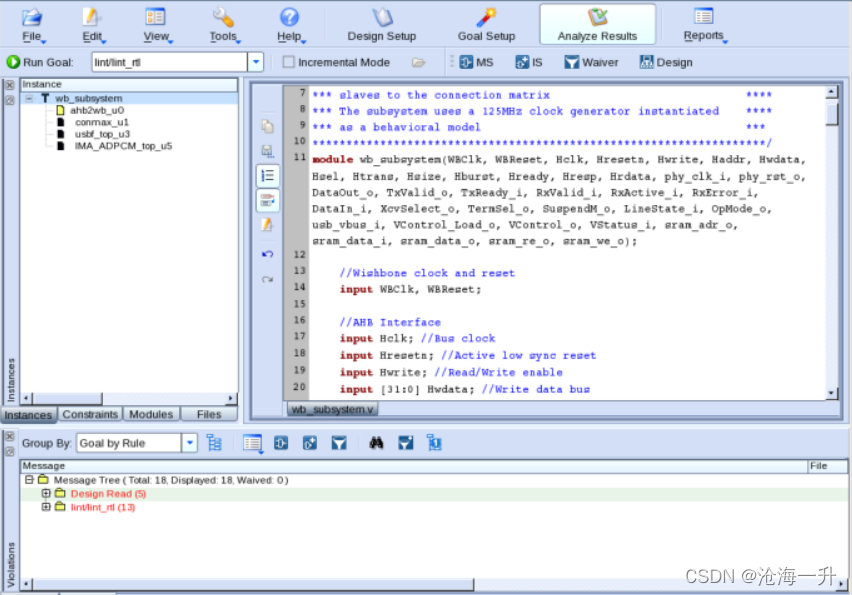

点击Run Design Read 开始进行设计文件编译和分析,在读取完成后会在下方窗口列出问题。如下图所示:

其中三个问题类型都为ErrorAnalyzeB Box,这是因为有的模块文件没有添加,SPYGLASS找不到,后面SPYGLASS会将其作为黑盒子处理。

左侧instance下文件不同颜色标识意义为:

- 绿色表示该模块可进行分析,但不可进行综合;

- 黑色表示该模块作为黑盒子存在;

- 白色表示该模块可综合。

需要注意,只是读取设计并不会完成综合,因此也不会创建相关的原理图。因此,为了使用spyglass,首先应该解决黑盒子问题。

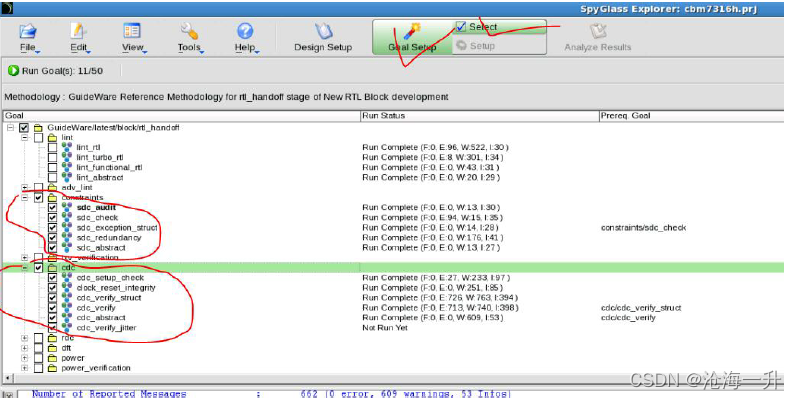

然后选择不同目标进行检查:

然后点击Run Goal(s) ,当运行完成,会自动弹出Analyze Result窗口。

得到分析结果后,首先查看Lint分析结果。首先展开lint/lint_rtl文件夹消息。错误信息以红色显示,警告以橙色显示,信息以绿色显示。双击违规消息,此时与错误相关的代码会在RTL代码窗口中显示出来。 此时可以对该问题进行分析。

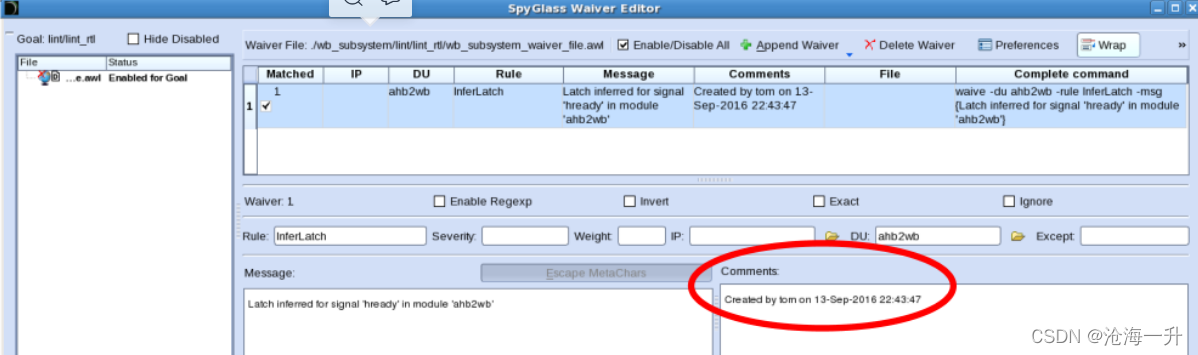

可以通过手动添加waivers来放弃对一些电路的检查:鼠标在违规信息上 -> 右键 -> Waive Selected Messages…

这将打开waivers编辑器窗口,并为其填充相关信息(违规消息、规则和设计单位(DU)):

可以在Comments字段中添加放弃的原因。做出任何更改后,单击Apply。可以将Waiver设置保存为文件然后重复使用:在waivers编辑器窗口中右键点击左侧面板中文件,然后选择Save Waiver Files。 SpyGlass会为每个Goal保存一个关于检查过滤的文件。

3、生成报告

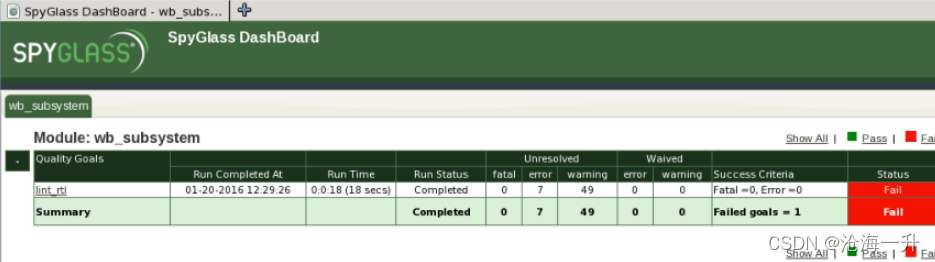

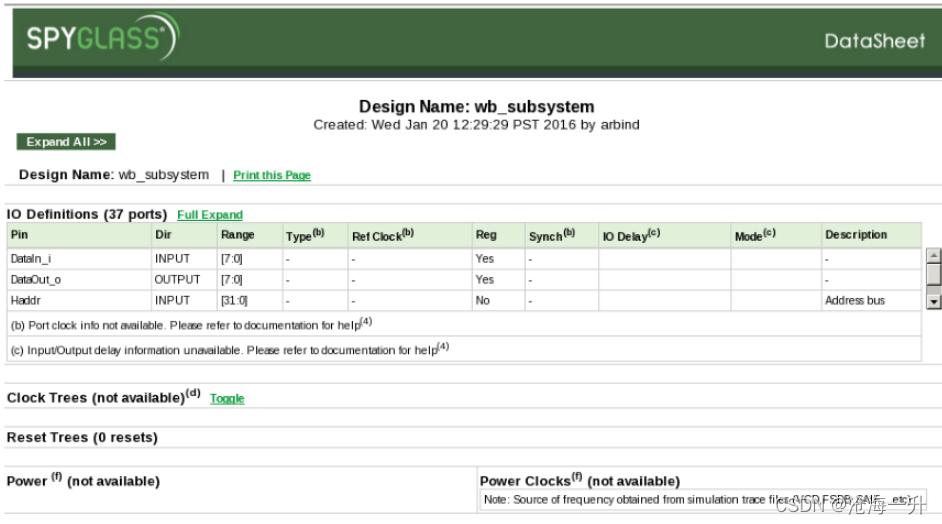

报表内容为运行的Goal的分析结果。有的功能需要使用SpyGlass的组件完成,如果具有相应的License则会将相应的运行结果包含在报表中。报表包括datasheet 和dashboard 。

在GUI界面下打开shell命令窗口,输入如下命令生成报表:

write_aggregate_report datasheet write_aggregate_report dashboard生成的报表可以用浏览器打开,下面两张图为报表示例:

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/133036.html