大家好,欢迎来到IT知识分享网。

REVIEW

已经学习过VGA 时序与实现-CSDN博客

VGA 多分辨率-CSDN博客

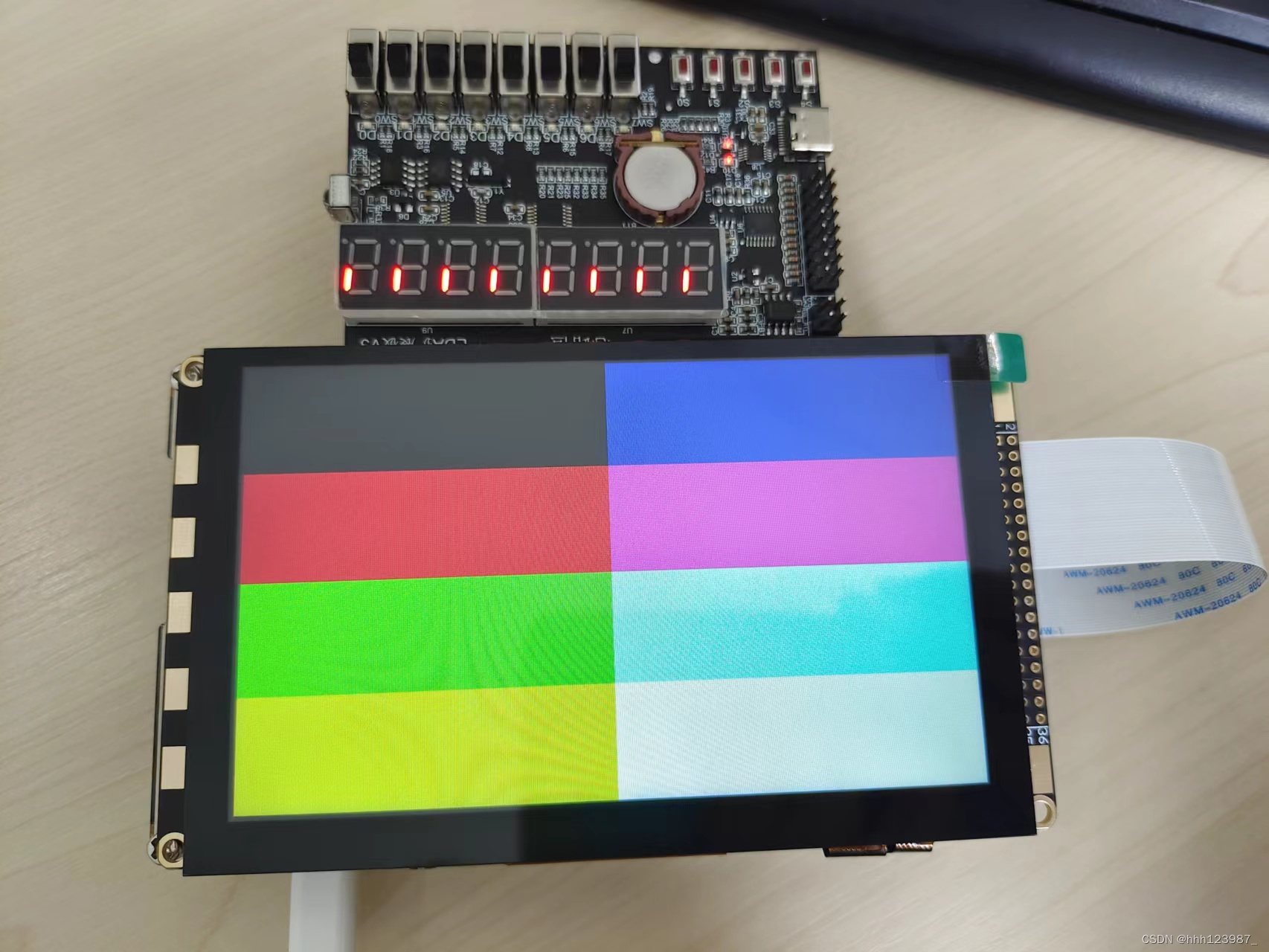

今天就来让TFT屏显示一下

ACZ702开发板管脚信息表 – ACZ702开发板 – 芯路恒电子技术论坛 – Powered by Discuz! (corecourse.cn)

小梅哥视频:24 RGB TFT显示屏原理与驱动实现_哔哩哔哩_bilibili

1. 设置显示屏参数与时钟

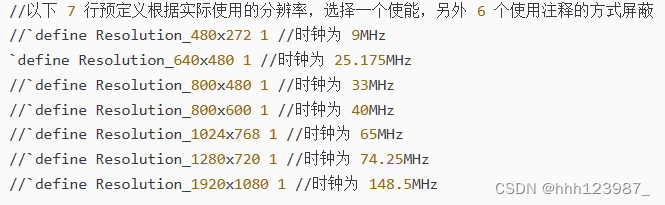

注意到VGA_parameter.v中,不懂得分辨率对应于不同的频率,这里结合IP核,学习clk

现有时钟频率为50MHz ,5寸 TFT屏对应800*480为33MHz

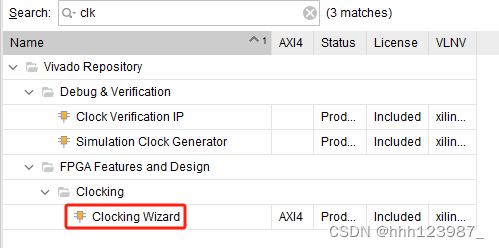

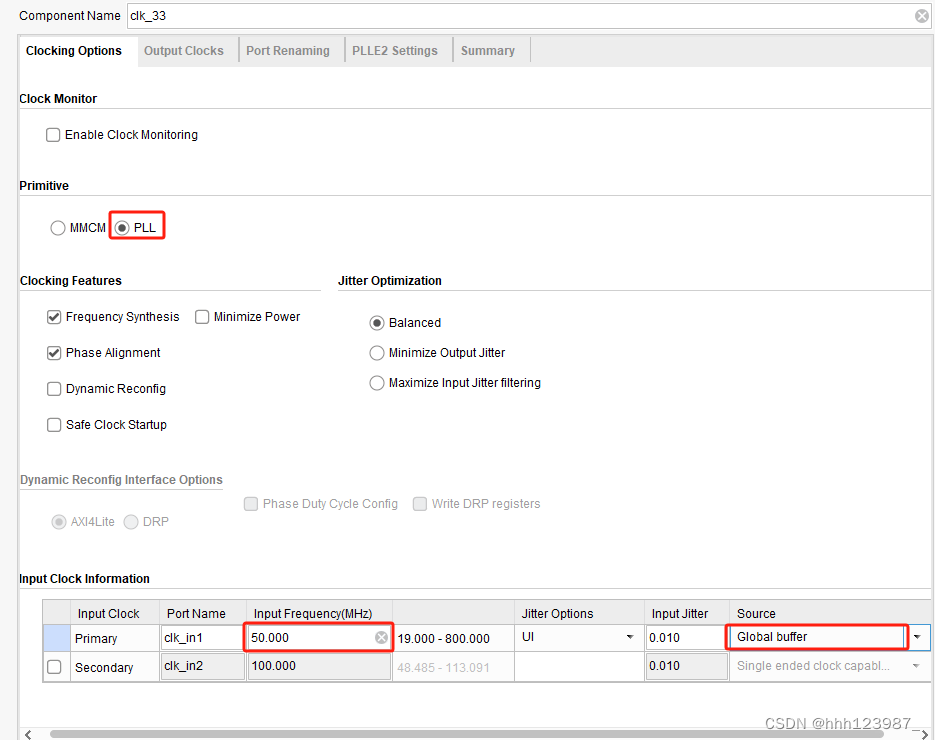

采用PLL锁相环设置时钟频率

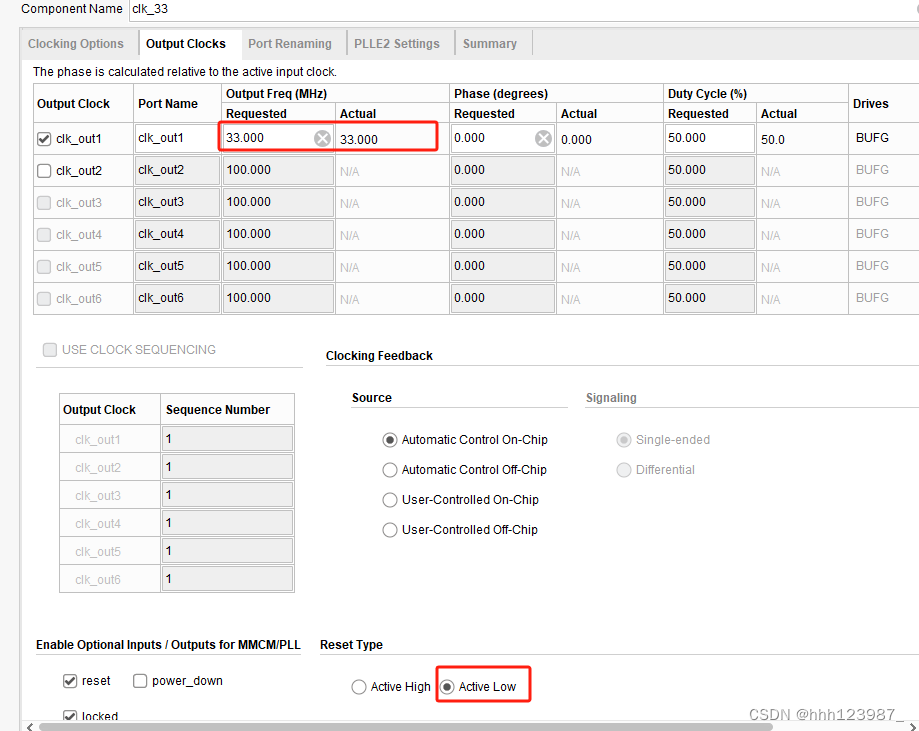

由于 ACZ702 的按键按下是低电平, PLL 复位设置成低电平有效。

具体设置方法如下:

本次实验只生成一个时钟频率,但在本页设置中,可以增加多个输出时钟:

同频率不同相位、不同频率等, 在后续实验中,可以进行设置进行比较

本次未设置reset 、locked

2. VGA_CTRL.v

本程序中未对RGB888/RGB565进行设置

在xdc文件中进行说明

module VGA_CTRL( input clk , input reset_n , input [23:0]data , output reg data_req , output reg [11:0]H_addr , //当前扫描点的H坐标 output reg [11:0]V_addr , //当前扫描点的V坐标 output reg VGA_HS , output reg VGA_VS , output reg VGA_BLK , //BLK表示的是data时间段 output reg [23:0]VGA_RGB //{R[7:0]、G[7:0]、B[7:0]} ); `include "vga_parameter.v" localparam VGA_HS_end = `H_Sync_Time - 1'b1 ; localparam Hdat_begin = `H_Sync_Time + `H_Back_Porch + `H_Left_Border - 1'b1 ; localparam Hdat_end = `H_Total_Time - `H_Right_Border - `H_Front_Porch - 1'b1 ; localparam Hpixel_end = `H_Total_Time - 1'b1 ; localparam VGA_VS_end = `V_Sync_Time - 1'b1 ; localparam Vdat_begin = `V_Sync_Time + `V_Back_Porch + `V_Top_Border - 1'b1 ; localparam Vdat_end = `V_Total_Time - `V_Bottom_Border - `V_Front_Porch - 1'b1 ; localparam Vline_end = `V_Total_Time - 1'b1 ; //行计数器 reg[11:0]H_cnt; always@(posedge clk or negedge reset_n) if(!reset_n) H_cnt <= 0 ; else if(H_cnt == Hpixel_end) H_cnt <= 0 ; else H_cnt <= H_cnt + 1'b1 ; // 场计数器 reg[11:0]V_cnt; always@(posedge clk or negedge reset_n) if(!reset_n) V_cnt <= 0 ; else if(H_cnt == Hpixel_end) if(V_cnt == Vline_end) V_cnt <= 0 ; else V_cnt <= V_cnt + 1'b1 ; else V_cnt <= V_cnt ; // VGA_HS always@(posedge clk or negedge reset_n) if(!reset_n) VGA_HS <= 1; else if(H_cnt == 0) VGA_HS <= 0; else if(H_cnt > VGA_HS_end) VGA_HS <= 1; // VGA_VS always@(posedge clk or negedge reset_n) if(!reset_n) VGA_VS <= 1; else if(V_cnt == 0) VGA_VS <= 0; else if(V_cnt > VGA_VS_end) VGA_VS <= 1; // data_req always@(posedge clk or negedge reset_n) if(!reset_n) data_req <= 0 ; else data_req <= ((H_cnt >= Hdat_begin)&&(H_cnt < Hdat_end)&&(V_cnt >= Vdat_begin)&&(V_cnt <= Vdat_end)) ? 1 : 0; // VGA_BLK always@(posedge clk or negedge reset_n) if(!reset_n) VGA_BLK <= 0 ; else VGA_BLK <= data_req ; // assign VGA_RGB = VGA_BLK? Data:0; // VGA_RGB always@(posedge clk ) if(data_req) VGA_RGB <= data; else VGA_RGB <= 0; //address always@(posedge clk ) if(data_req) begin H_addr <= H_cnt - Hdat_begin; V_addr <= V_cnt - Vdat_begin; end else begin H_addr <= 0; V_addr <= 0; end endmodule 3. VGA_CTRL_test.v

显示彩条:

TFT_BL表示背光,拉高即可

module VGA_CTRL_test( input clk , //50MHZ时钟 input reset_n , output VGA_CLK, output VGA_HS, //TFT行同步信号 output VGA_VS, //TFT场同步信号 output VGA_BLK, //VGA 场消隐信号 output [23:0] VGA_RGB ,//TFT数据输出 output TFT_BL //背光 ); assign TFT_BL = 1; reg [23:0]disp_data; wire [11:0]hcount; wire [11:0]vcount; wire Clk33M; wire Data_Req; assign VGA_CLK= Clk33M; clk_vga vga_clk( .clk_out1(Clk33M), .clk_in1(clk) ); VGA_CTRL VGA_CTRL( .clk(Clk33M), //系统输入时钟33MHZ .reset_n(reset_n), .data(disp_data), //待显示数据 .data_req(Data_Req), .H_addr(hcount), //VGA行扫描计数器 .V_addr(vcount), //VGA场扫描计数器 .VGA_HS(VGA_HS), //VGA行同步信号 .VGA_VS(VGA_VS), //VGA场同步信号 .VGA_BLK(VGA_BLK) , //VGA 场消隐信号 .VGA_RGB(VGA_RGB) //VGA数据输出 ); //定义颜色编码 localparam BLACK = 24'h000000, //黑色 BLUE = 24'h0000FF, //蓝色 RED = 24'hFF0000, //红色 PURPPLE = 24'hFF00FF, //紫色 GREEN = 24'h00FF00, //绿色 CYAN = 24'h00FFFF, //青色 YELLOW = 24'hFFFF00, //黄色 WHITE = 24'hFFFFFF; //白色 //定义每个像素块的默认显示颜色值 localparam R0_C0 = BLACK, //第0行0列像素块 R0_C1 = BLUE, //第0行1列像素块 R1_C0 = RED, //第1行0列像素块 R1_C1 = PURPPLE,//第1行1列像素块 R2_C0 = GREEN, //第2行0列像素块 R2_C1 = CYAN, //第2行1列像素块 R3_C0 = YELLOW, //第3行0列像素块 R3_C1 = WHITE; //第3行1列像素块 wire R0_act = vcount >= 0 && vcount < 120; //正在扫描第0行 wire R1_act = vcount >= 120 && vcount < 240;//正在扫描第1行 wire R2_act = vcount >= 240 && vcount < 360;//正在扫描第2行 wire R3_act = vcount >= 360 && vcount < 480;//正在扫描第3行 wire C0_act = hcount >= 0 && hcount < 400; //正在扫描第0列 wire C1_act = hcount >= 400 && hcount < 800;//正在扫描第1列 wire R0_C0_act=R0_act & C0_act;//第0行0列像素块处于被扫描中标志信号 wire R0_C1_act=R0_act & C1_act;//第0行1列像素块处于被扫描中标志信号 wire R1_C0_act=R1_act & C0_act;//第1行0列像素块处于被扫描中标志信号 wire R1_C1_act=R1_act & C1_act;//第1行1列像素块处于被扫描中标志信号 wire R2_C0_act=R2_act & C0_act;//第2行0列像素块处于被扫描中标志信号 wire R2_C1_act=R2_act & C1_act;//第2行1列像素块处于被扫描中标志信号 wire R3_C0_act=R3_act & C0_act;//第3行0列像素块处于被扫描中标志信号 wire R3_C1_act=R3_act & C1_act;//第3行1列像素块处于被扫描中标志信号 always@(*) case({R3_C1_act,R3_C0_act,R2_C1_act,R2_C0_act, R1_C1_act,R1_C0_act,R0_C1_act,R0_C0_act}) 8'b0000_0001:disp_data = R0_C0; 8'b0000_0010:disp_data = R0_C1; 8'b0000_0100:disp_data = R1_C0; 8'b0000_1000:disp_data = R1_C1; 8'b0001_0000:disp_data = R2_C0; 8'b0010_0000:disp_data = R2_C1; 8'b0100_0000:disp_data = R3_C0; 8'b1000_0000:disp_data = R3_C1; default:disp_data = R0_C0; endcase endmodule 4. VGA_CTRL_test.xdc

由于使用的是RGB565格式

设置中data 与 VGA_RGB 都为24位

此时在I/O中有几位是无需链接的,会出现[DRC NSTD-1]

【Vivado常见问题】【DRC NSTD-1 DRC UCIO-1】无法生成bitstream(部分管脚位置或电平未指定) – Vivado软件使用和设置 – 芯路恒电子技术论坛 – Powered by Discuz! (corecourse.cn)

xdc文件添加:

| set_property SEVERITY {Warning} [get_drc_checks NSTD-1] set_property SEVERITY {Warning} [get_drc_checks RTSTAT-1] set_property SEVERITY {Warning} [get_drc_checks UCIO-1] |

set_property SEVERITY {Warning} [get_drc_checks NSTD-1] set_property SEVERITY {Warning} [get_drc_checks RTSTAT-1] set_property SEVERITY {Warning} [get_drc_checks UCIO-1] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[23]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[22]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[21]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[20]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[19]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[18]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[17]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[16]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[15]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[14]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[13]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[12]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[11]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[10]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[9]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[8]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[0]}] set_property IOSTANDARD LVCMOS33 [get_ports clk] set_property IOSTANDARD LVCMOS33 [get_ports reset_n] set_property IOSTANDARD LVCMOS33 [get_ports VGA_BLK] set_property IOSTANDARD LVCMOS33 [get_ports TFT_BL] set_property IOSTANDARD LVCMOS33 [get_ports VGA_CLK] set_property IOSTANDARD LVCMOS33 [get_ports VGA_HS] set_property IOSTANDARD LVCMOS33 [get_ports VGA_VS] set_property PACKAGE_PIN W20 [get_ports {VGA_RGB[23]}] set_property PACKAGE_PIN W19 [get_ports {VGA_RGB[22]}] set_property PACKAGE_PIN V17 [get_ports {VGA_RGB[21]}] set_property PACKAGE_PIN V16 [get_ports {VGA_RGB[20]}] set_property PACKAGE_PIN T15 [get_ports {VGA_RGB[19]}] set_property PACKAGE_PIN V20 [get_ports {VGA_RGB[15]}] set_property PACKAGE_PIN U17 [get_ports {VGA_RGB[14]}] set_property PACKAGE_PIN V18 [get_ports {VGA_RGB[13]}] set_property PACKAGE_PIN T16 [get_ports {VGA_RGB[12]}] set_property PACKAGE_PIN R16 [get_ports {VGA_RGB[11]}] set_property PACKAGE_PIN U19 [get_ports {VGA_RGB[10]}] set_property PACKAGE_PIN Y19 [get_ports {VGA_RGB[7]}] set_property PACKAGE_PIN Y18 [get_ports {VGA_RGB[5]}] set_property PACKAGE_PIN W16 [get_ports {VGA_RGB[4]}] set_property PACKAGE_PIN Y17 [get_ports {VGA_RGB[3]}] set_property PACKAGE_PIN W14 [get_ports VGA_VS] set_property PACKAGE_PIN U14 [get_ports VGA_HS] set_property PACKAGE_PIN U15 [get_ports VGA_CLK] set_property PACKAGE_PIN R17 [get_ports TFT_BL ] set_property PACKAGE_PIN U18 [get_ports clk] set_property PACKAGE_PIN H18 [get_ports reset_n] set_property PACKAGE_PIN W15 [get_ports VGA_BLK] 5. 显示

6. RGB565

对后续使用TFT屏幕,将VGA_CTRL改为VGA_CTRL_565进行使用

即 [23,0]改为[15,0]

6.1 VGA_CTRL_RGB565.v

module VGA_CTRL_RGB565( input clk , input reset_n , input [15:0]data , output reg data_req , output reg [11:0]H_addr , //当前扫描点的H坐标 output reg [11:0]V_addr , //当前扫描点的V坐标 output reg VGA_HS , output reg VGA_VS , output reg VGA_BLK , //BLK表示的就是输出输出的时间段 output reg [15:0]VGA_RGB //{R[5:0]、G[6:0]、B[5:0]} ); `include "vga_parameter.v" localparam VGA_HS_end = `H_Sync_Time - 1'b1 ; localparam Hdat_begin = `H_Sync_Time + `H_Back_Porch + `H_Left_Border - 1'b1 ; localparam Hdat_end = `H_Total_Time - `H_Right_Border - `H_Front_Porch - 1'b1 ; localparam Hpixel_end = `H_Total_Time - 1'b1 ; localparam VGA_VS_end = `V_Sync_Time - 1'b1 ; localparam Vdat_begin = `V_Sync_Time + `V_Back_Porch + `V_Top_Border - 1'b1 ; localparam Vdat_end = `V_Total_Time - `V_Bottom_Border - `V_Front_Porch - 1'b1 ; localparam Vline_end = `V_Total_Time - 1'b1 ; //行计数器 reg[11:0]H_cnt; always@(posedge clk or negedge reset_n) if(!reset_n) H_cnt <= 0 ; else if(H_cnt == Hpixel_end) H_cnt <= 0 ; else H_cnt <= H_cnt + 1'b1 ; // 场计数器 reg[11:0]V_cnt; always@(posedge clk or negedge reset_n) if(!reset_n) V_cnt <= 0 ; else if(H_cnt == Hpixel_end) if(V_cnt == Vline_end) V_cnt <= 0 ; else V_cnt <= V_cnt + 1'b1 ; else V_cnt <= V_cnt ; // VGA_HS always@(posedge clk or negedge reset_n) if(!reset_n) VGA_HS <= 1; else if(H_cnt == 0) VGA_HS <= 0; else if(H_cnt > VGA_HS_end) VGA_HS <= 1; // VGA_VS always@(posedge clk or negedge reset_n) if(!reset_n) VGA_VS <= 1; else if(V_cnt == 0) VGA_VS <= 0; else if(V_cnt > VGA_VS_end) VGA_VS <= 1; // data_req always@(posedge clk or negedge reset_n) if(!reset_n) data_req <= 0 ; else data_req <= ((H_cnt >= Hdat_begin)&&(H_cnt < Hdat_end)&&(V_cnt >= Vdat_begin)&&(V_cnt <= Vdat_end)) ? 1 : 0; // VGA_BLK always@(posedge clk or negedge reset_n) if(!reset_n) VGA_BLK <= 0 ; else VGA_BLK <= data_req ; // assign VGA_RGB = VGA_BLK? Data:0; // VGA_RGB always@(posedge clk ) if(data_req) VGA_RGB <= data; else VGA_RGB <= 0; //address always@(posedge clk ) if(data_req) begin H_addr <= H_cnt - Hdat_begin; V_addr <= V_cnt - Vdat_begin; end else begin H_addr <= 0; V_addr <= 0; end endmodule 6.2 VGA_CTRL_RGB565.xdc

set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[15]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[14]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[13]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[12]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[11]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[10]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[9]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[8]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[0]}] set_property IOSTANDARD LVCMOS33 [get_ports clk] set_property IOSTANDARD LVCMOS33 [get_ports reset_n] set_property IOSTANDARD LVCMOS33 [get_ports VGA_BLK] set_property IOSTANDARD LVCMOS33 [get_ports TFT_BL] set_property IOSTANDARD LVCMOS33 [get_ports VGA_CLK] set_property IOSTANDARD LVCMOS33 [get_ports VGA_HS] set_property IOSTANDARD LVCMOS33 [get_ports VGA_VS] set_property PACKAGE_PIN W20 [get_ports {VGA_RGB[15]}] set_property PACKAGE_PIN W19 [get_ports {VGA_RGB[14]}] set_property PACKAGE_PIN V17 [get_ports {VGA_RGB[13]}] set_property PACKAGE_PIN V16 [get_ports {VGA_RGB[12]}] set_property PACKAGE_PIN T15 [get_ports {VGA_RGB[11]}] set_property PACKAGE_PIN V20 [get_ports {VGA_RGB[10]}] set_property PACKAGE_PIN U17 [get_ports {VGA_RGB[9]}] set_property PACKAGE_PIN V18 [get_ports {VGA_RGB[8]}] set_property PACKAGE_PIN T16 [get_ports {VGA_RGB[7]}] set_property PACKAGE_PIN R16 [get_ports {VGA_RGB[6]}] set_property PACKAGE_PIN U19 [get_ports {VGA_RGB[5]}] set_property PACKAGE_PIN Y19 [get_ports {VGA_RGB[4]}] set_property PACKAGE_PIN W18 [get_ports {VGA_RGB[3]}] set_property PACKAGE_PIN Y18 [get_ports {VGA_RGB[2]}] set_property PACKAGE_PIN W16 [get_ports {VGA_RGB[1]}] set_property PACKAGE_PIN Y17 [get_ports {VGA_RGB[0]}] set_property PACKAGE_PIN W14 [get_ports VGA_VS] set_property PACKAGE_PIN U14 [get_ports VGA_HS] set_property PACKAGE_PIN U15 [get_ports VGA_CLK] set_property PACKAGE_PIN R17 [get_ports TFT_BL] set_property PACKAGE_PIN U18 [get_ports clk] set_property PACKAGE_PIN H18 [get_ports reset_n] set_property PACKAGE_PIN W15 [get_ports VGA_BLK] 免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/141185.html