大家好,欢迎来到IT知识分享网。

系列文章目录

PCIe扫盲(一)

PCIe扫盲(二)

PCIe扫盲(三)

PCIe扫盲(四)

PCIe扫盲(五)

PCIe扫盲(六)

PCIe扫盲(七)

PCIe扫盲(八)

PCIe扫盲(九)

PCIe扫盲(10)

PCIe扫盲(11)

PCIe扫盲(12)

PCIe扫盲(13)

PCIe扫盲(14)

热插拔简要介绍

某些特殊的应用场合可能要求 PCIe 设备能够以高可靠性持续不间断运行,为此,PCIe 总线采用热插拔(Hot Plug)和热切换(Hot Swap)技术,来实现不关闭系统电源的情况下更换 PCIe 卡设备。

注:热切换(Hot Swap)和热插拔的主要区别是应用领域不同,热插拔主要应用于 PC 以及服务器的主板上的板卡连接,而热切换主要针对的是 CPCI(CompactPCI ,一种常用于仪器仪表的接口)应用的。具体请参考 PCIe Spec 和 PCIe CEM Spec 的相关章节。

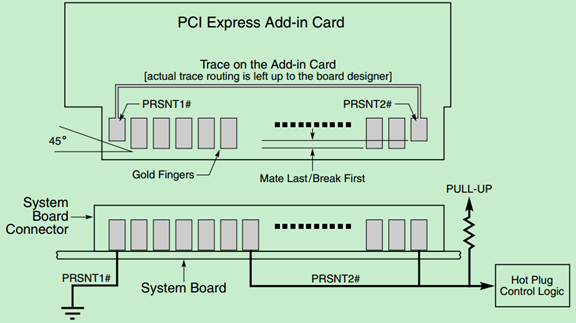

PCIe 总线的热插拔主要指的是 PCIe 卡设备的热插拔,以及相关的实现机制等。PCIe 卡有两个用于热插拔机制的引脚 —— PRSNT1# 和 PRSNT2# 。PCIe 卡设备上的这两个信号之间是短路的,PCIe 插槽的 PRSNT1# 被固定地连接到地,PRSNT2# 则被上拉。且 PCIe 卡上的这两个信号的金手指长度要比其他的信号的金手指长度要短一点。如下图所示,当 PCIe 卡设备未被完全插入插槽时,插槽的 PRSNT2# 信号由于上拉的作用,将一直处于高点平状态。当 PCIe 卡设备被完全插入插槽后,插槽上的 PRSNT2# 信号则会被 PCIe 卡设备的短路线连接到地,从而使得其变为低电平。换句话说,从插槽的角度看,当 PRSNT2# 位高电平时,则认为 PCIe 卡设备未能正确插入或者无 PCIe 卡设备;当 PRSNT2# 位低电平时,表明 PCIe 卡设备被正确地插入插槽中。

注:PCIe 总线除了有一个 Base Spec 之外,还有一个关于 PCIe 卡设备的 Spec —— PCIe Card ElectroMechanical Spec(CEM)。

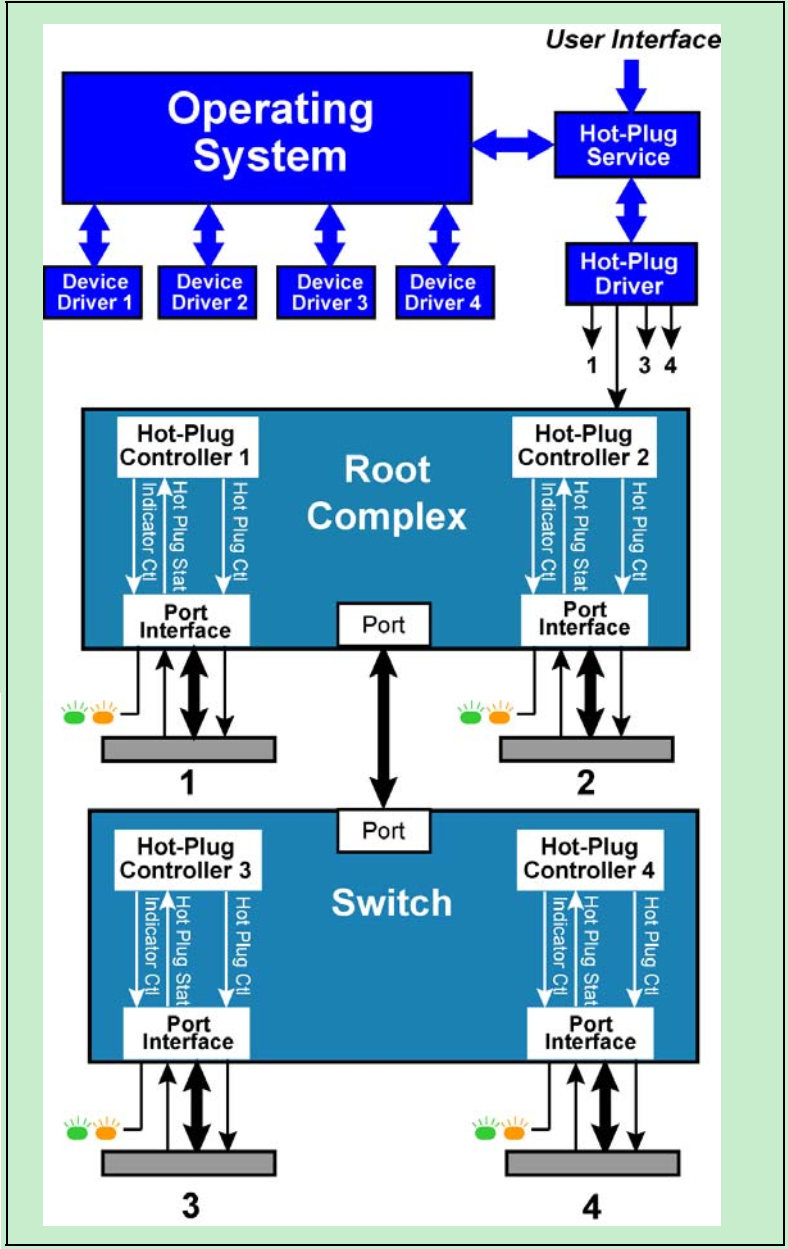

与 PCI 总线不同,PCIe 总线采用的是点到点的连接(Point-to-Point Connections),因此其并不像 PCI 总线那样需要用于卡设备的隔离逻辑(Isolation Logic),但是每个端口(桥设备中的,如 Root 和 Switch )都必须包含一个独立的热插拔控制器(Hot Plug Controller),如下图所示:

当然,热插拔不仅仅是硬件的事,其需要软硬件协同实现。要想实现热插拔功能,操作系统、主板热插拔驱动器、PCIe 卡设备驱动以及 PCIe 卡硬件功能都必须支持热插拔,缺一不可。从 PCIe 卡设备硬件功能的角度来看,其需要支持 Quiesce 命令、Pause 命令(可选)、Start 命令和 Resume 命令。

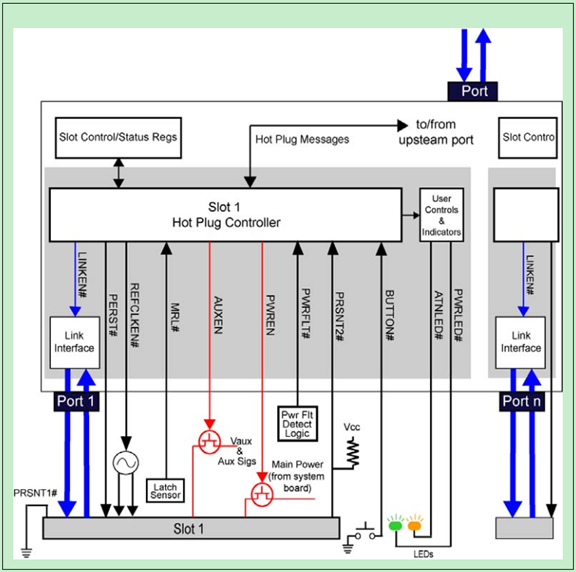

桥设备(Switch 等)中还需要支持热插拔控制器(Hot Plug Controller),如下图所示,这里就不详细介绍了。具体请参考 PCIe Spec 相关章节内容。

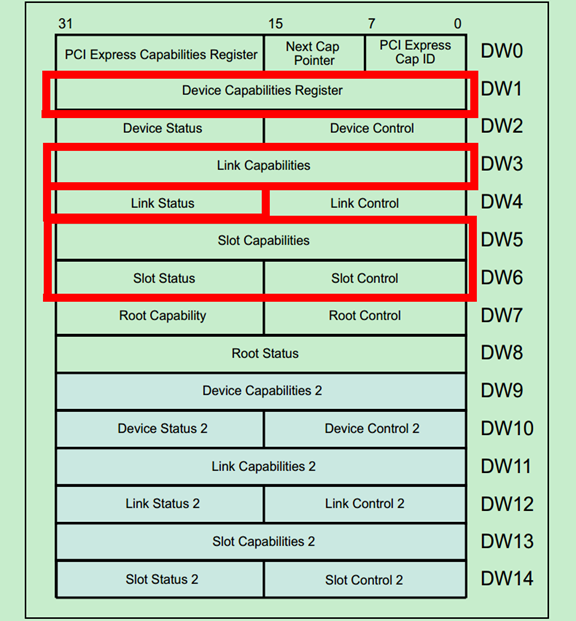

配置空间中,与热插拔相关的寄存器如下图所示:

具体就不详细介绍了,请参考 PCIe Spec 相关章节。

PCI Express 物理层接口(PIPE)

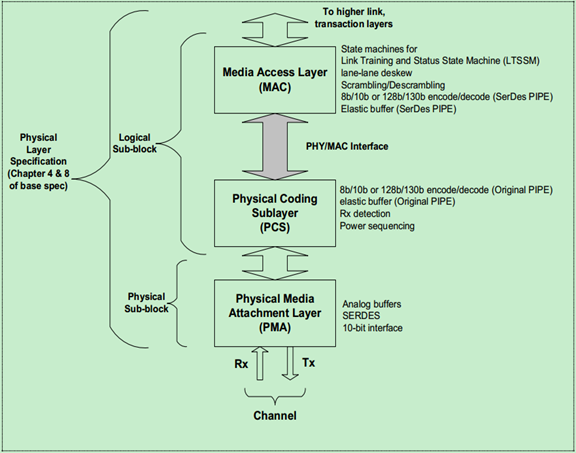

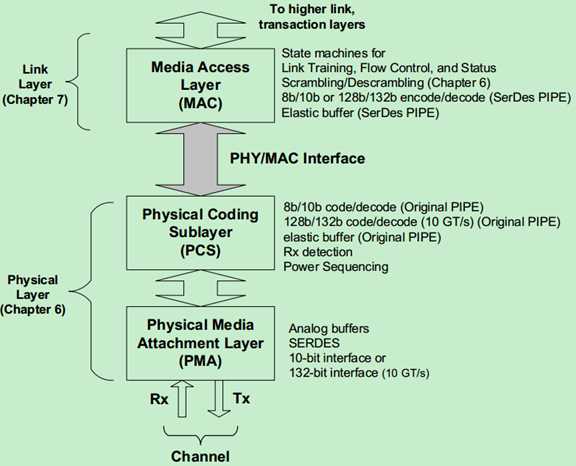

PCIe 物理层接口(Physical Interface for PCI Express,PIPE)定义了物理层中的,媒介层(Media Access Layer,MAC)和物理编码子层(Physical Coding Sub-layer,PCS)之间的统一接口,旨在为提供一种统一的行业标准。如下图所示:

其中 MAC 和 PCS 都属于 PCIe 中的物理层逻辑子层部分,而 PMA(Physical Media Attachment Layer)则属于物理层电气子层。需要注意的是,PIPE 规范是由 Intel 提出的行业建议,并非 PCI-SIG 规定的 PCIe 标准之一。PCIe 设备厂家完全可以自主选择是否采用 PIPE 规范。

由于业界通常采用 SerDes 器件(包括 FPGA 中集成的 SerDes 模块)来实现 PCIe 中的 PCS 和 PMA,所以往往 MAC(以及事务层和数据链路层等)和 PCS/PMA 是独立设计的,甚至是不同厂家设计的。为这之间提供统一的行业标准 —— PIPE,有助于使不同厂家之间的设备有更好的兼容性。当然,也有很多 PCIe 设备完全是由一个厂家设计的(如部分基于 PCIe 的 ASIC 等),此时是否采用 PIPE 的必要性就不是那么重要了。

随着高速串行技术的发展,各种串行通信技术的物理层逐渐走向了统一,用户甚至可以基于 FPGA 中的 SerDes/PCS 完成多种高速串行通信接口的设计。这些通信接口的区别往往只是体现在高层协议(数据链路层与事务层等),在物理层上(尤其是物理层电气子层上)基本上是一致的。

虽然 PIPE 规范最早是用于 PCIe 总线中的(从命名方式就可以看出来),但是该规范的后续版本逐渐开始支持了其他的串行接口。以 Intel 发布的最新版本的 PIPE Spec 为例(v5.1),该版本涉及 PCI Express、SATA、USB、DisplayPort 和 Converged IO 等多种高速串行接口。

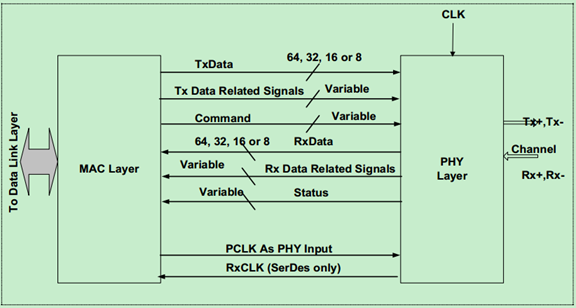

USB 中的 PHY/MAC 接口,如下图所示:

详细的 PHY/MAC 接口(PIPE)的示意图如下(PCIe、USB 等):

弹性缓存(Elastic Buffer/ CTC Buffer)

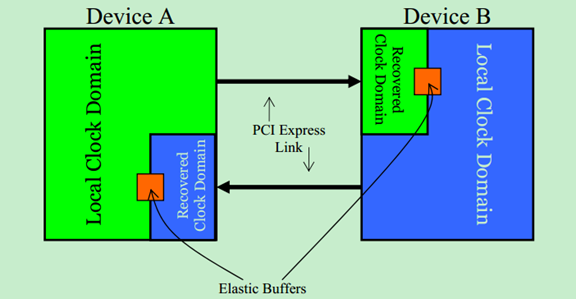

前面在介绍 PCIe 物理层逻辑子层的文章中,有提到过弹性缓存(Elastic Buffer,又称为 CTC Buffer 或者 Synchronization Buffer)。其本质上是一种 FIFO,主要用于解决跨时钟域问题。当然,PCIe 的弹性缓存还用于补偿时钟误差(Compensate for the clock differences)。实际上,除了 PCIe ,弹性缓存还广泛应用于其它的高速串行接口 —— USB、InfiniBand、Fibre Channel、Gigabit Ethernet 等基于 SerDes 的应用。

由于 PCIe 采用的基于 8b/10b 的嵌入式源同步时钟,接收端存在两个时钟域:一个是通过 CDR 从数据流中解析出来的时钟,用该时钟对数据进行采样;另一个是本地时钟域,用于其他的逻辑的。借助弹性缓存(FIFO),可以实现数据在这两个时钟域的转换。

以 PCIe Gen1 为例,链路上的数据速率为 2.5Gbps。但实际上,任何晶振(或者其他频率发生器)都是有误差的,PCIe Spec 允许的误差范围为 ±300ppm(Parts Per Million)。即,链路上实际的频率范围为 2.49925GHz~2.50075GHz 。借助弹性缓存,通过删除或者插入 SKP Ordered Set 可以消除链路频率误差的影响。如下图所示:

需要注意的是 PCIe Spec 并没有规定弹性缓存的具体位置,设计者可以将弹性缓存放在 8b/10b 解码器之前,也可以把弹性缓存放在 8b/10b 解码器之后。不过,Mindshare 的建议是将弹性缓存放置于 8b/10b 解码器之前的。

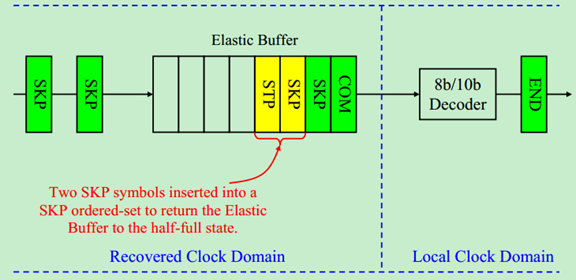

当本地时钟域的时钟(Local Clock)的速度比数据流通过 CDR 解析出的时钟(Recovered Clock)的时钟要快时,且弹性缓存即将被读空之前,可以向 SKP Ordered Set 中插入 1~2 个 SKP。如下图所示:

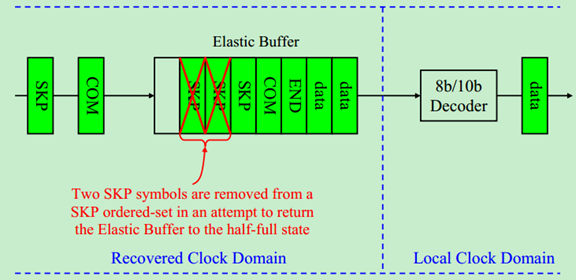

当本地时钟域的时钟(Local Clock)的速度比数据流通过 CDR 解析出的时钟(Recovered Clock)的时钟要慢时,且弹性缓存即将溢出之前,可以从 SKP Ordered Set 中移除 1~2 个 SKP 。如下图所示:

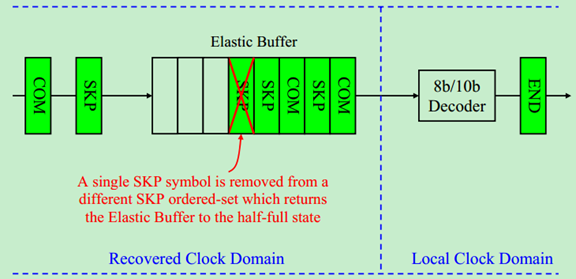

需要特别注意的是,Intel 提出的 PIPE 规范(并非 PCI-SIG 强制的规范,具体参考前面关于 PIPE 的文章)中,只允许每次从一个 SKP Ordered Set 中插入或者移除一个 SKP 。如果需要插入或者移除两个 SKP ,则需要对两个 SKP Ordered Set 进行操作。如下图所示:

PCIe 配置空间寄存器快速定位表

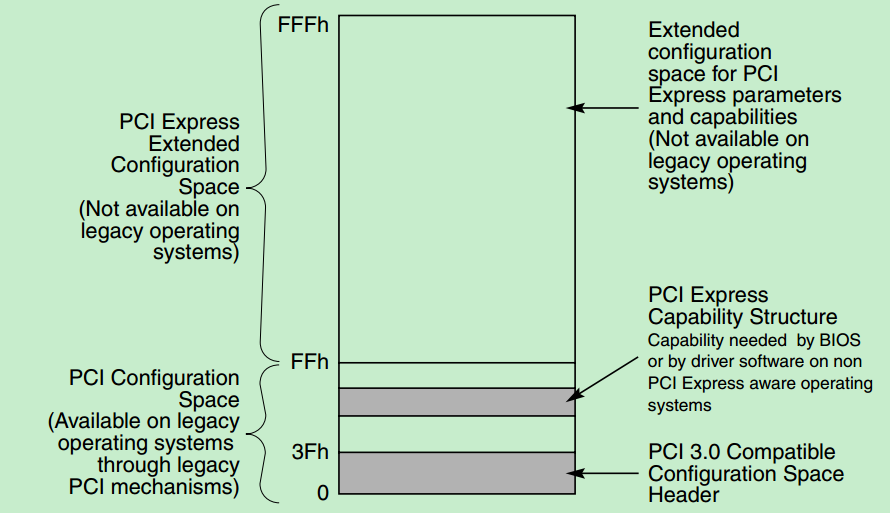

PCI Express 的配置空间结构图如下图所示,为了能够快速定位相关寄存器的描述在 PCIe Spec 中的位置,整理了一个表格,顺便分享到我的博客上。

注:这个表格是基于 PCIe Spec V2.0 的,也就是 Gen2 的 Spec 正式版。其中有很多空白的地方,只是在 Gen2 中没有明确定义,但是在 Gen3/Gen4 可能会被用到的。具体以 Spec 为准。

转载链接

- 热插拔简要介绍

- PCI Express 物理层接口(PIPE)

- 弹性缓存(Elastic Buffer/ CTC Buffer)

- PCIe 配置空间寄存器快速定位表

☆

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/148275.html