大家好,欢迎来到IT知识分享网。

DRV8825Stepper Motor Controller IC

前言

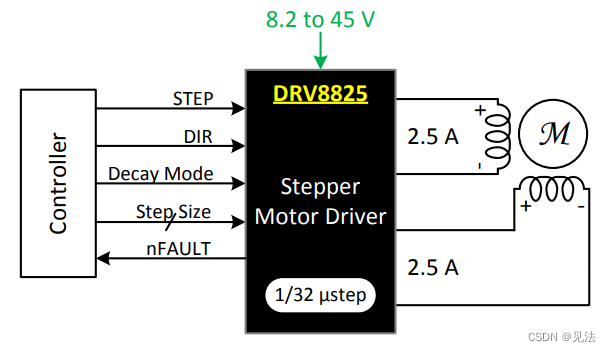

DRV8825是一个步进电机驱动IC芯片,内置了两个H桥和细分器(最高32细分)。

一、DRV8825的Features

- 内置细分器,最高支持32细分;

- 具有3种电流衰减模式:Mixed、Slow、Fast;

- 工作电压:8.2Vto45V;

- 所能提供的最大电机驱动电流:2.5A@24V@25°C。

- 简单的STEP、DIR接口(可供单片机控制);

- 具备低电流睡眠模式;

- 内置3.3V参考电压输出(点位脚);

- 保护电路:过流保护(OCP)、热关断(TSD)、欠压锁定(UVLO)、故障状态指示引脚(nFAULT)

二、DRV8825的使用

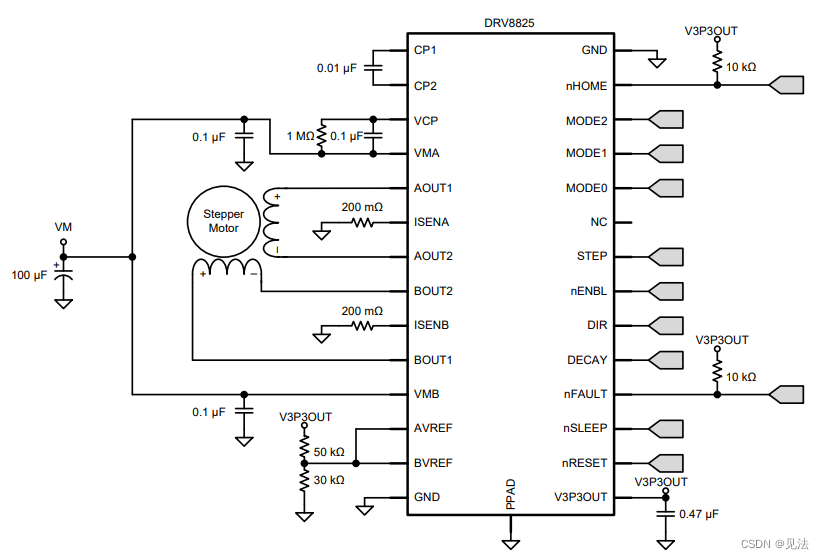

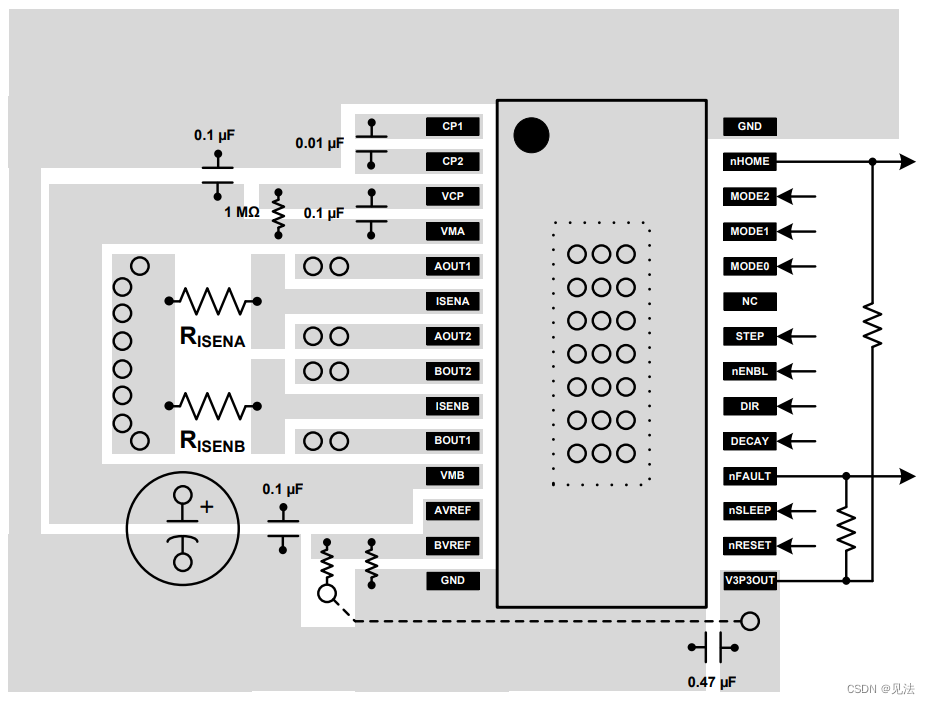

1、 简化的原理图

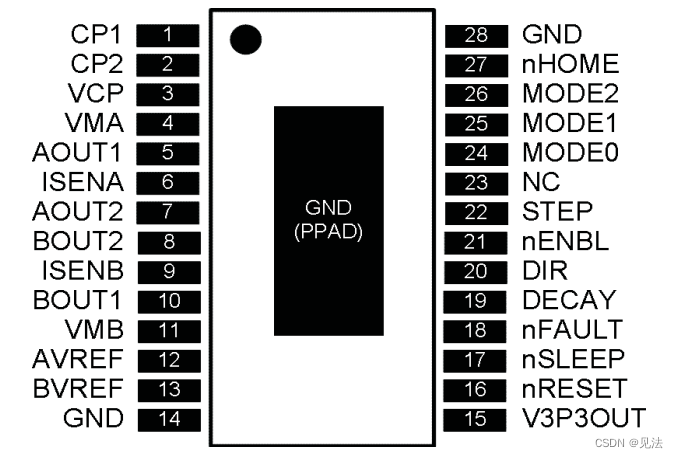

2、 引脚分布

| PinName | Description |

|---|---|

| CP1、CP2 | 电荷泵引脚,用一个0.01μF@50V的电容连接 |

| GND | 地 |

| VCP | High-side gate driver voltage,Connect a 0.1-μF 16-V ceramic capacitor and a 1-MΩ resistor to VM。 |

| VMA、VMB | H桥A和H桥B的电压供应引脚 |

| V3P3OUT | Bypass to GND with a 0.47-μF 6.3-V ceramic capacitor.可以用于为VREF供应电位 |

| AVREF、BVREF | 桥A、桥B的电流设定参考输入,可接上述V3P3OUT,通常情况下AVREF与BVREF相等 |

| DECAY | 驱动回路电流衰减模式,共三种:慢、快、混合,其内部上拉和内部下拉。 |

| DIR | 设置步进的方向。内部下拉。 |

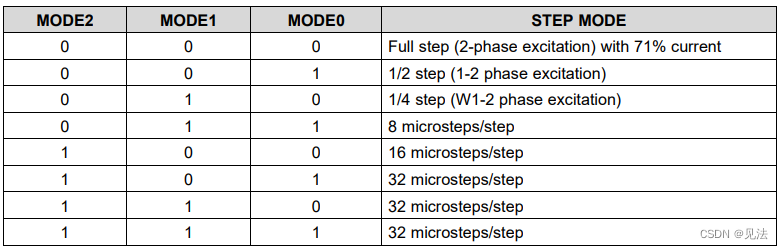

| MODE0、MODE1、MODE2 | 三者共同组成一个3位二进制数,DRV8825有6种细分模式可供选择,内部下拉。 |

| NC | No connect |

| nENBL | Enable input,高电平以禁用设备输出和所引起操作,内部下拉。 |

| nRESET | 低电平激活,初始化索引器,并且禁用H桥输出,内部下拉。⭐ |

| nSLEEP | 睡眠模式引脚,低电平激活DRV8825进入低能耗睡眠模式,内部下拉。 |

| STEP | Step input.上升沿使得所引起移动一步,内部下拉 |

| nFAULT | 开漏输出,当DRV8825出现故障后,引脚置低电平 |

| nHome | 开漏输出,Logic low when at home state of step table |

| AOUT1、AOUT2;BOUT1、BOUT2 | 接到四线两相步进电机上。A、B分别对应电机的两个windng |

| ISENA、ISENB | A桥、B桥的接地端,或插入一个测流电阻实现电流测量 |

3、绝对值

| ValueName | MIN | MAX | UNIT |

|---|---|---|---|

| VM | -0.1 | 47 | V |

| Digital Pin Voltage | -0.5 | 7 | V |

| 略 | |||

| ······ |

3.1 建议工作值

| ValueName | MIN | MAX | UNIT |

|---|---|---|---|

| VMx | 8.2 | 45 | V |

| VREF | 1 | 3.5 | V |

| Iv3p3 | 0 | 1 | mA |

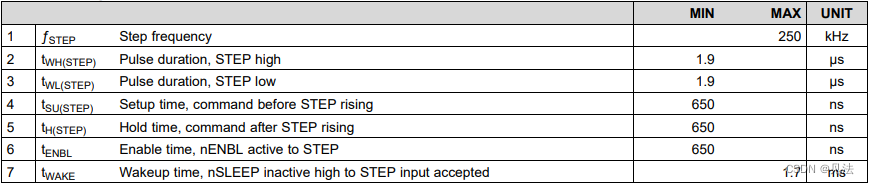

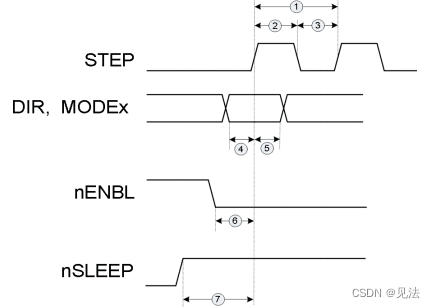

4、时间要求

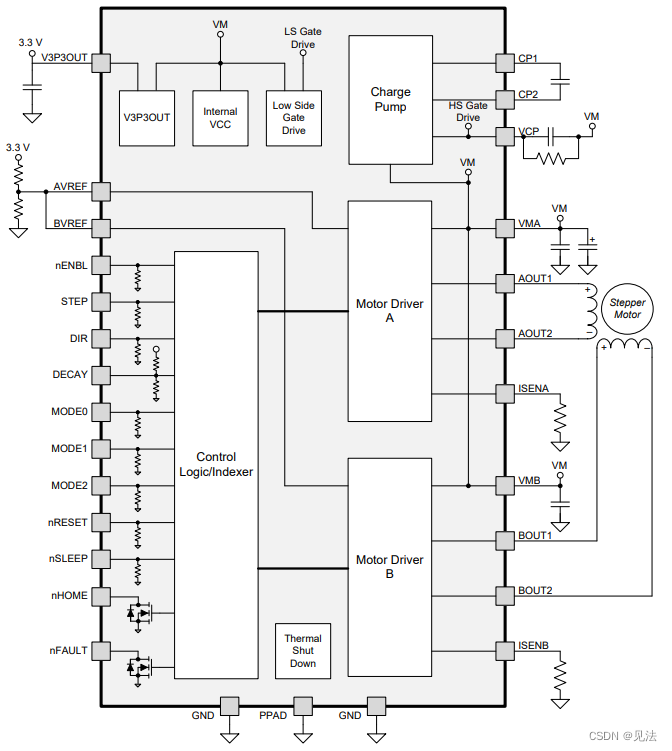

5、内部框图

5.1 电流调节

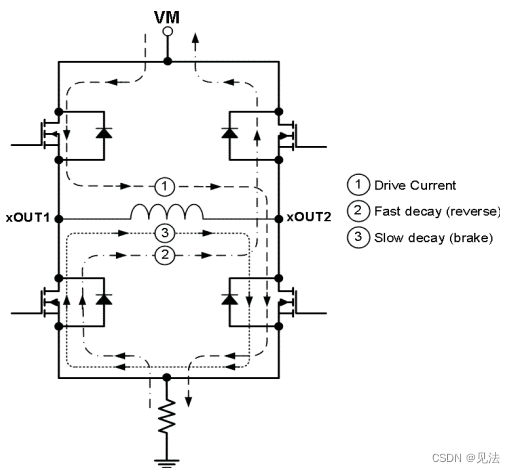

5.2 Decay Mode

DRV8825支持快速衰减、慢速衰减和混合衰减模式。慢速、快速或混合衰减模式由decay引脚的状态选择;逻辑低选择慢速衰减,打开选择混合衰减操作,逻辑高设置快速衰减模式。DECAY引脚具有一个约130 kΩ的内部上拉电阻器和一个约80 kΩ的内拉电阻器。如果引脚保持打开或未驱动,则设置混合衰减模式。

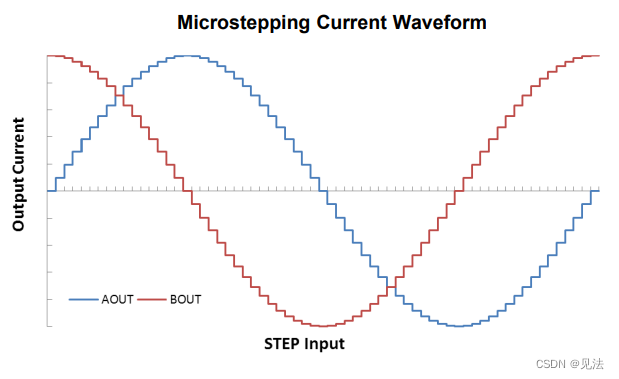

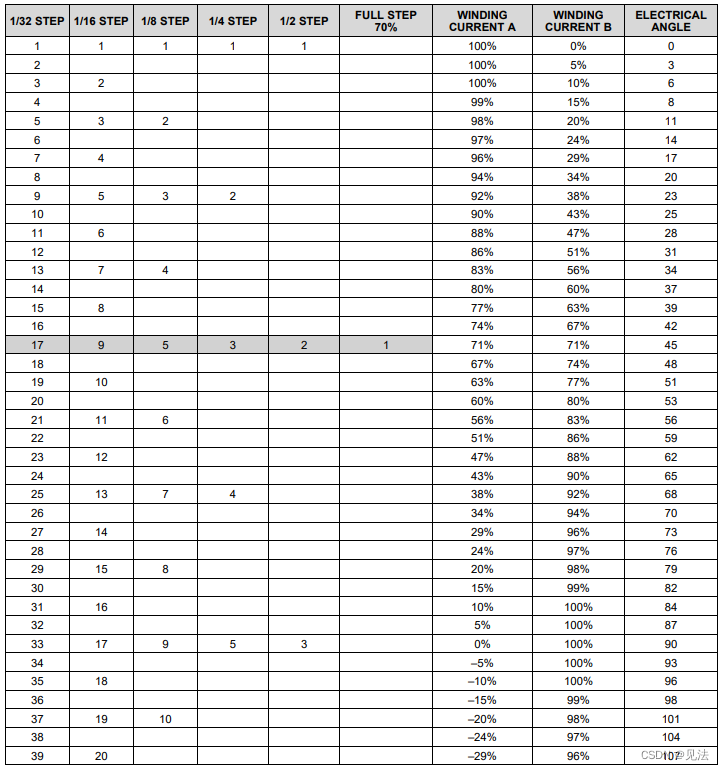

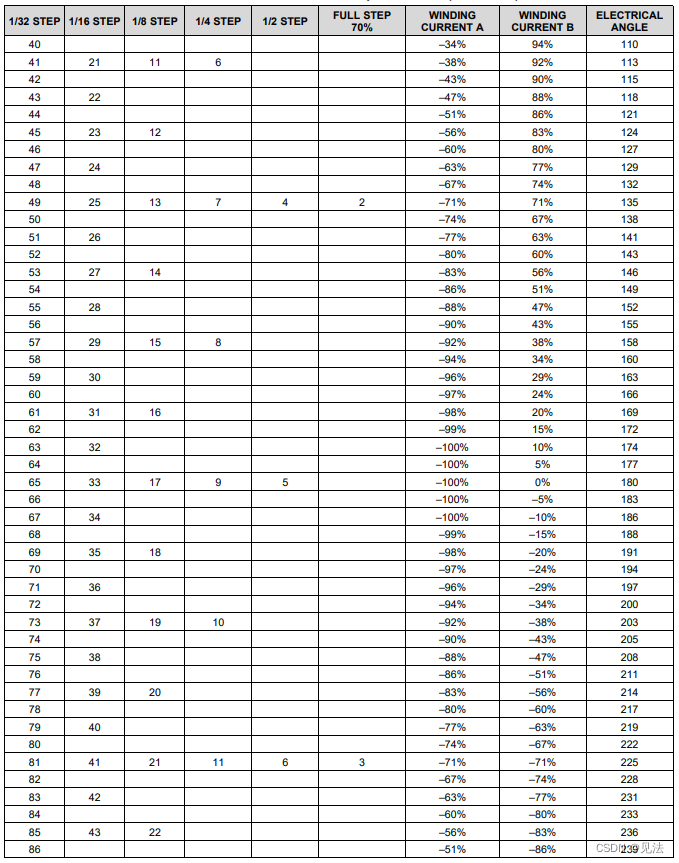

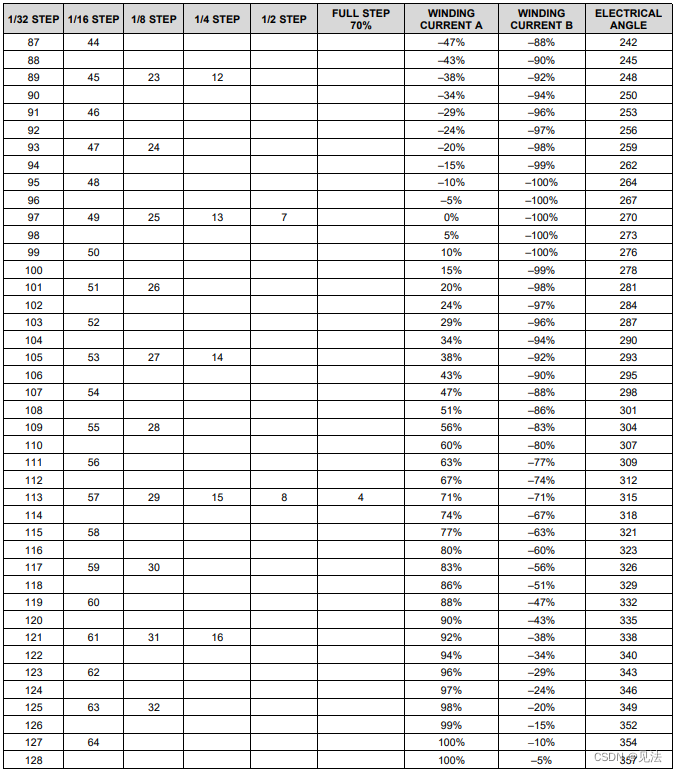

5.3 细分器

DRV8825中内置的索引器逻辑允许多种不同的步进配置。MODE0至MODE2引脚用于配置步进格式,如表所示。

5.4 nRESET, nENBL, and nSLEEP Operation

略 6 应用电路

6.1 典型电路

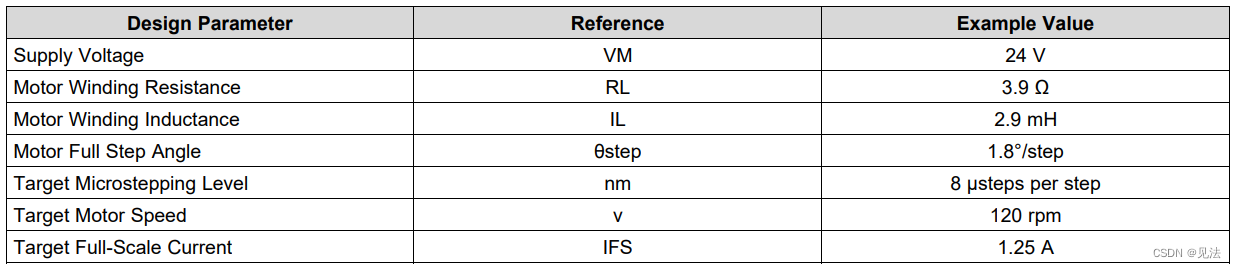

6.2 上述典型电路的设计要求

6.3 电路设计步骤

6.3.1 电机转速

配置DRV8825的第一步需要所需的电机速度和微步进水平。如果该应用需要恒定的电机速度,则必须将频率为ƒ步长的方波应用于IC的step引脚。

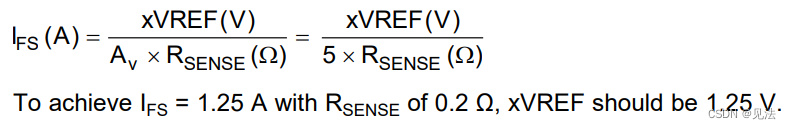

6.3.2 驱动电流的调节

6.3.3 驱动电流的衰减模式

7 供电建议

DRV8825的供电范围是8.2~45 V。两个额定为VMx的0.1µF陶瓷电容器必须分别放置在尽可能靠近VMA和VMB引脚的位置(每个引脚上一个)。除了局部去耦帽之外,还需要额外的体电容,并且必须根据应用要求确定其大小。

7.1 体电容(Bulk Capacitance)

略

7.2 上电时序

DRV8825对上电时序没有特殊要求,上电之后它就开始按照引脚状态开始工作。

8 Layout

8.2 Layout Guidelines

8.3 Layout Example

总结

文章比较详细的记载了有关DRV8825的资料。

作者能力有限,有些地方记载的不具体,请翻看DRV8825datasheet。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/112919.html