大家好,欢迎来到IT知识分享网。

GMAC:千兆网媒体访问控制

GMAC接口(1)——GMAC简介_daikaimiao的博客-CSDN博客_gmac

GMAC接口(2)——协议_daikaimiao的博客-CSDN博客_gmac协议

GMAC接口(3)——传输描述符_daikaimiao的博客-CSDN博客_gmac接口

GMAC系统框架(EMAC是百兆mac, GMAC是千兆mac)

以太网卡中数据链路层的芯片一般简称之为MAC控制器,物理层的芯片我们简称之为PHY。

- CPU内部集成了MAC和PHY (难度较高)

- CPU内部集成MAC,PHY采用独立芯片 (主流方案)

- CPU不集成MAC和PHY,MAC和PHY采用独立芯片或者集成芯片 (高端采用)

MAC控制器:主要完成数据链路层的IP数据报打包成网络帧并将数据发送给PHY。

PHY:主要完成速度协商,数字信号到模拟信号的转换最后把信号输出到网线上。

以太网基础-MAC和PHY_奇小葩的博客-CSDN博客_mac phy

趣谈网络协议栈,以太网基础MAC和PHY – 知乎

网卡(Network Interface Card,简称NIC),也称网络适配器,是电脑与局域网相互连接的设备。无论是普通电脑还是高端服务器,只要连接到局域网,就都需要安装一块网卡。如果有必要,一台电脑也可以同时安装两块或多块网卡。

电脑之间在进行相互通讯时,数据不是以流而是以帧的方式进行传输的。我们可以把帧看做是一种数据包,在数据包中不仅包含有数据信息,而且还包含有数据的发送地、接收地信息和数据的校验信息。

一个网卡主要包括OSI的最下面的两层,物理层和数据链路层

物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY

数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。数据链路层的芯片称之为MAC控制器

本文针对这两层进行相关的学习,总结整个系统的框架和物理上硬件组成原理,学习数据包的发送和接收的处理过程。

一,网卡系统框架结构

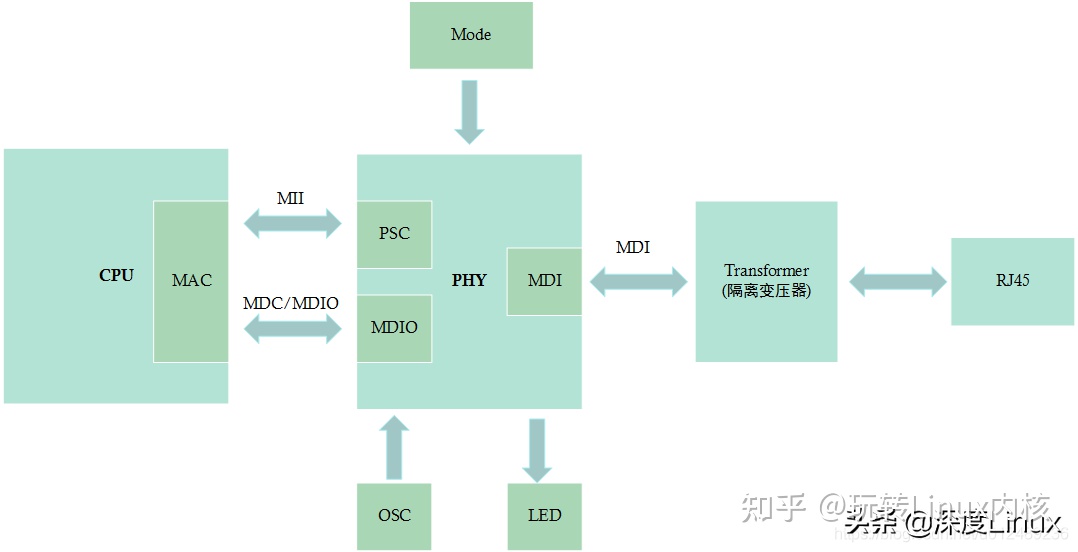

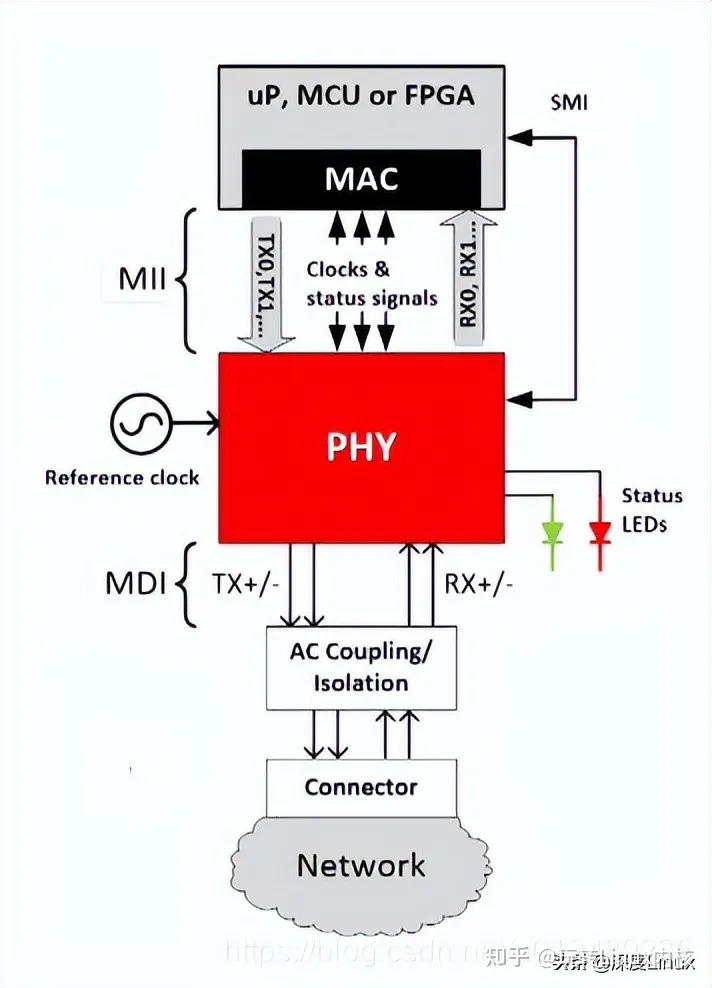

从硬件的角度来分析,以太网的电路接口一般由CPU、MAC(Media Access Control)控制器和物理层接口(physical Layer PHY)组成,如下图所示:

对于上述三部分,并不一定都是独立的芯片,主要有以下几种情况

- CPU内部集成了MAC和PHY (难度较高)

- CPU内部集成MAC,PHY采用独立芯片 (主流方案)

- CPU不集成MAC和PHY,MAC和PHY采用独立芯片或者集成芯片 (高端采用)

PHY整合了大量模拟硬件,而MAC是典型的全数字器件,芯片面积及模拟/数字混合架构是为什么先将MAC集成进微控制器而将PHY留在片外的原因。更灵活、密度更高的芯片技术已经可以实现MAC和PHY的单芯片整合

以常用的第二种:CPU内部集成MAC,PHY采用独立的芯片方案,虚线内表示CPU和MAC集成在一起,PHY芯片通过MII接口与CPU上的MAC互联。

对于这种方案,其硬件方案比独立的相对于更简单,PHY与MAC之间有以下两个重要的硬件接口

- MDIO总线接口,主要是完成CPU对于PHY芯片的寄存器配置

- MII总线接口,主要是完成数据收发相关的业务

当我们的PHY芯片发送数据,接受到MAC层发送过来的数字信号,然后转换成模拟信号,通过MDI接口传输出去。但是我们的网线传输的距离又很长,有时候需要送到100米甚至更远的地址,那么就会导致信号的流失。而且外网线与芯片直接相连的话,电磁感应和静电,也很容易导致芯片的损坏,所以就要使用网络变压器,其主要作用是

- 传输数据,它把PHY送出来的差分信号用差模耦合的线圈耦合滤波以增强信号,并且通过电磁场的转换耦合到不同电平的连接网线的另外一端

- 隔离网线连接的不同网络设备间的不同电平,以防止不同电压通过网线传输损坏设备

- 还能使芯片端与外部隔离,抗干扰能力大大增强,而且对芯片增加了很大的保护作用,保护PHY免遭由于电气失误而引起的损坏(如雷击)

网卡介绍——MAC与PHY的关系分析_li_wen01的博客-CSDN博客_mac phy

下图是网口结构简图.网口由CPU、MAC和PHY三部分组成.DMA控制器通常属于CPU的一部分,用虚线放在这里是为了表示DMA控制器可能会参与到网口数据传输中.

对于上述的三部分,并不一定都是独立的芯片,根据组合形式,可分为下列几种类型:

- CPU集成MAC与PHY;

- CPU集成MAC,PHY采用独立芯片;

- CPU不集成MAC与PHY,MAC与PHY采用独立芯片或者集成芯片;

本例中选用方案二做进一步说明,因为CPU总线接口很常见,通常都会做成可以像访问内存一样去访问,没必要拿出来说,而Mac与PHY之间的MII接口则需要多做些说明.

下图是采用方案二的网口结构图.虚框表示CPU,MAC集成在CPU中.PHY芯片通过MII接口与CPU上的Mac连接.

在软件上对网口的操作通常分为下面几步:

- 为数据收发分配内存;

- 初始化MAC寄存器;

- 初始化PHY寄存器(通过MIIM);

- 启动收发;

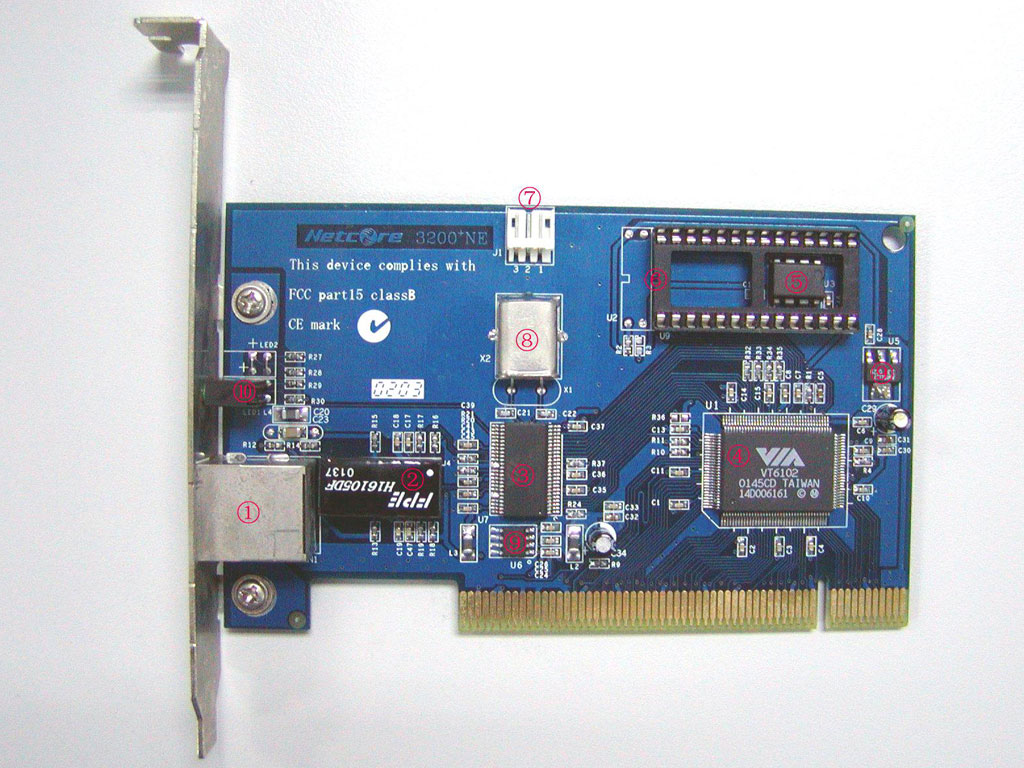

我们现在来看两个图

如上:MAC和PHY分开的以太网卡

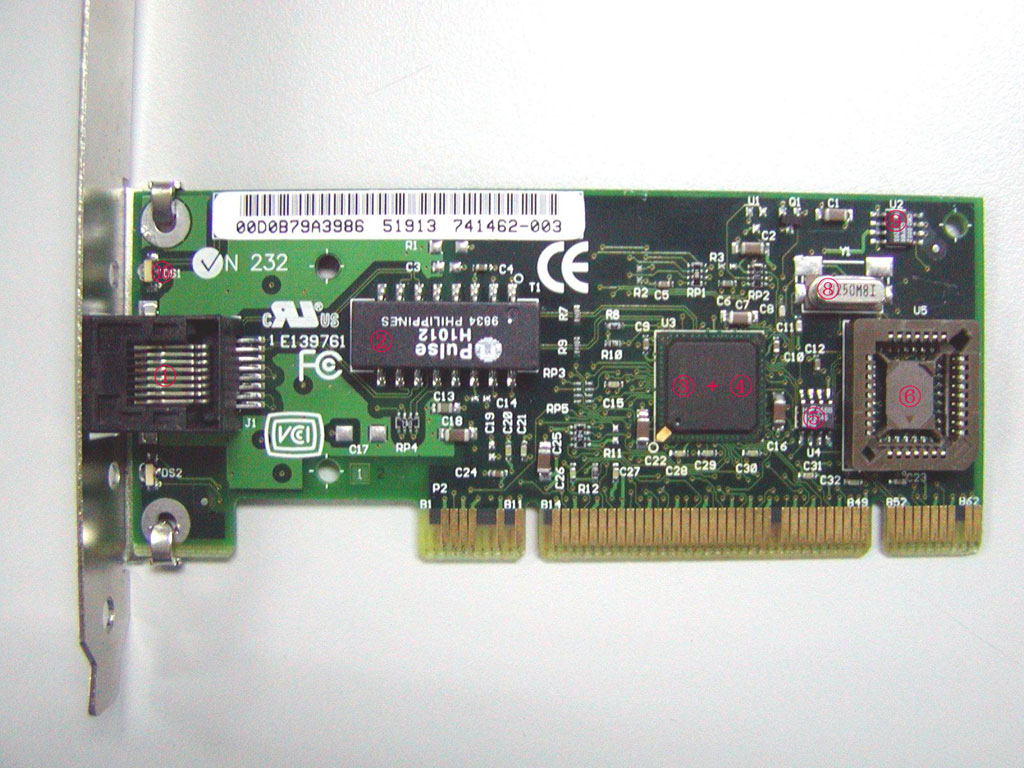

如上:MAC和PHY集成在一颗芯片的以太网卡

上图中各部件为:

①RJ-45接口

②Transformer(隔离变压器)

③PHY芯片

④MAC芯片

⑤EEPROM

⑥BOOTROM插槽

⑦WOL接头

⑧晶振

⑨电压转换芯片

⑩LED指示灯

网卡的功能主要有两个:一是将电脑的数据封装为帧,并通过网线(对无线网络来说就是电磁波)将数据发送到网络上去;二是接收网络上其它设备传过来的帧,并将帧重新组合成数据,发送到所在的电脑中.网卡能接收所有在网络上传输的信号,但正常情况下只接受发送到该电脑的帧和广播帧,将其余的帧丢弃.然后,传送到系统CPU做进一步处理.当电脑发送数据时,网卡等待合适的时间将分组插入到数据流中.接收系统通知电脑消息是否完整地到达,如果出现问题,将要求对方重新发送.

二,MAC控制器、PHY介绍

MAC

PHY

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是CRC.对于100BaseTX因为使用4B/5B编码,每4bit就增加1bit的检错码),然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去.收数据时的流程反之.PHY还有个重要的功能就是实现CSMA/CD的部分功能.它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去.如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据.这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突.

PHY还提供了和对端设备连接的重要功能并通过LED灯显示出自己目前的连接的状态和工作状态让我们知道.当我们给网卡接入网线的时候,PHY不断发出的脉冲信号检测到对端有设备,它们通过标准的”语言”交流,互相协商并却定连接速度、双工模式、是否采用流控等.通常情况下,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式.这个技术被称为AutoNegotiation或者NWAY,它们是一个意思–自动协商.

具体传输过程为,发送数据时,网卡首先侦听介质上是否有载波(载波由电压指示),如果有,则认为其他站点正在传送信息,继续侦听介质.一旦通信介质在一定时间段内(称为帧间缝隙IFG=9.6微秒)是安静的,即没有被其他站点占用,则开始进行帧数据发送,同时继续侦听通信介质,以检测冲突.在发送数据期间,如果检测到冲突,则立即停止该次发送,并向介质发送一个“阻塞”信号,告知其他站点已经发生冲突,从而丢弃那些可能一直在接收的受到损坏的帧数据,并等待一段随机时间(CSMA/CD确定等待时间的算法是二进制指数退避算法).在等待一段随机时间后,再进行新的发送.如果重传多次后(大于16次)仍发生冲突,就放弃发送.接收时,网卡浏览介质上传输的每个帧,如果其长度小于64字节,则认为是冲突碎片.如果接收到的帧不是冲突碎片且目的地址是本地地址,则对帧进行完整性校验,如果帧长度大于1518字节(称为超长帧,可能由错误的LAN驱动程序或干扰造成)或未能通过CRC校验,则认为该帧发生了畸变.通过校验的帧被认为是有效的,网卡将它接收下来进行本地处理.

接口

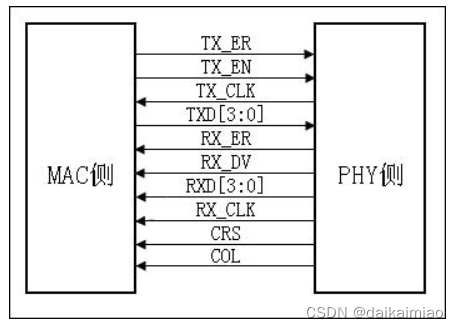

MII(Medium Independent Interface, 媒体独立接口): MII 支持 10Mbps 和 100Mbps 的操作,数据位宽为 4 位

在 100Mbps 传输速率下,时钟频率为 25Mhz

在 10Mbps 传输速率下,时钟频率为 2.5Mhz

RMII(Reduced MII): RMII 是 MII 的简化版, 数据位宽为 2 位

在 100Mbps 传输速率下,时钟频率为 50Mhz

在 10Mbps 传输速率下,时钟频率为 5Mhz

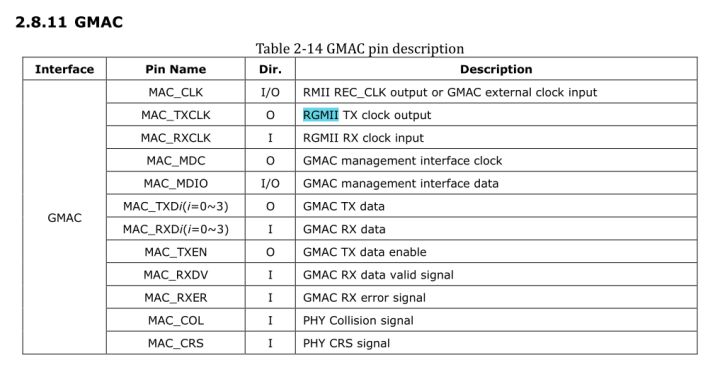

GMII(Gigabit MII): GMII 接口向下兼容 MII 接口, 支持 10Mbps、 100Mbps 和 1000Mbps 的操作,数据位宽为 8 位

在 1000Mbps 传输速率下,时钟频率为 125Mhz

在 100Mbps 传输速率下,时钟频率为 25Mhz

在 10Mbps 传输速率下,时钟频率为 2.5Mhz

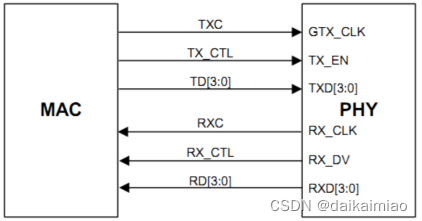

RGMII(Reduced GMII): RGMII 是 GMII 的简化版,数据位宽为 4 位

在 1000Mbps 传输速率下,时钟频率为 125Mhz,在时钟的上下沿同时采样数据

在 100Mbps传输速率下,时钟频率为25MHz,为单个时钟沿采样

在 10Mbps传输速率下,时钟频率为2.5MHz,为单个时钟沿采样

在千兆以太网中,常用的接口为 RGMII 和 GMII 接口。 RGMII 接口的优势是同时适用于10M/100M/1000Mbps 通信速率,同时占用的引脚数较少。但 RGMII 接口也有其缺点,就是在 PCB 布线时需要尽可能对时钟、控制和数据线进行等长处理,且时序约束相对也更为严格。

MII

MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。MII管理接口是个双信号接口,一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。其管理是使用SMI(Serial Management Interface)总线通过读写PHY的寄存器来完成的。PHY里面的部分寄存器是IEEE定义的,这样PHY把自己的目前的状态反映到寄存器里面,MAC通过SMI总线不断的读取PHY的状态寄存器以得知目前PHY的状态,例如连接速度,双工的能力等。当然也可以通过SMI设置PHY的寄存器达到控制的目的,例如流控的打开关闭,自协商模式还是强制模式等。不论是物理连接的MII总线和SMI总线还是PHY的状态寄存器和控制寄存器都是有IEEE的规范的,因此不同公司的MAC和PHY一样可以协调工作。当然为了配合不同公司的PHY的自己特有的一些功能,驱动需要做相应的修改。

PHY是物理接口收发器,它实现物理层。包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。

GMII

RMII

GMAC是为了满足千兆网传输而发展起来的,它是构成千兆网必备的条件之一。GMAC在七层ISO标准中属于数据链路层,它对逻辑链路和物理链路之间的通道进行控制和协调,可以连接各种不同物理媒介,不同物理媒介有不同的GMAC标准,GMAC的标准由IEEE802工作组制定。

GMAC可以分为四个部分:帧发送(Frame Transmission)、帧接收(Frame Reception)、GMAC控制(GMAC Control)、媒体独立接口管理(GMII)。

帧发送:接收GMAC客户(上层协议)传下来的数据,在数据段头尾加上一些控制信息,组成一个以太网数据帧,并将该数据帧以位数据流的形式传送到物理层,以待发送。

帧接收:接收从物理层来的位数据流,在接收完一帧的数据后,检查该帧是否有效(如目的地址、计算校验码、字节对齐等),若有效就去除数据帧的头尾将数据字段提交给上层协议,否则就丢弃该数据帧。

GMAC控制:用于全双工模式下控制帧的生成、检测,它处在主机和发送、接收模块之间,对普通的数据帧来说是透明的。

媒体独立接口管理:控制物理层的输入输出操作,检查物理层的状态信息。

3 GMAC工作模式

GMAC本身并不会接收和发送网络数据,而只是对物理层的接收和发送的行为进行控制。物理层是真正实现数据收发功能的地方,但它不会对数据进行任何区分和处理,当发现网络上有数据,它就把数据从网络上取下来送给GMAC,当GMAC有数据给它时,它就把数据放到网络上。GMAC的作用是把物理层送上来的数据进行区分,如果数据包的目的地址是本机,就把数据包适当处理后提交给上层协议,如果不是就丢弃该数据包,在发送时,GMAC在待发送的数据包上加一些信息后直接交给物理层。实际上GMAC和PHY(物理层)之间的接口是标准的,不管是什么物理网络,MAC都可以通过标准接口对物理层的行为进行控制,而且一个GMAC可以同时管理多个PHY的行为。

GMAC的工作方式有半双工和全双工两种。

半双工模式:GMAC client将数据传给GMAC后,GMAC先给数据加上Preamble、FSD、FCS,组成以太网帧,然后检查载波侦听信号(CRS),若有载波信号,表示有数据正在 本地网段上传播,就等待直到载波信号消失,载波信号消失后,GMAC还要等待一个帧间延时(interFrame Spacing),若在帧间延时期间,一直没有载波信号,该以太网帧就可以开始向物理层传输。

当物理层在传送数据的过程中,网络上同时也有其它数据在传输,就会产生冲突,(collision),物理层检查到冲突后,向GMAC发送冲突信息,GMAC检查是normal collision还是late collision,如果是normal collision,停止传输数据,传送32位的jam数据流,然后等待一个随机时间段后进行重传,如果是late collision,在传送jam数据流后丢弃该数据包。如果重传的次数达到16次,丢弃该数据包。接收数据时,当GMAC收到一帧数据时,首先检查目的地址是否正确,然后检查以太网帧是否8byte对齐(位长度是8的倍数),若没有对齐,将FCS前的数据段截取成字节对齐,接着根据收的数据产生CRC,与收到的FCS比较,不相等就丢弃该帧。最后去除Preamble、FSD和FCS,将数据传给上层协议。

全双工模式:GMAC从GMAC Client接收到数据后,不需要载波侦听和冲突检测,直接向物理层传送,其它操作与半双工相同。

4 GAMC中几个重要概念介绍

4.1 载波侦听

(适用于半双工)在GMAC开始向物理层传输数据之前,GMAC进行载波侦听,如果物理网路上有载波,说明有数据正在传输,本地数据必须要等待,当侦听到载波消失,本地数据就可以准备发送,但GSMA/CD协议规定两帧数据之间必须有inter-FrameGap(或interFrameSpacing),以便使整个网路上的其它设备有足够的时间恢复状态,所以载波消失后还要等待interFrameGap的时间,当inter-FrameGap结束而且其间一直没有载波时,数据就可以开始发送了,如果在interFrameGap其间侦听到载波信号,本地数据重新开始等待过程。

4.2 冲突检测

(适用于半双工)在数据向物理层传输的过程中,网络上可能会同时出现两组数据在传输,当两组数据在网路上相遇时,就发生冲突(collision),GMAC检测到冲突后,判别冲突的类型:

(1)normal collision:冲突发生在以太网帧的前512bit内,它又可分为两类:

①冲突发生在(Preamble+FSD)之内,则将(Preamble+FSD)传送完,接着传送一个32bit的jam数据流,然后开始back off(等待重传);

②站突发生在(Preamble+FSD)之后,则立即停止当前的数据传送,接着传送一个32bit的jam数据流,然后开始back off(等待重传);

(2)late collision:突冲发生在以太网帧的512bit之后,结果冲突发生,则立即停止当前的数据传送,接着传送一个32bit的jam数据流,并且将该数据包丢弃,通知上层协议发生late collision(寄存器置位);

* * * *传送jam数据流是为了保证本地网路的值是任意的,只要求不是有意的使其等于已经传送数据的CRC。

4.3 Slot Time

对于半双工来说,这是一个很重要的概念。因为半双工模式下工作时会出现冲突,就要求当冲突出现时网路上的每个设备都能检测到,所以CSMA/CD规定了与物理层紧密联系的Slot Time。

4.4 Interframe Gap(Interframe Spacing)

连续两帧之间的空闲时间,用于设备恢复,以便下一帧数据的接收,长度为96bit时(24个时钟周期),任何一个以太网帧,则在传输前都要等待InterframeGap。InterframeGap分成0.06us和0.036us两个部分,如果在前面0.06us内检测到载波,停止等待,直到载波消失再重新开始等待InterframeGap,如果在后面的0.036us内检测到载波,忽略该载波信号。InterframeGap使网路上的各个设备都有相同的机会获得网路。

4.5 Back off

当发生normal collision时,就需要back off,等待数据重传,back off实际上是一个等待的过程,等待的时间r是0和二进制递增值之间的随机数,如果数据帧是第n次重传(前面n-1次都发生冲突,n≤16),k=min(n,10),二进制递增值就是2k,所以随机数值的范围为0≤r<2k,当本地数据等待r个Slog Time后,就可以准备重传数据(需要再等待interFrameGap)。

4.6 Pause Frame

控制帧的一种(也是目前唯一的控制帧),在全双工模式下,A、B之间进行通信,当A的数据传送很快,造成B出现拥塞状况的时候,B可以向A发送一个Pause Frame,要求A暂停发送数据,A收到暂停帧后,就停止数据发送,暂停的时间有Pause Frame中的字段决定,当暂停时间结束时,A继续传送数据。暂停帧是控制帧的一种,所以Length/Type的值为h8808(控制帧类型),操作码为h0001(表示暂停),16bit的参数决定暂停的时间,单位:Slot Time,范围:h0000-hffff。在暂停期间,暂停帧仍旧能够发送和接收,若A处于暂停状态,又接收到B的一个暂停帧,则A开始等待新的暂停时间,若新的暂停时间为0,则立即恢复以前的状态继续发送数据,所以发送一个0时间的暂停帧可以取消对方的暂停状态。

4.7 无效数据帧

下面几种情况的数据帧是无效的:

①收到的数据帧的长度和Length/Type(表示长度)的值不相等;

②收到的数据帧的长度不是整数个字节,在这种情况下,要进行字节对齐截取成最近的整数个字节;

③GMAC根据数据帧产生的CRC校验码与数据帧中的FCS不等(一般用Magic Number来检测);

5 以太网帧的格式

①Preamble:该字段为7个’b,数值没有实际的意义,只是让物理层做好接收数据的准备;

②SFD(start framc delimiter):紧跟着Preamble,固定值’b,表示数据帧开始;

③DA(dest.MAC address):以太网帧的目的地址,可以是单机地址,也可以使多播、广播地址;

④SA(source MAC address):以太网帧的源地址,单机地址,如果GMAC Client给GMAC传输的数据帧中SA为空,GMAC必须填充SA;

⑤Length/Type:当该值小于1536时表示数据段的长度,当大于等于1536时表示上层协议的类型,此时传送的以太网帧都是固定长度的(相应于帧类型),一般用于控制等特殊用途;

⑥GMAC Client Data:上层协议的数据字段;

⑦Pad:填充字段,当GMAC Client Data的长度小于46b时,由于规定了最小以太网帧长度,所以必须对GMAC Client Data进行填充(padding),使其达到48b,填充的内容任意;

⑧FCS(frame check sequence):CRC字段,32 b CRC校验码由802.3规定的校验公式决定,作用范围是从DA字段到Pad字段(如果有的话);

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/135721.html