大家好,欢迎来到IT知识分享网。

一、ARM异常处理(一)

(一)注意事项

学习处理器的两大方面:指令集和异常处理。

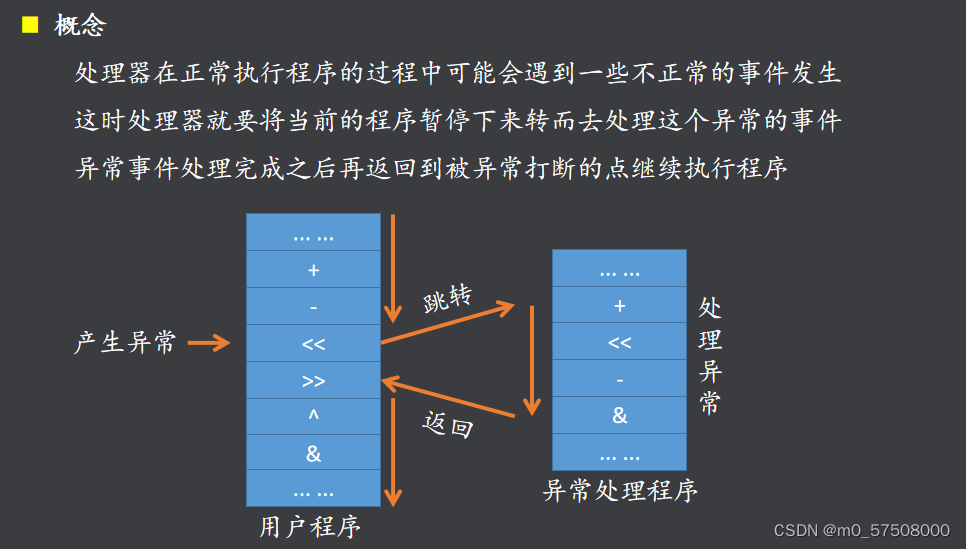

(二)异常的概念

处理器在正常执行过程中遇到一些不正常的事,中断程序处理异常,返回断点继续执行。类似于应用层的信号机制。

处理异常的过程也是执行程序,执行异常处理程序。

异常处理程序也是程序员自己写的。

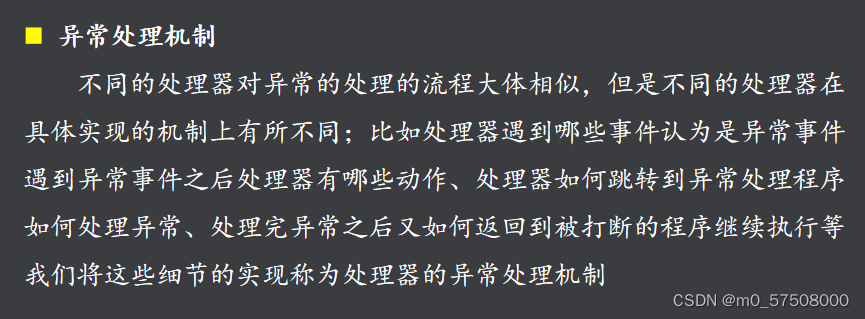

(三)异常处理机制

所有处理器都有异常处理,流程相似,异常事件不同,细节不同,不同CPU如何处理异常称为异常处理机制。

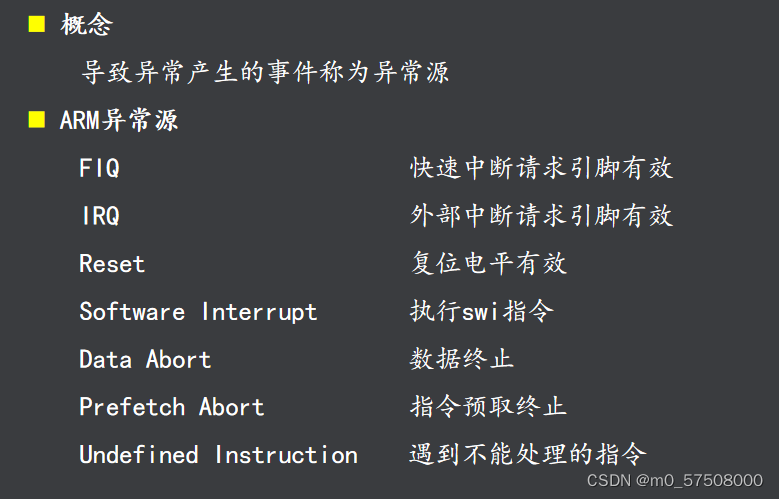

(四)异常源

1、FIQ/IRQ

一般是由外部硬件产生,比如按键。FIQ响应速度更快,优先级更高。

2、Reset

复位电平有效。

3、Software Interrupt

软中断,由软件或指令,自中断。

4、Data Abort

数据终止,读取内存出现问题,内存地址出错等。

5、Prefetch Abort

指令预取终止,指令地址不对,指令为空等。

6、Undefined Instruction

译码过程遇到不能处理的指令,译码器执行不了或者不认识

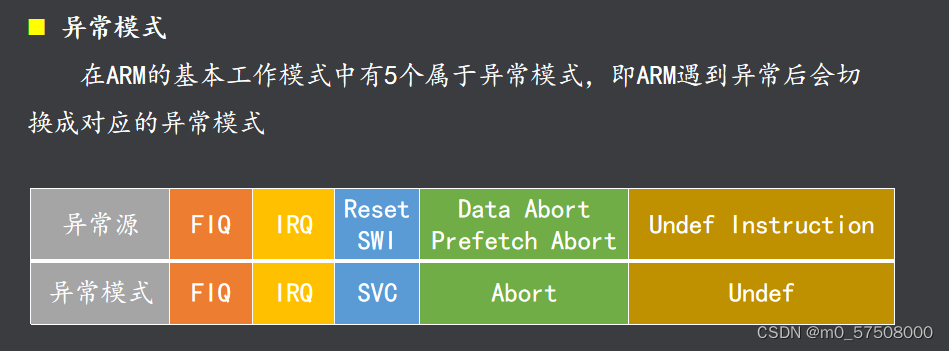

注意区分ARM的8个模式和7个异常源

处理器遇到异常源会进入异常模式

7、异常源和异常模式的对应

二、ARM异常处理(二)

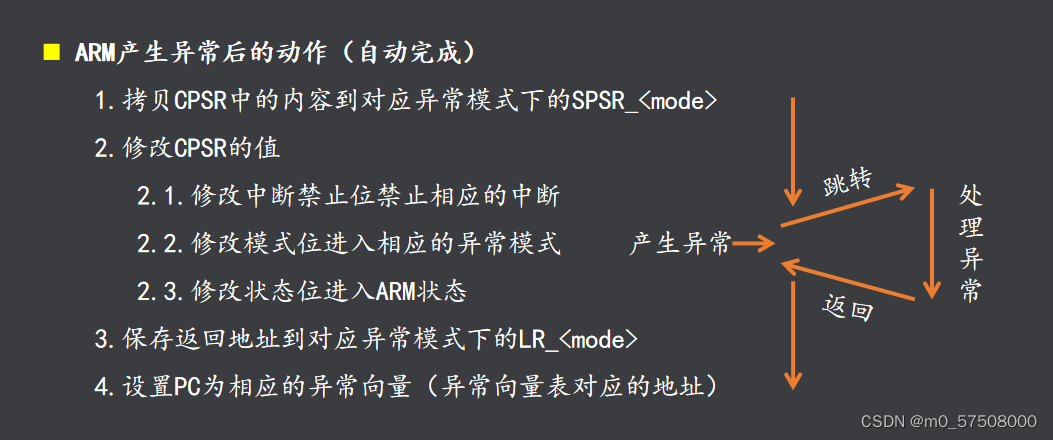

(一)ARM异常处理流程

1、保存CPSR(处理异常前,备份当前状态)到对应异常模式的SPSR_<mode>

2、修改CPSR(修改成异常模式)

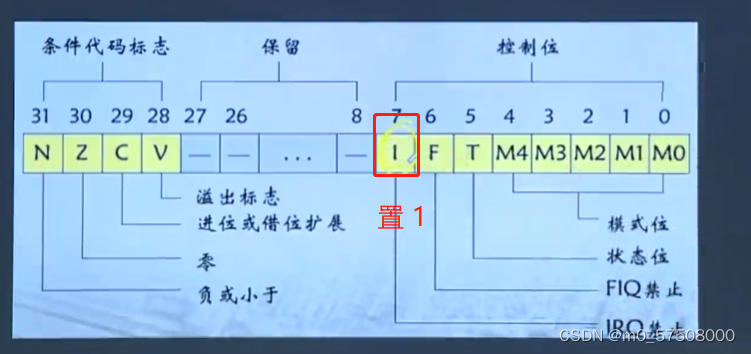

1)修改中断禁止位禁止相应的中断(异常处理过程中阻塞其他中断)

例:IRQ中断时

但是高优先级可以打断低优先级,如果进入IRQ,会阻塞其他IRQ,但可以被FIQ中断,处理完FIQ,返回处理IRQ,处理完,退出异常模式,回到刚刚执行的程序。

FIQ会同时阻塞FIQ和IRQ。

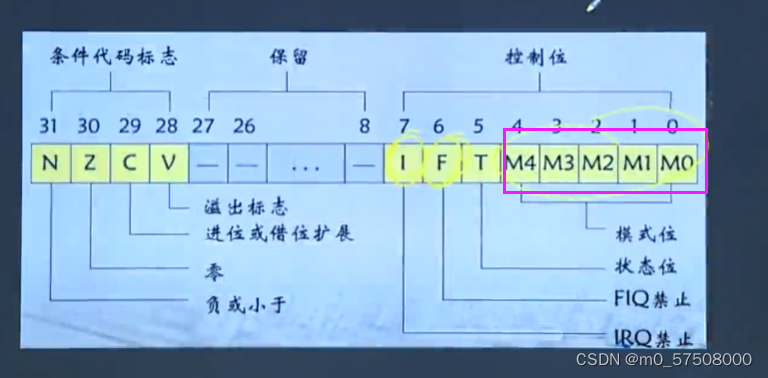

2)修改模式位进入相应的异常模式

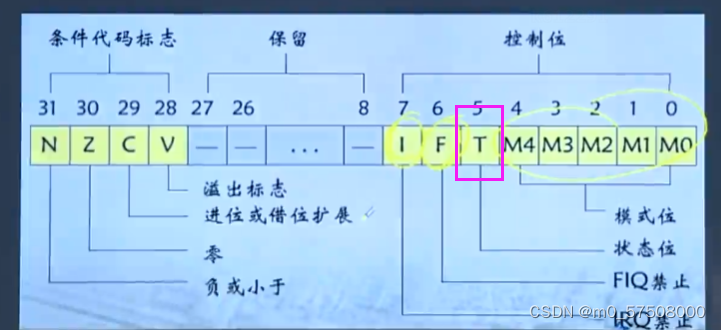

3)修改状态位进入ARM模式

T = 0 ARM模式

T = 1 Thumb模式

处理异常只能在ARM模式下

3、保存返回地址到对应异常模式下的LR_<mode>

LR在发生异常时自动保存正在执行的程序的下一条指令地址,不同异常模式对应不同的LR

4、设置PC为相应的异常向量(异常向量表对应的地址)

修改PC为异常处理程序的地址,但是异常处理程序的存储位置不知道,所以PC实际上跳转的位置是异常向量表

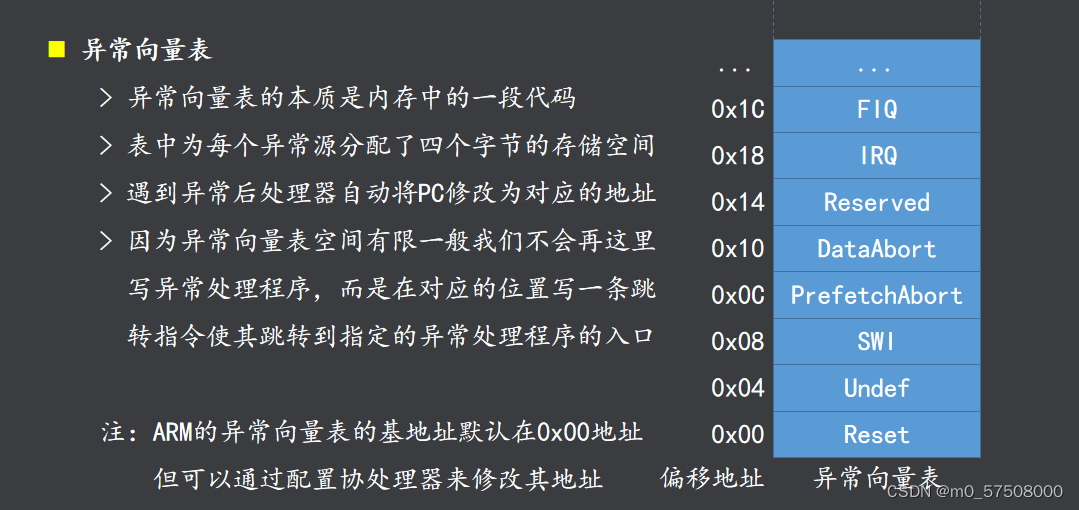

(二)异常向量表

32字节 异常向量表中存放的是跳转指令,跳转到指定的异常处理程序的入口

Cortex-A处理器异常向量表可以通过配置协处理器修改地址,修改基地址,再通过偏移量找到对应的异常模式

(三)异常返回

(四)IRQ异常举例

三、ARM异常处理(三)

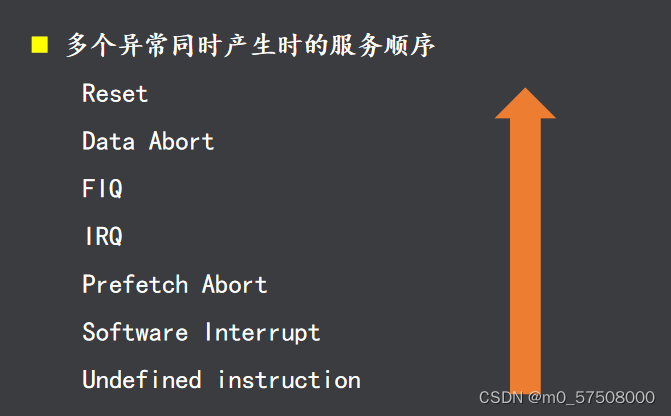

(一)异常优先级

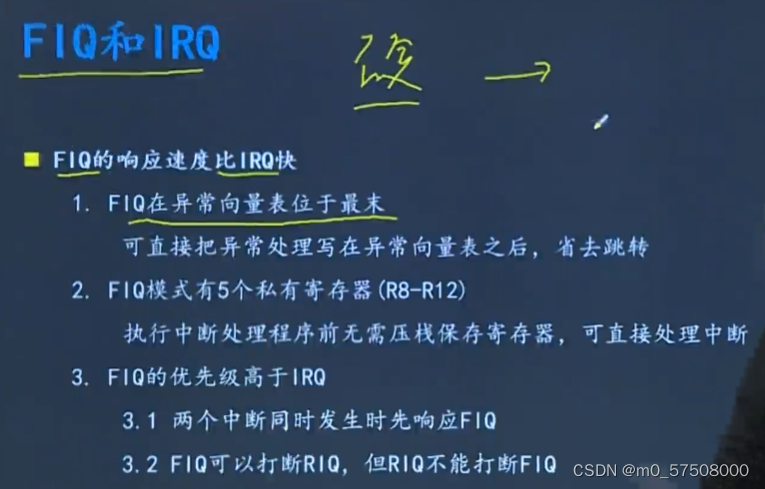

(二)FIQ和RIQ

FIQ响应速度比IRQ快

1、FIQ位于异常向量表的末端,可以把异常处理程序写在异常向量表之后,省去跳转

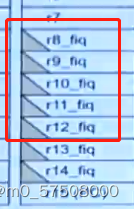

2、FIQ模式有5个私有寄存器(R8-R12)

省去了等待公用寄存器的时间,不需要压栈出栈

3、FIQ可以打断IRQ

四、ARM微架构

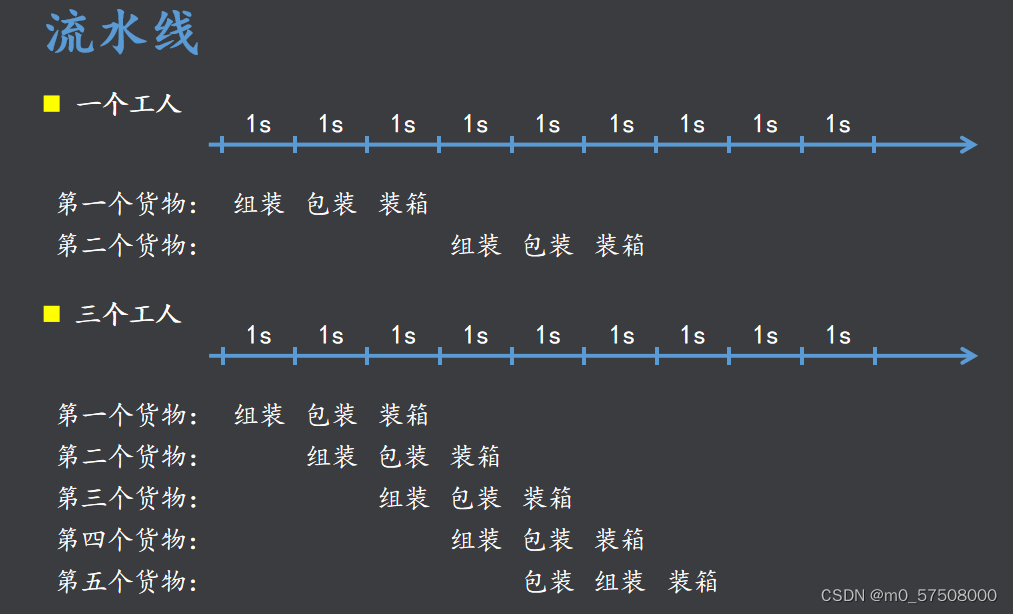

(一)流水线

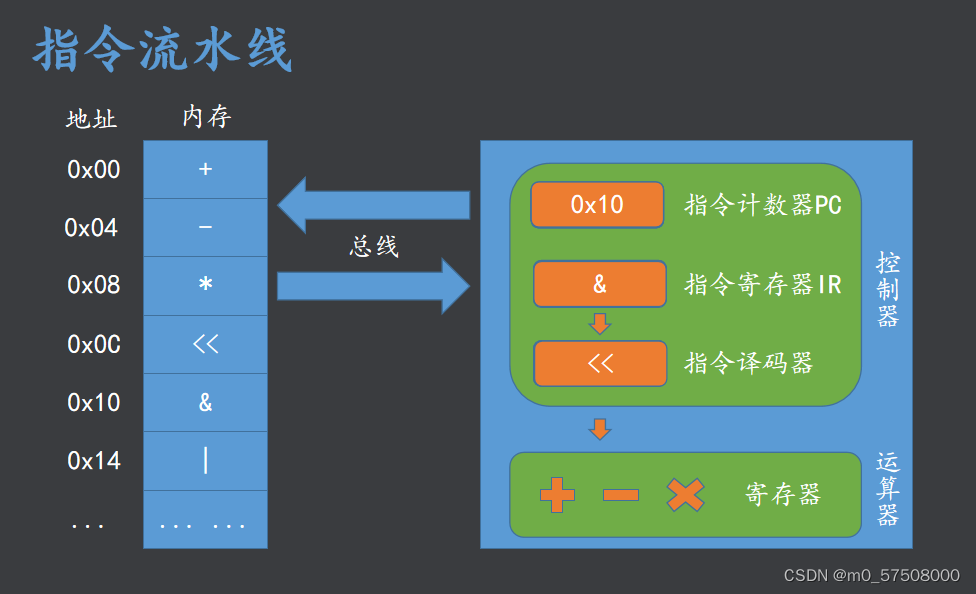

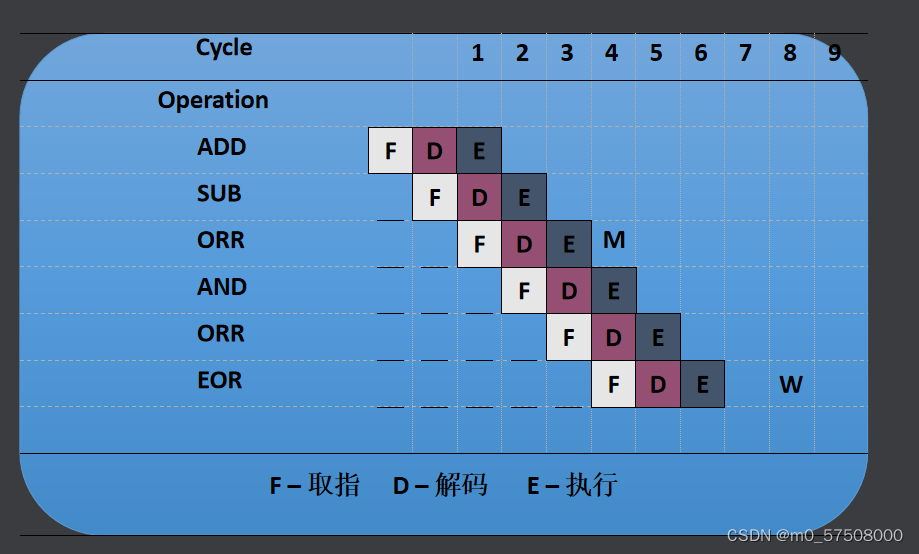

(二)指令流水线

1、取址:PC,IR

2、译码:译码器

3、执行:运算器

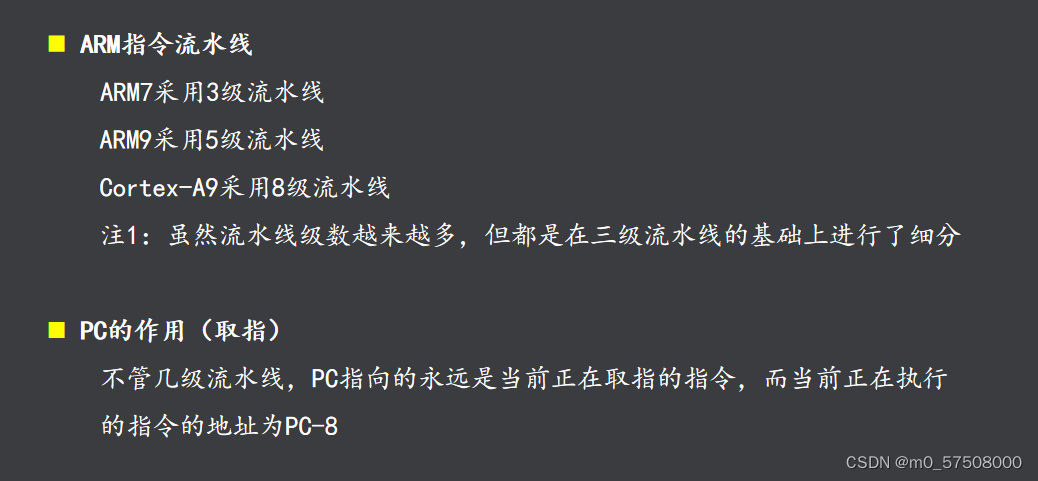

处理器越高级,流水线越细

PC指向的永远是正在取址的指令,而当前正在执行的指令是PC-8,正在译码的指令是PC-4

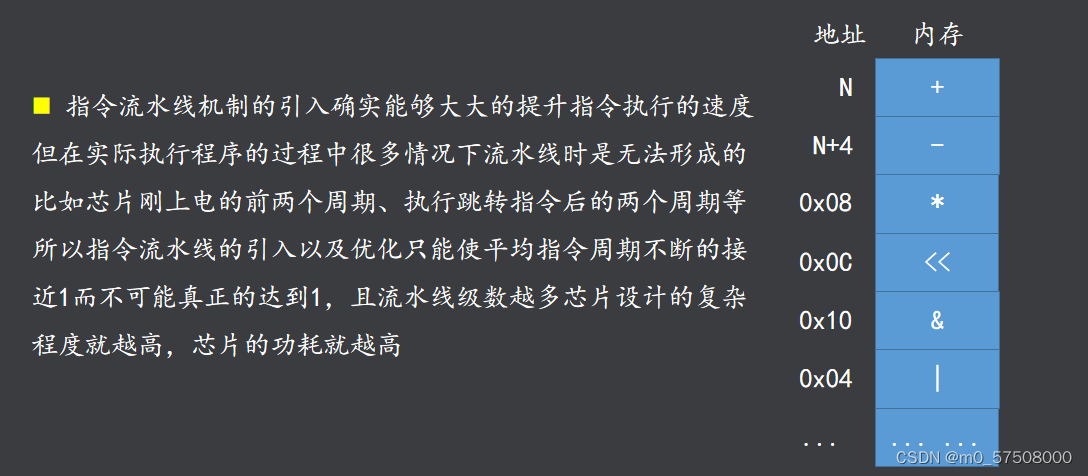

流水线级数越多,芯片越复杂,功耗越大

复杂指令集,指令越多,电路越复杂,体积越大,功耗越低

三级流水线不是一级的三倍,跳转指令时,三级流水线会被打断,有译码后的指令浪费

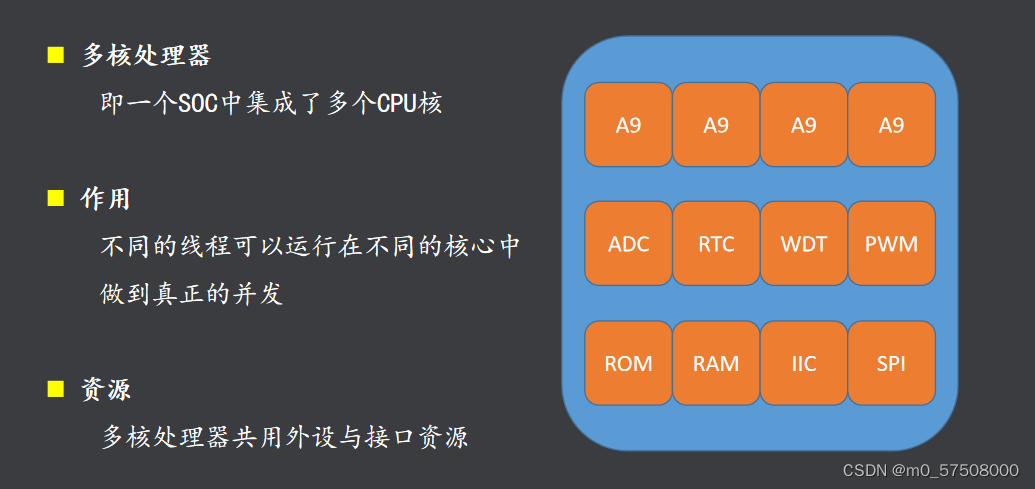

(三)多核处理器

多核CPU同时工作,多核一般是多核多线程,不同的线程放入不同核,真正实现并发,单核只能分时。

多核也是共享外设与接口资源。

五、注意事项

1、流水线级数越多,芯片越复杂,功耗越大

复杂指令集,指令越多,电路越复杂,体积越大,功耗越低

2、三级流水线不是一级的三倍,跳转指令时,三级流水线会被打断,有译码后的指令浪费

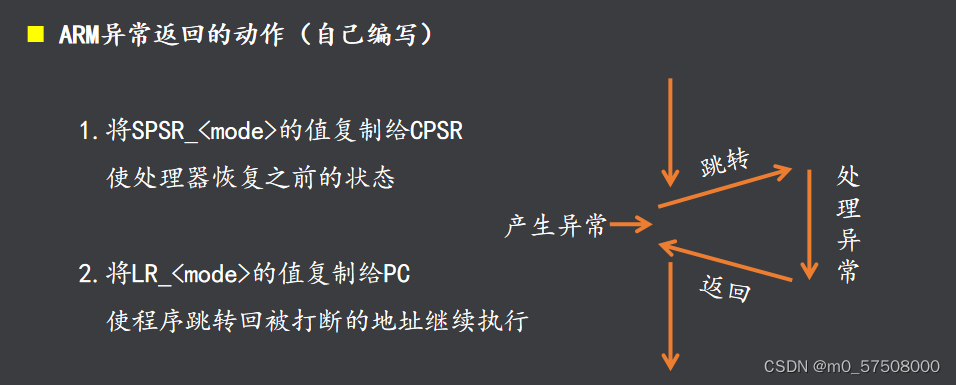

以IRQ为例,简述ARM处理器在正常执行程序过程中如果遇到IRQ异常会自动完成哪些动作以及处理完异常后如何返回到正常程序:

异常处理:

1、保存CPSR(处理异常前,备份当前状态)到对应异常模式的SPSR_irq。

2、修改CPSR(修改成异常模式)

1)修改中断禁止位禁止相应的中断(异常处理过程中阻塞其他中断)。

2)修改模式位进入相应的异常模式。

3)修改状态位进入ARM模式。

3、保存返回地址到对应异常模式下的LR_irq。

(LR在发生异常时自动保存正在执行的程序的下一条指令地址,不同异常模式对应不同的LR)

4、设置PC为相应的异常向量(异常向量表对应的地址)。

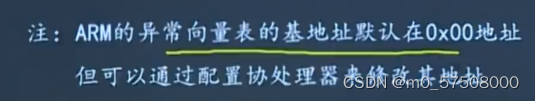

异常返回:

1、将SPSR_irq的值复制给CPSR使处理器恢复之前的状态

2、将LR_irq的值复制给PC使程序跳转回被打断的地址继续执行。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/145187.html