大家好,欢迎来到IT知识分享网。

AMD 的 Zen 4 架构在科技领域备受期待。

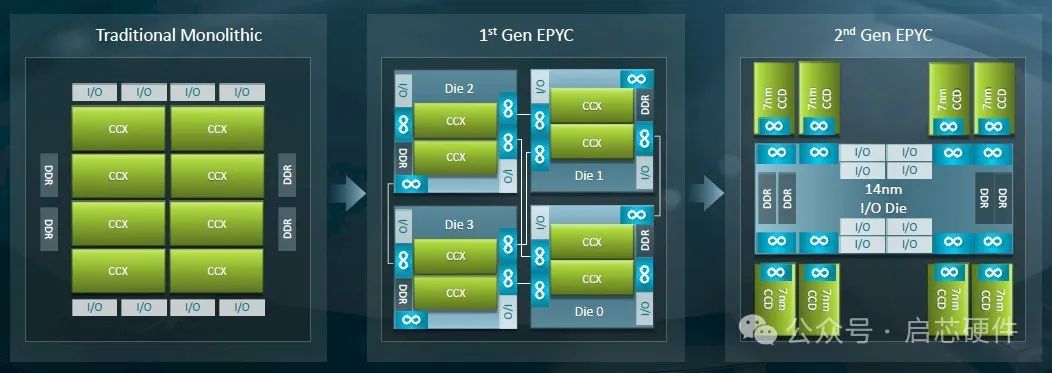

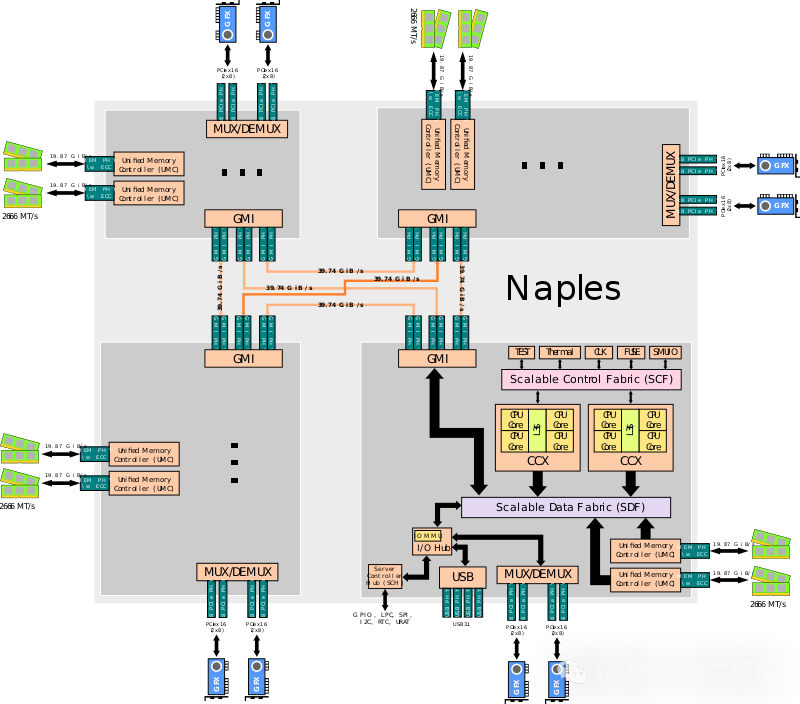

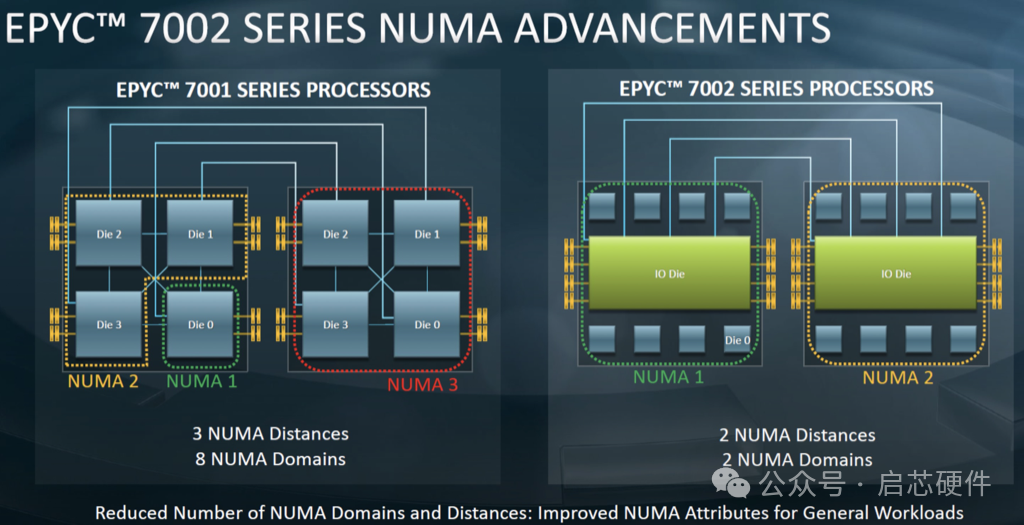

这个要从历代ZEN说起。Zen1 和 Intel 还比较像,只是一个CPU会封装多个小的Die来得到多核能力,导致NUMA node比较多。

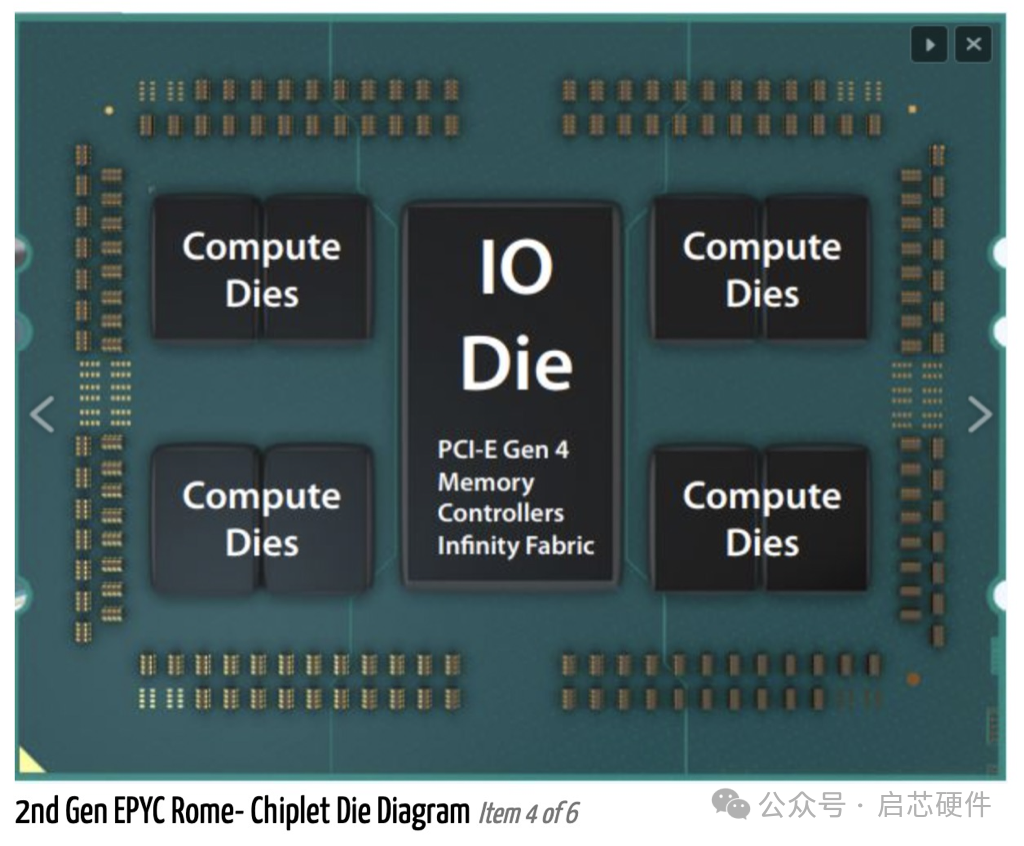

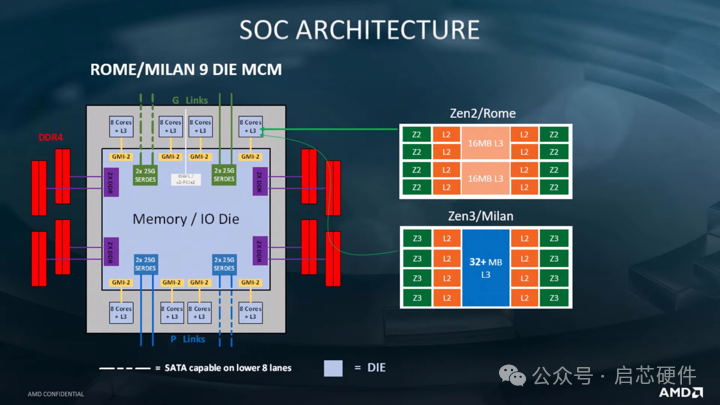

AMD 从Zen2开始架构有了比较大的变化,Zen2架构改动比较大,将IO从Core Die中抽离出来,形成一个专门的IO Die,这个IO Die可以用上一代的工艺实现来提升成品率降低成本。剩下的core Die 专注在core和cache的实现上,同时可以通过最新一代的工艺来提升性能。并且在一个CPU上封装一个 IO Die + 8个 core Die这样一块CPU做到像Intel一样就是一个大NUMA,但是成本低了很多,也许在云计算时代这么搞比较合适。当然会被大家笑话为胶水核(用胶水把多个Die拼在一起),性能肯定是不如一个大Die好,但是挡不住便宜。尤其是现在工艺节点的提升越来越小,所以封装技术显得越来越重要。

比如Core Die用7nm工艺,IO Die用14nm工艺,一块CPU封装8个Core Die+1个IO Die的话既能得到一个多核的CPU成本有非常低

AMD EPYC CPU演进路线

1-Zen1

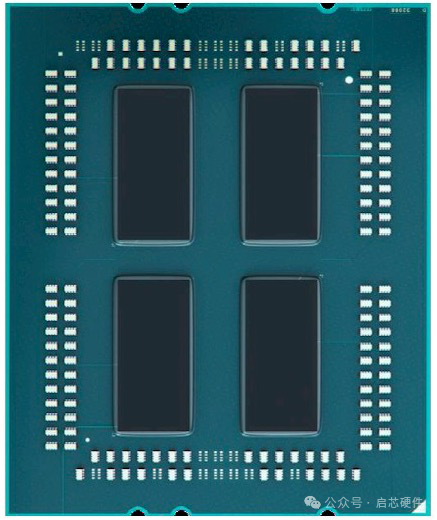

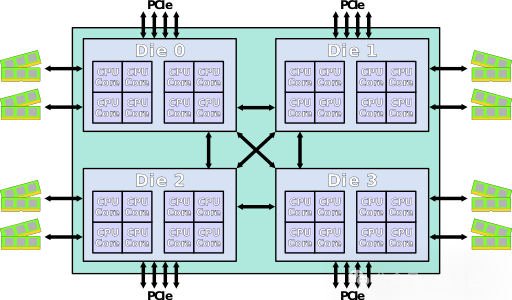

hygon 5280封装后类似下图(一块CPU封装了2个Die,还有封装4个Die的,core更多更贵而已)

或者4个Die封装在一起

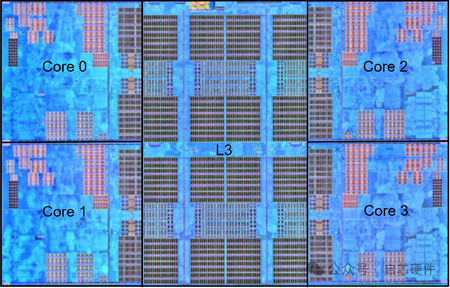

Zen1 Die

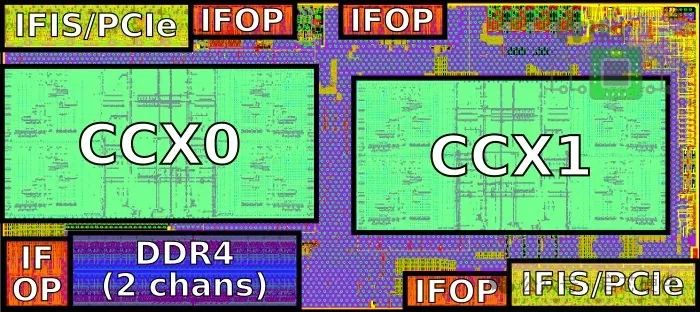

下面这块Die集成了两个CCX(每个CCX四个物理core), 同时还有IO接口

Quad-Zeppelin Configuration, as found in EPYC.

Zen CPU Complex(CCX)

hygon 5280使用这个结构, There are 4 cores per CCX and 2 CCXs per die for 8 cores.

44 mm² area

L3 8 MiB; 16 mm²

1,400,000,000 transistors

封装后的Zen1(4Die)

4个Die的内部关系

2-Zen2 Rome

Zen2开始最大的变化就是将IO从Core Die中抽离出来,形成一个专门的IO Die。封装后如下图:

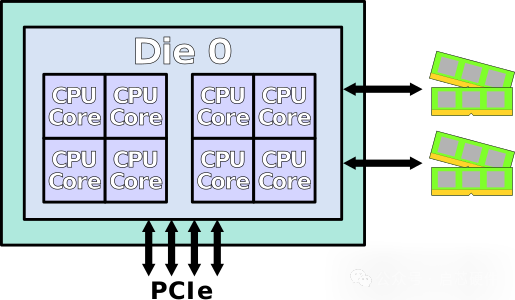

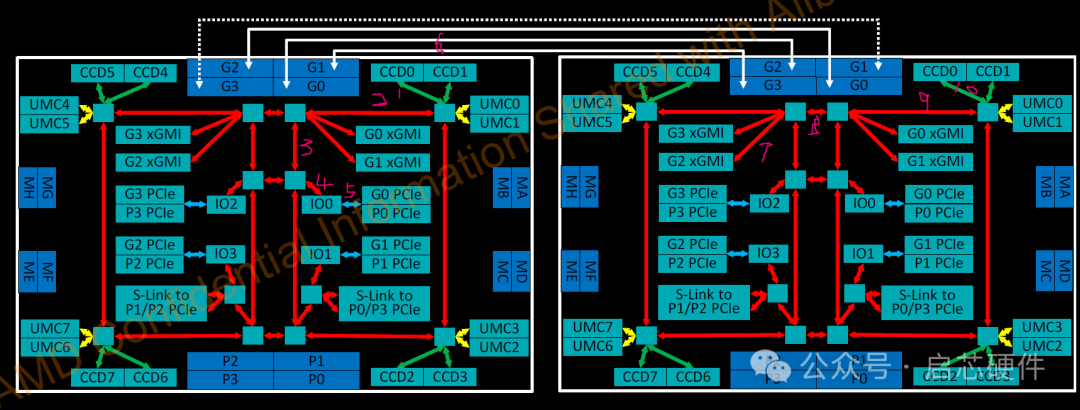

以上结构的CPU在2路服务器下的内部结构:

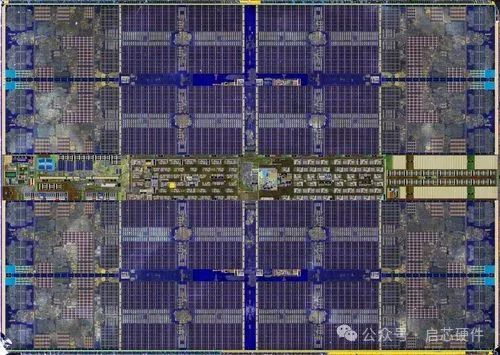

Zen2 Core Complex Die

TSMC 7-nanometer process

13 metal layers[1]

3,800,000,000 transistors[2]

Die size: 74 mm²

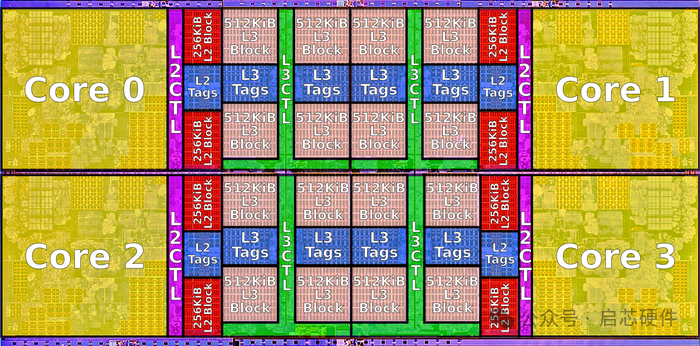

CCX size: 31.3 mm², 4core per CCX // 16M L3 perf CCX

2 × 16 MiB L3 cache: 2 × 16.8 mm² (estimated) // 中间蓝色部分是L3 16M,一个Die封装两个CCX的情况下

在Zen2/Rome架构中,一个CCD由两个CCX构成,一个CCX包含4个物理核,共享16MB的L3 cache。

在Zen3/Milan架构中,抛弃了两个CCX组成一个CCD的概念,一个CCD直接由8个物理核构成,共享整个Die上的32MB L3 cache。

Zen1 VS Zen2

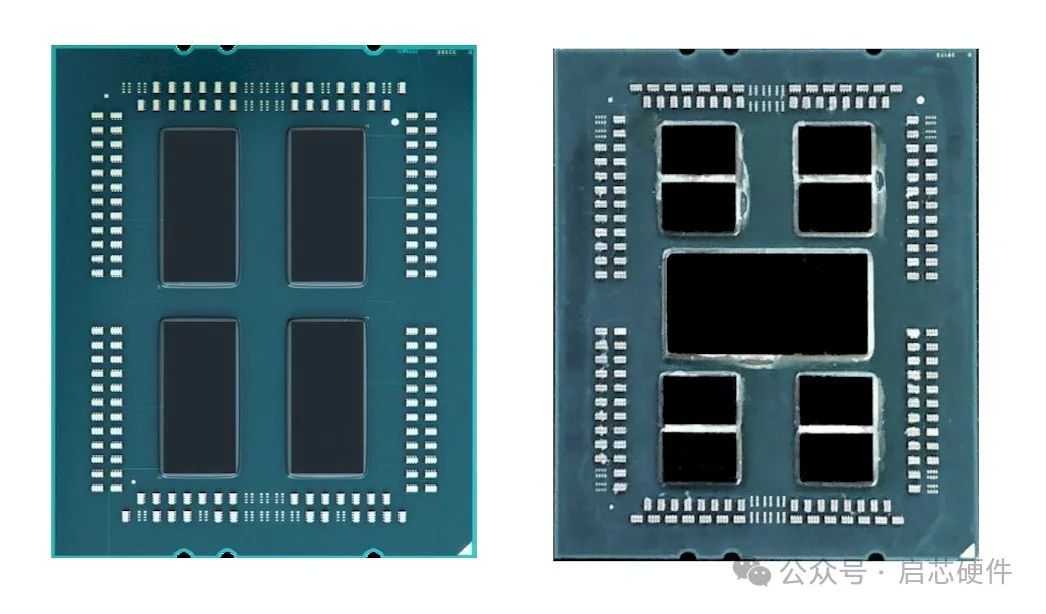

Here is what the Naples and Rome packages look like from the outside:

NUMA

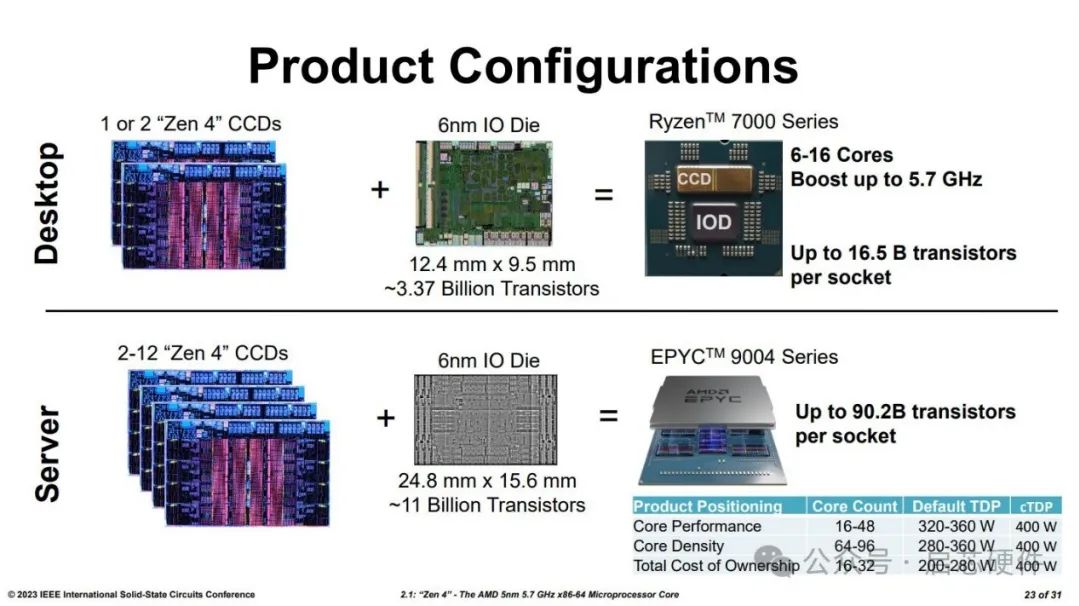

3-zen4

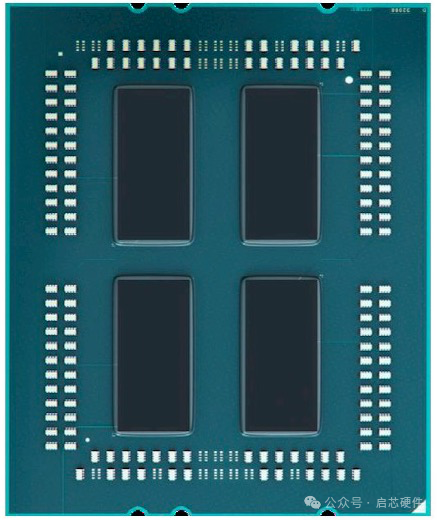

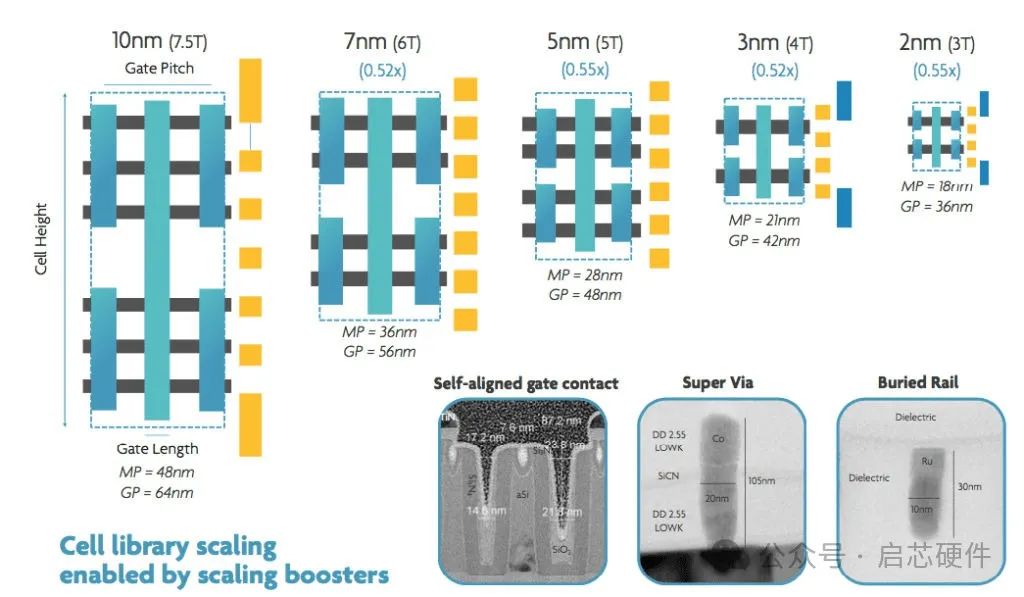

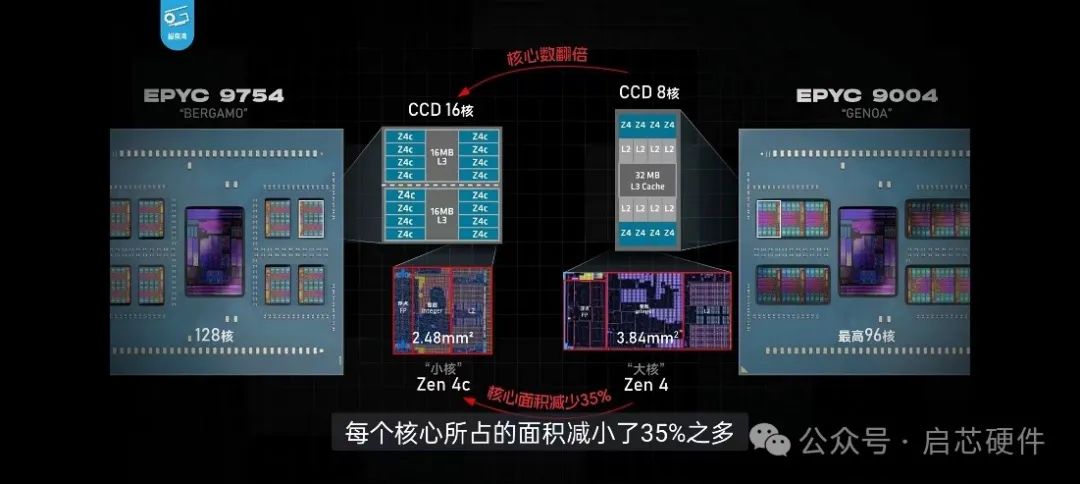

AMD Zen 4 芯片采用5nm工艺,面积约 80mm² ,相比 Zen 2 的 Die Size 提升了 10% 可容纳 12 个甚至 16 个 CPU 核心,因此 AMD 可以打造高达 128 核心的处理器。

根据 AMD 的规划,旗下最新第四代 EPYC 服务器处理器「Genoa」采用 TSMC 5nm 制程、Zen 4 架构,而消息指 TSMC 5nm 制程将会比现有的 7nm 提升 80%,整体性能会提升 15%。

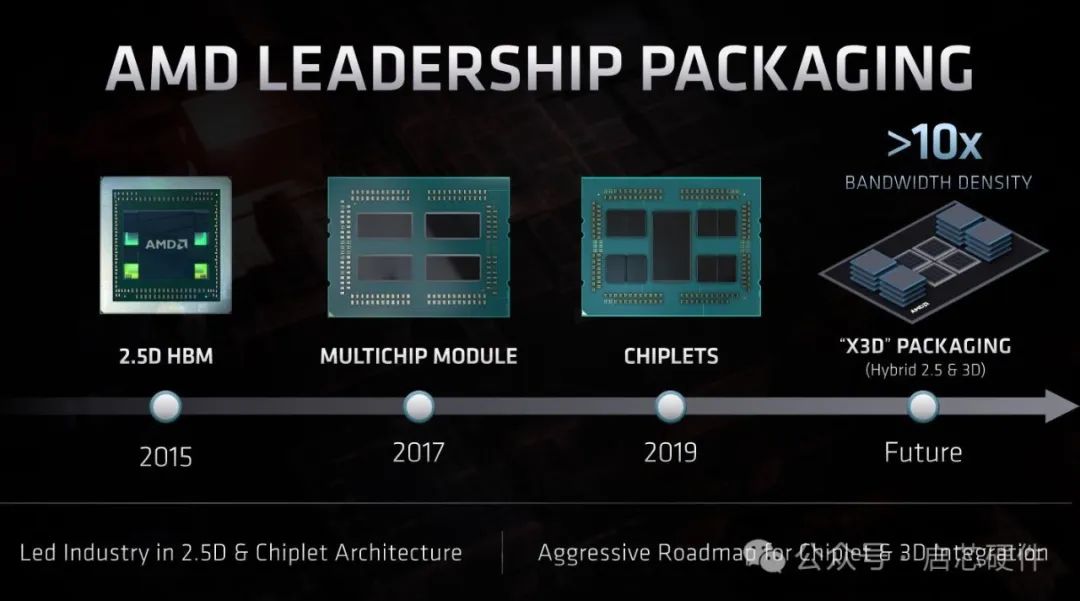

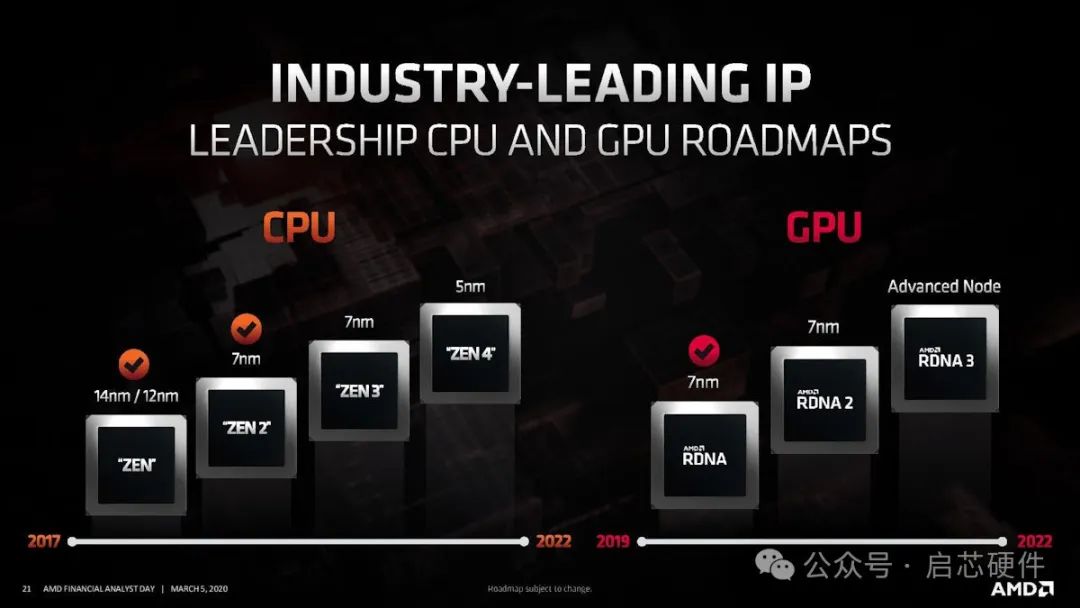

AMD CPU和GPU的工艺技术迭代图

最重要的 CPU 核心前端和分支预测单元,与上一代“Zen 3”相比,IPC 提高了 13%

“Zen 4”CCD的晶体管数量为65.7亿个,比“Zen 3”CCD的41.5亿个晶体管数量增加了58%。

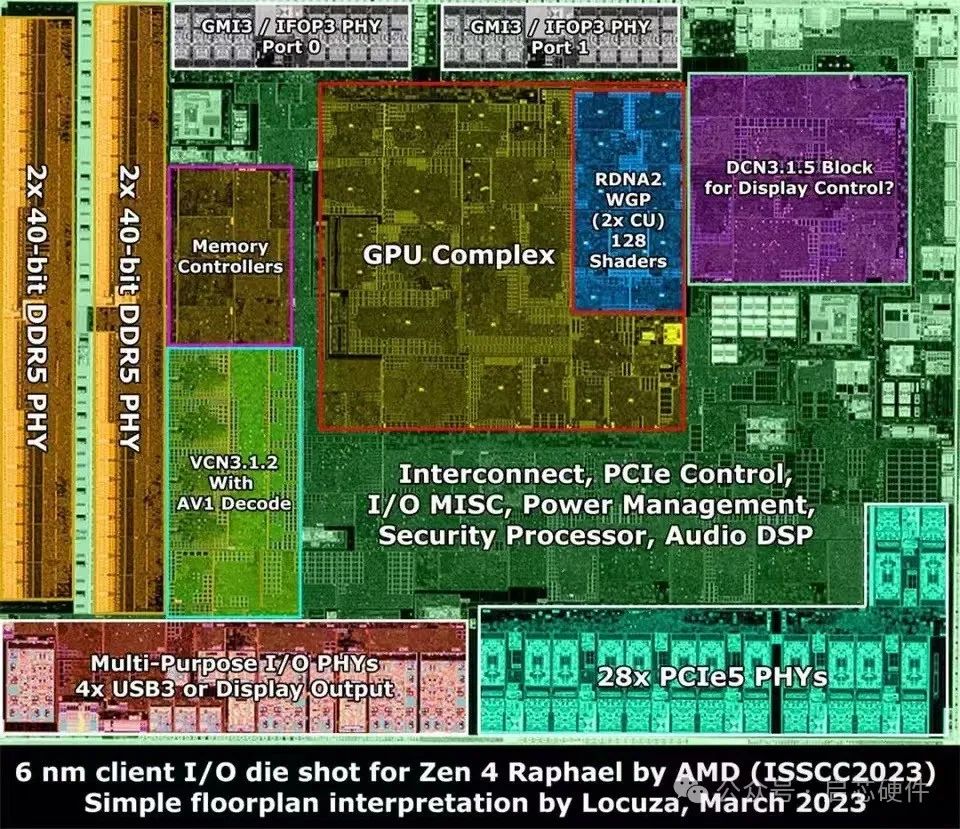

cIOD(客户端 I/O 芯片)见证了大量创新。它基于 6 纳米(台积电 N6)节点构建,与 Ryzen 5000 系列处理器的 cIOD 所基于的 GlobalFoundries 12 纳米节点相比,这是一个巨大的飞跃。它还集成了 Ryzen 6000“Rembrandt”处理器的某些电源管理功能。除了 DDR5 内存控制器和 PCI-Express Gen 5 根复合体之外,该 cIOD 还包含基于 RDNA2 图形架构的 iGPU。新的 6 nm cIOD 尺寸为 124.7 mm²,而 Ryzen 5000 系列的 cIOD 稍大,为 124.9 mm²。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/145191.html