大家好,欢迎来到IT知识分享网。

1 总线简介

总线:是指计算机组件间规范化的交换数据的方式,以一种通用的方式为各个组件提供数据传送和控制逻辑。

chatgpt 给的结果是 :总线(Bus)是计算机系统中用于传输数据、地址和控制信号的一种集合线路。它在计算机内部的各个组件之间传递信息,如中央处理器(CPU)、内存、输入输出设备等。总线可以分为不同的类型,包括数据总线、地址总线和控制总线。

- 数据总线(Data Bus):用于传输数据和指令,使各个组件能够交换信息。数据总线的宽度决定了系统能够一次传输的位数,例如,一个32位数据总线可以一次传输32位(4字节)的数据。

- 地址总线(Address Bus):用于传输内存或设备的地址信息,使CPU能够访问特定的内存位置或设备。地址总线的宽度决定了系统能够寻址的内存范围,例如,一个16位地址总线可以寻址2^16个不同的内存位置。

- 控制总线(Control Bus):用于传输各种控制信号,例如时钟信号、读写信号、中断信号等,以控制各个组件的操作。

总线的设计和性能对计算机系统的整体性能至关重要。更快速、更宽的总线可以提高数据传输速度,从而加快计算机的工作效率。然而,总线速度的提升也会受到物理限制和成本因素的制约。因此,在计算机系统的设计中,总线的选择和优化是一个重要的考虑因素

对于总线而言,有以下比较重要的性能指标或者是概念需要掌握:

带宽:指的是单位时间内总线上传送的数据量;其大小为总线位宽*工作频率(单位为bit,但通常用Byte表示,此时需要除以8)。

位宽:指的是总线有多少比特,即通常所说的32位,64位总线。

时钟频率:以MHz或者GHz为单位。

延迟:一笔传输从发起到结束的时间。在突发传输中,通常指的是第一笔的发起和结束时间之间的延迟(什么事是突发传输后面再讲)。

传输方式:总线传输数据的方式主要有同步传输和异步传输两种模式。同步传输通过时钟信号来控制数据的传输,而异步传输则是直接在总线上进行数据交换。

2 AMBA总线

AMBA总线的发展历程

3 APB总线

APB的全程是Advanced Peripheral Bus ,高级外设总线,但是其链接的外设往往是低速度且低功耗的外设,如I2C,UART,SPI ,除了链接低速设备外,APB总线还广泛应用与配置各种IP的寄存器(这些IP预留给用户控制信号,有软件进行配置,这个时候就可以选择APB总线来配置这些寄存器),此外为了是APB能够容易的被整合进大部分的设计中,APB规定所有的信号必须是时钟的上升沿传递。

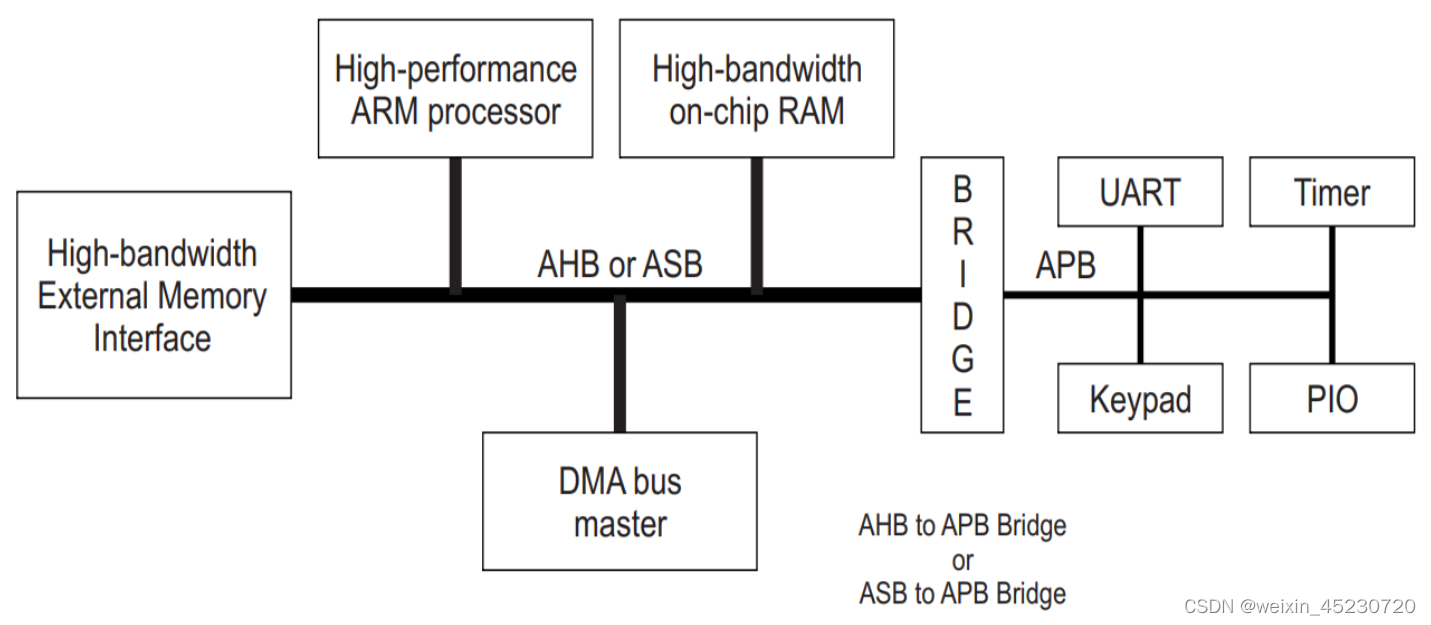

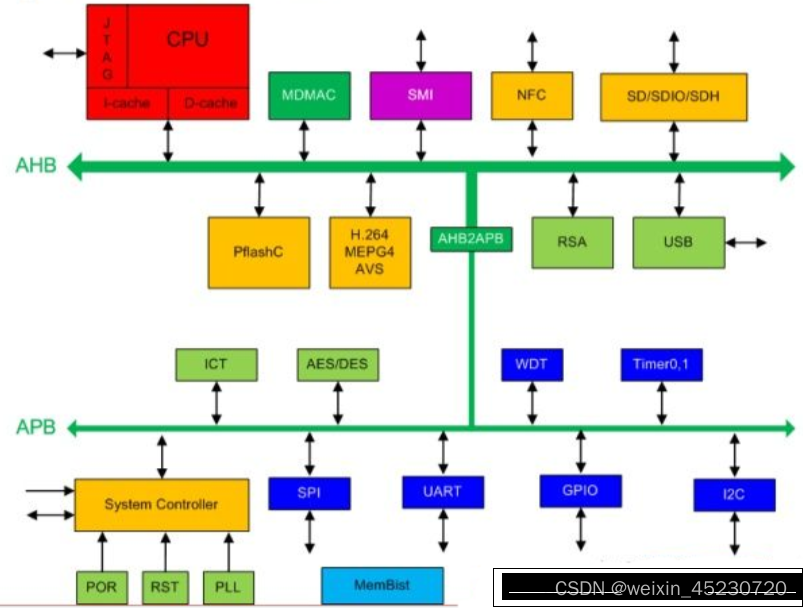

一个soc框架

简述一下APB 的发展历程

APB2 :

APB总线的基础版本

APB3:

增加PREDAY信号:用于反压master

增加PSLVERR:用于表示传输是否发生错误

APB4:

增加PPROT保护信号

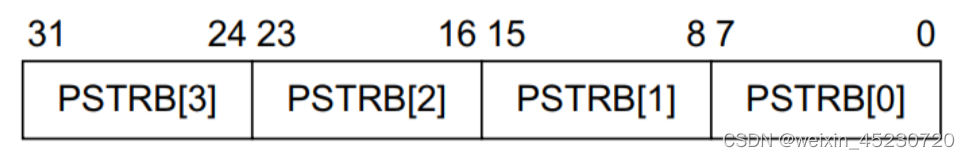

增加PSTRB代表字节选通

APB5:

增加PWAKEUP信号,从机唤醒功能

增加PAUSER信号,用户请求分配

增加PWUSER信号,用户写数据分配

增加PRUSER信号,用户读数据分配

增加PBUSER信号,用户数据分配

3.1APB信号列表

用于从slave向master返回传输错误,这个错误是slave自己定义的,比如写了不允许写的地址,即非法地址访问。或者是访问超时了,slave回应不了了。就可以拉高这个信号,从而避免总线锁死。

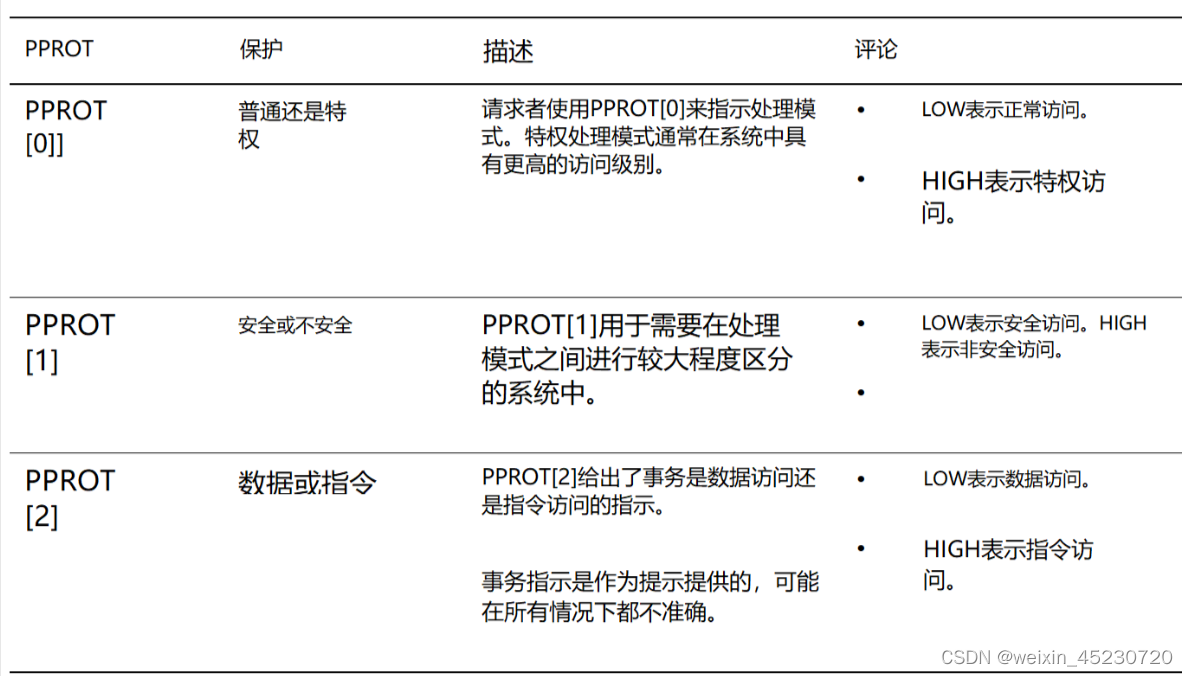

- PPROT

PPROT(Peripheral Protection)信号用于实现外设的访问保护,保护外设不受未授权的访问和恶意攻击。

对于CPU而言,可以工作在用户模式下也可以工作在特权模式下(比如RISC-V的USM三种模式)。对于支持trustzone的CPU,可以工作在secure world下,也可以工作在normal mode下。又由于现在的系统越来越复杂了,以前的外设是随意读写都可以,现在的一些外设或memory(比如一些CSR寄存器,Trusted RAM等)要求只能在secure下或者privileged模式下访问,因此就需要PPROT信号。

3.2APB传输

3.2.1APB状态机

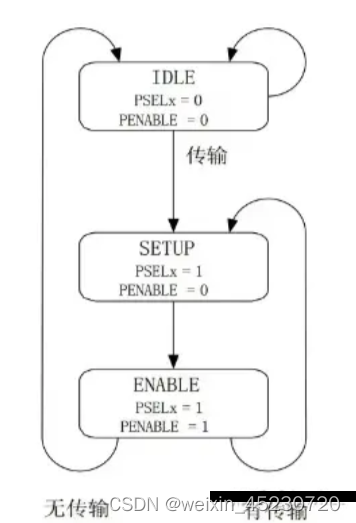

APB2.0的状态机

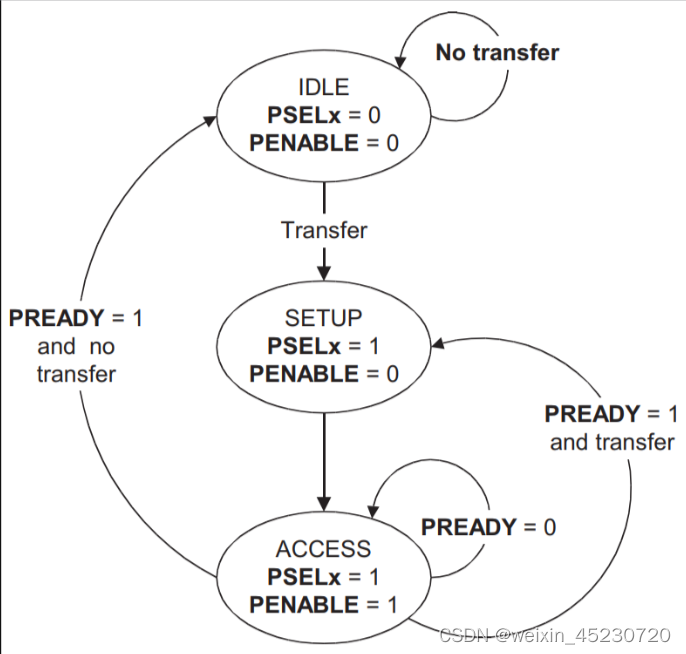

APB3/4/5的状态机

状态机有以下几种状态:

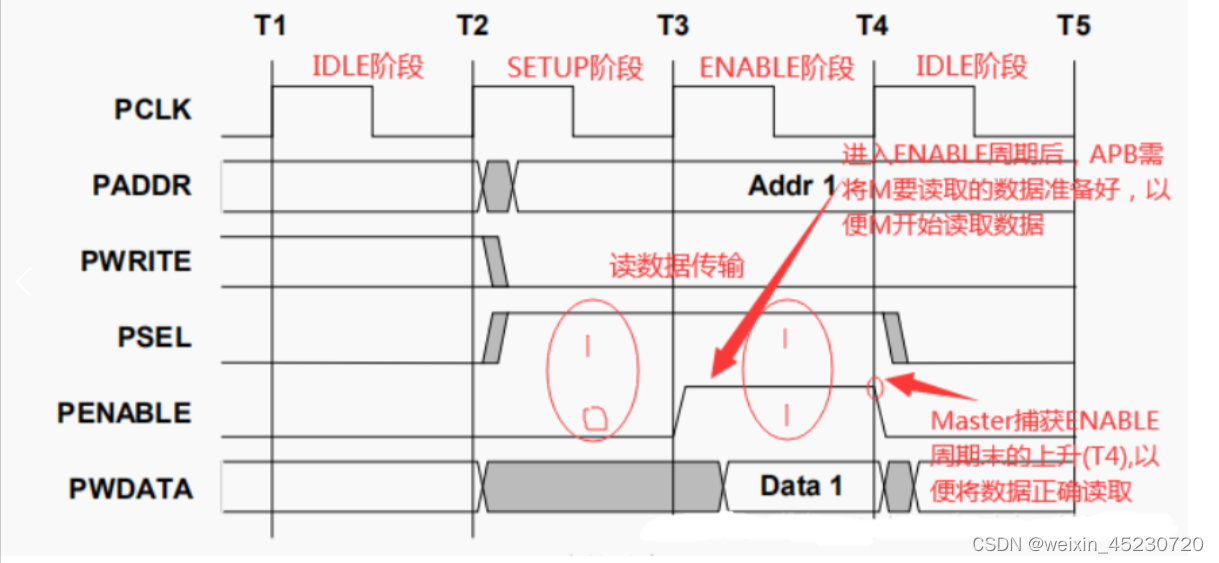

APB2读写操作

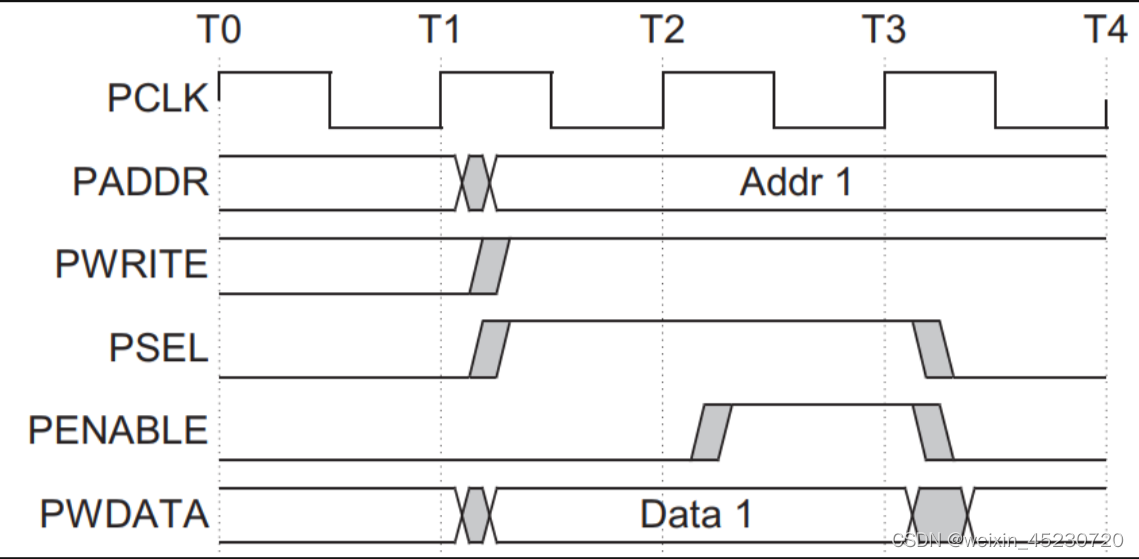

写操作

可以看到写操作非常的简单:

至此一次传输结束。可以看到,APB对每一笔数据的传输,需要花费两个时钟周期。且APB的数据传输不支持流水线操作(即不可以重叠)。因此APB是非常低效的

理论上写数据完全可以同时给出写地址和写数据,一拍就搞定,为什么APB要大费周章弄成两拍呢?这主要是那个年代的芯片本身的制程工艺以及片上互连线导致的。一个周期可能无法完成从Master向Slave写入数据的整个操作流程。因此采用两拍的方式,第一拍告诉你,我要开始传输啦!(称为setup phase)第二拍才真正的完成数据的传输。(称为access phase)。

如果Master想要马上发起一次新的传输,可以不拉低PSEL让其继续为1,但是必须要将PENABLE拉低。否则Slave侧的判断逻辑就会出现问题!

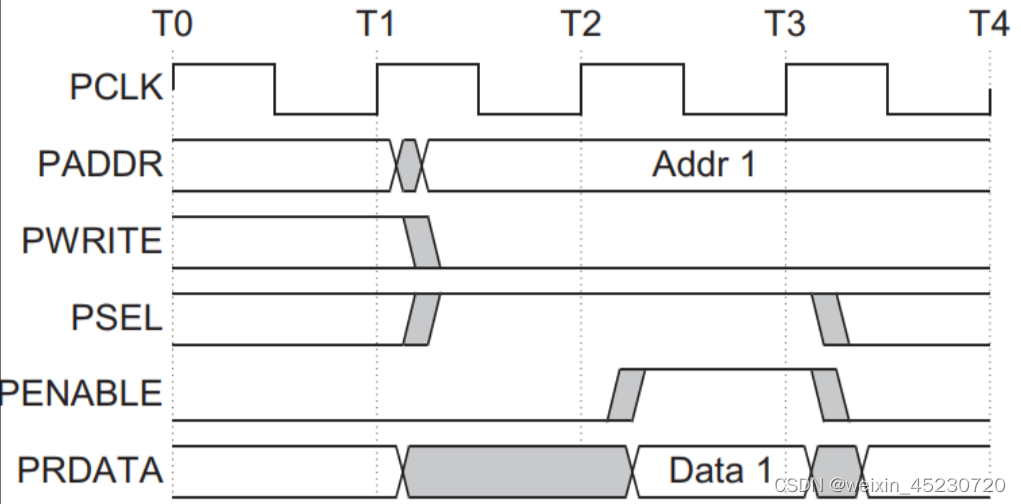

可以看到读操作非常的简单,跟写几乎一样。这里就不再做详细的解释了。

要特别注意的是,T2以后,也就是进入ENABLE周期后,APB的SLAVE设备必须要将M所需要读取的数据准备好,以便M可以在ENABLE的周期末也就是T3正时钟沿触发时正确的将数据读取。

APB2的一些理解问题

貌似上面的状态机模型以及读写时序图,有没有PENABLE信号实际上都能完成APB传输,那么APB slave 是否真的需要要penable信号?

分两种情况讨论一下

1如果APB slave 有pclk时钟信号,那么确实是不需要PENABLE信号,检测到PSEL高,即进入access阶段,然后在第二个时钟周期完成数据传输即可。代码参考全网。

`timescale 1ns/1ps `define DATAWIDTH 32 `define ADDRWIDTH 8 `define IDLE 2'b00 `define W_ENABLE 2'b01 `define R_ENABLE 2'b10 module APB_Slave ( input PCLK, input PRESETn, input [`ADDRWIDTH-1:0] PADDR, input PWRITE, input PSEL, input [`DATAWIDTH-1:0] PWDATA, output reg [`DATAWIDTH-1:0] PRDATA, ); reg [`DATAWIDTH-1:0] RAM [0:2`ADDRWIDTH -1]; reg [1:0] State; always @(negedge PRESETn or posedge PCLK) begin if (PRESETn == 0) begin State <= `IDLE; PRDATA <= 0; end else begin case (State) `IDLE : begin PRDATA <= 0; if (PSEL) begin if (PWRITE) begin State <= `W_ENABLE; end else begin State <= `R_ENABLE; end end end `W_ENABLE : begin if (PSEL && PWRITE) begin RAM[PADDR] <= PWDATA; end State <= `IDLE; end `R_ENABLE : begin if (PSEL && !PWRITE) begin PRDATA <= RAM[PADDR]; end State <= `IDLE; end default: begin State <= `IDLE; end endcase end end endmodule2如果APB slave是纯粹的组合逻辑,这个时候就需要penable信号

当PSEL & !PENABLE 为1 的时候,代表是setup stage ,实际上slave 什么也不用做

当PSEL& !PENABLE 为0 的时候,代表是数据传输阶段,slave完成数据的传输

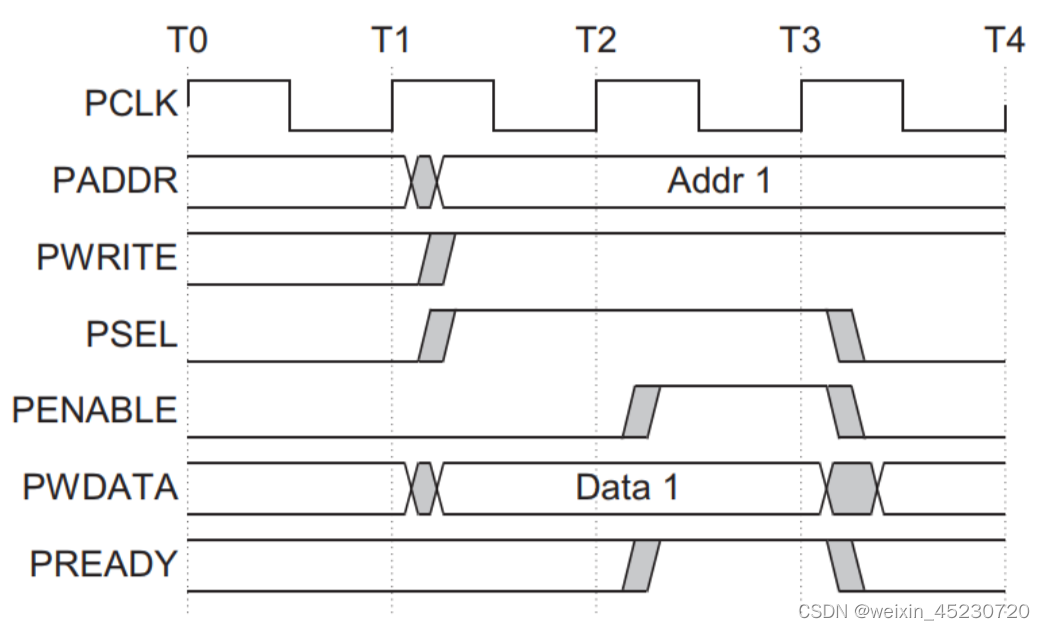

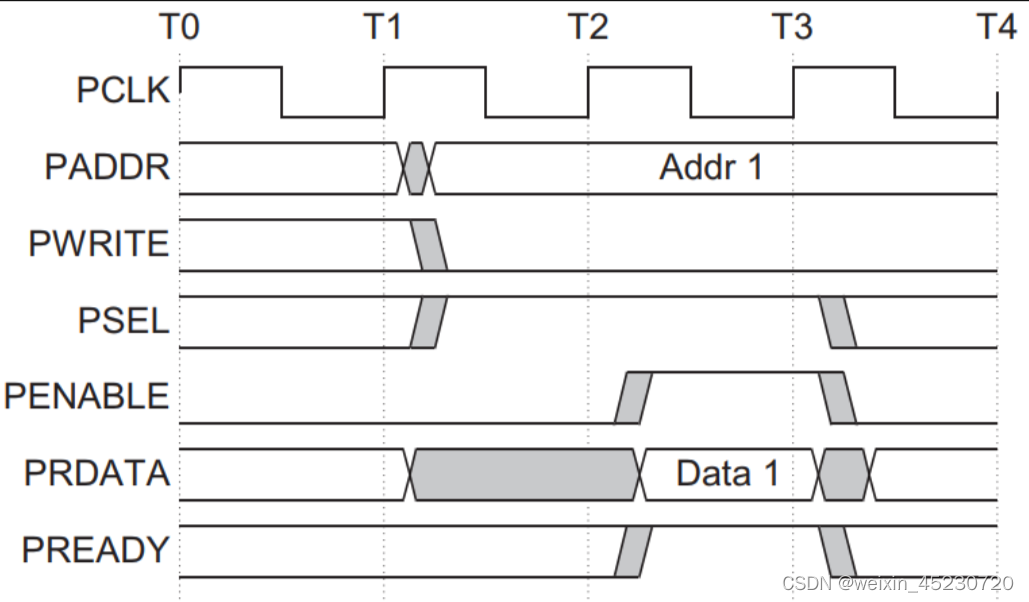

APB3读写操作

写操作

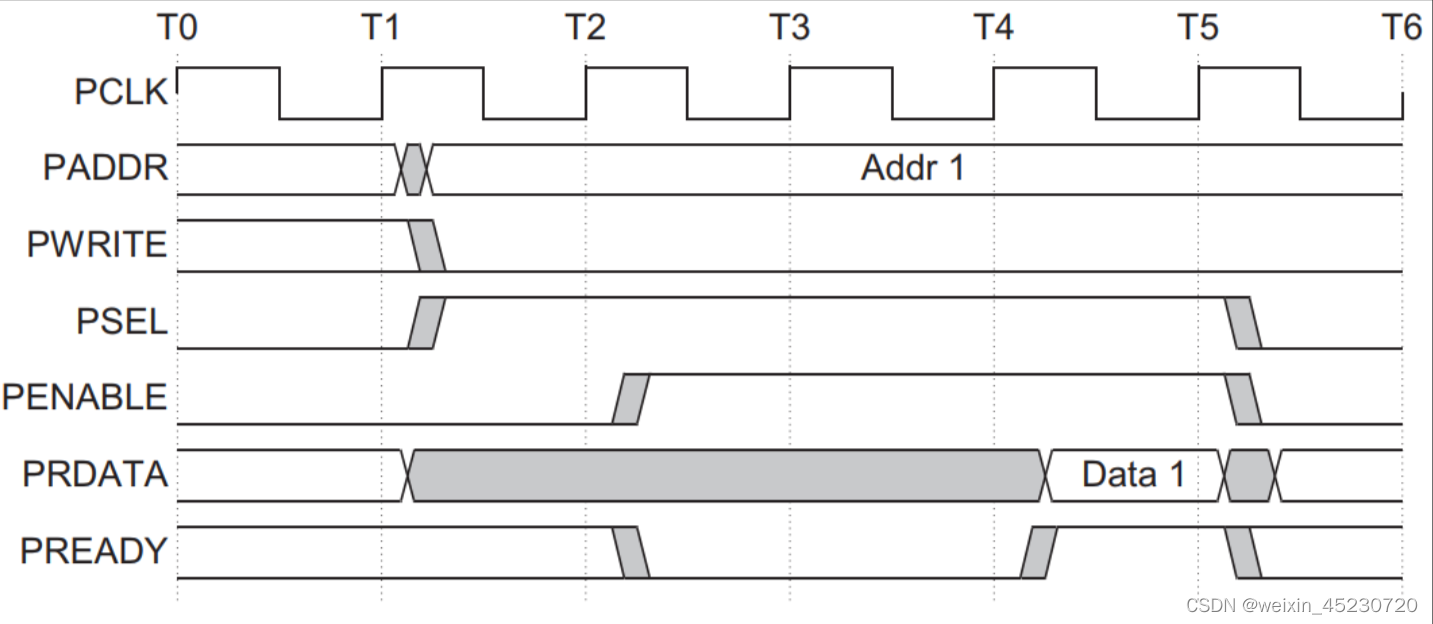

读操作

上图是没有wait states的情况。两拍完成写操作。和APB2的区别在于多了个PREADY,需要在传输的第二拍也就是真正发生数据传输的那一拍拉高。其它的和上面的写时序是一模一样的,因此不再说明。

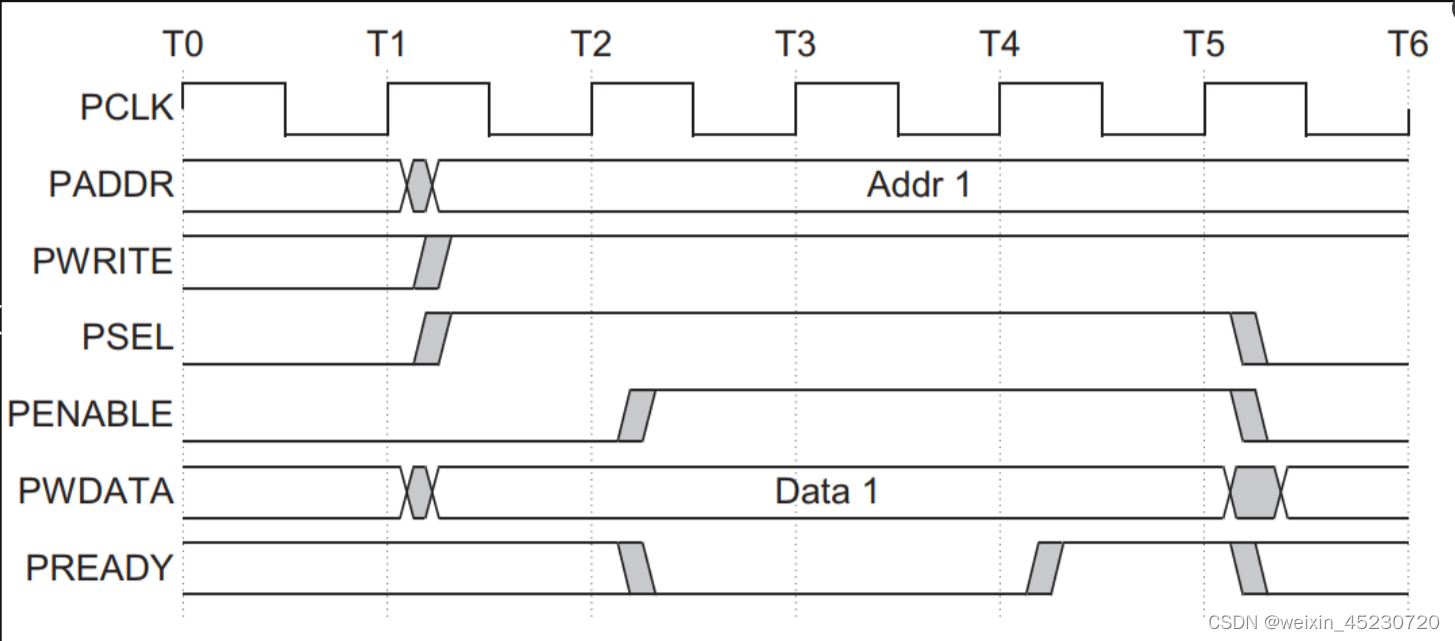

写操作(等待)

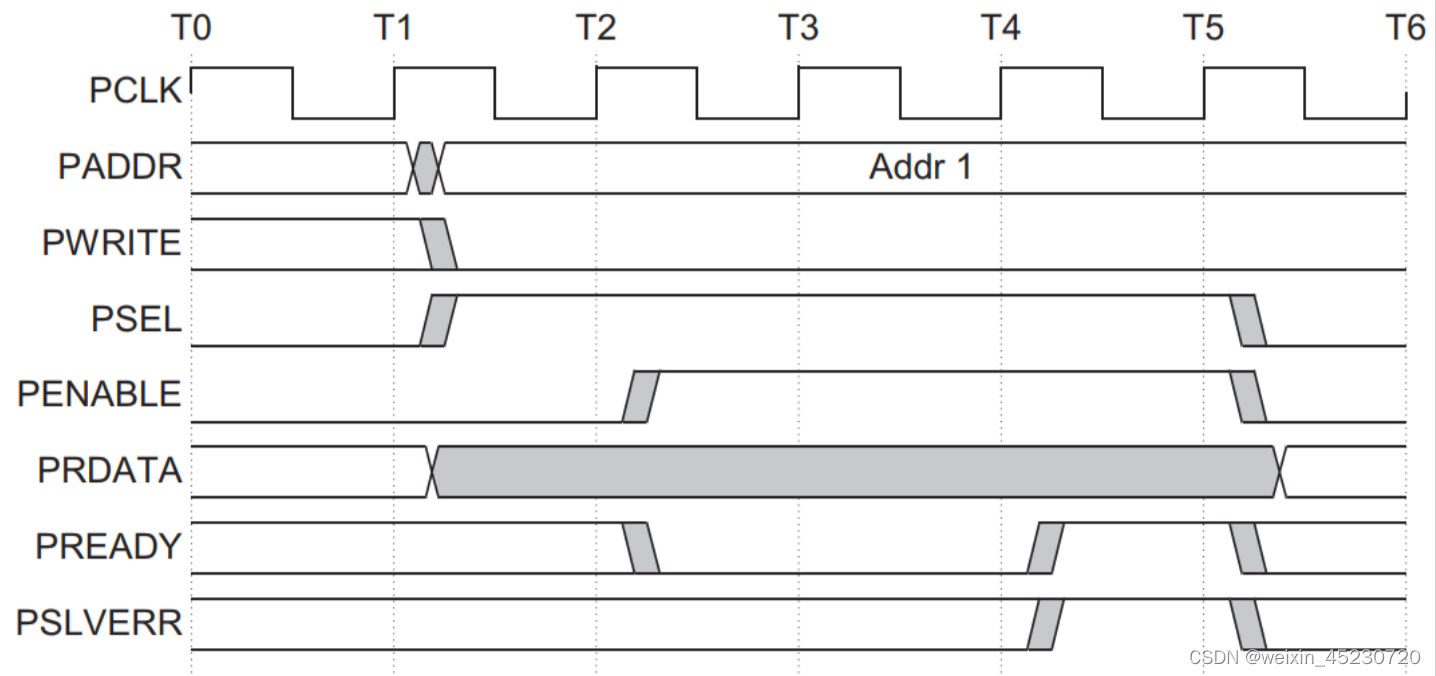

读操作(等待)

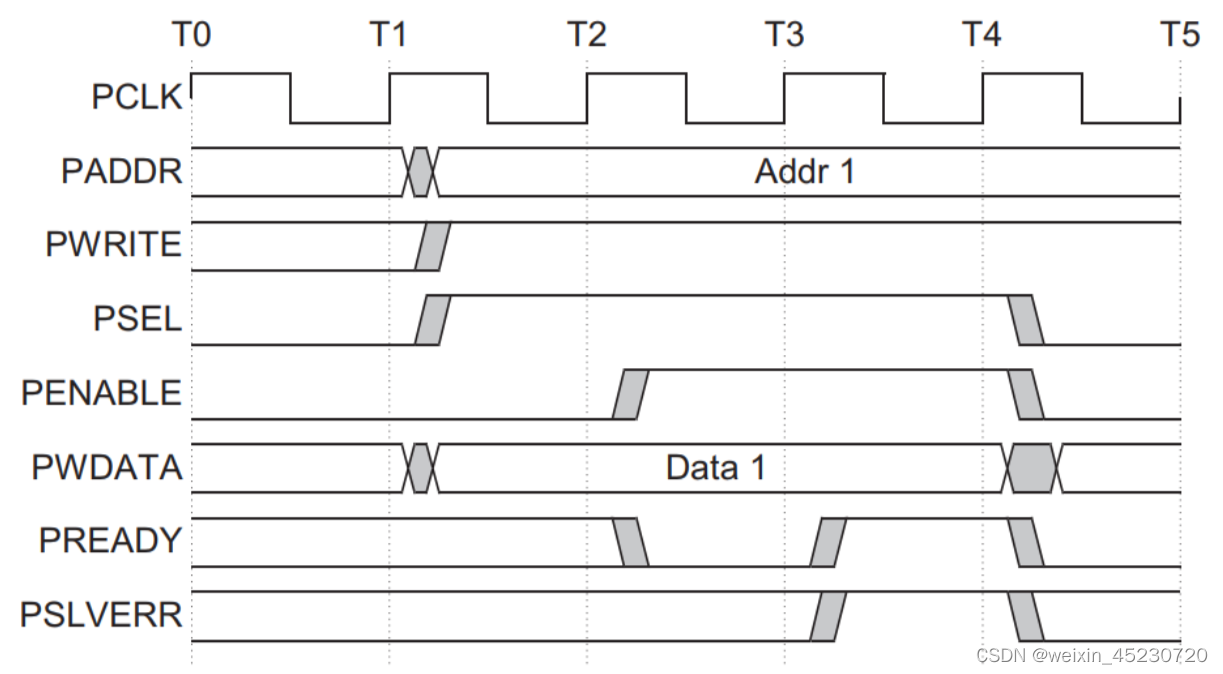

读操作(错误)

读写操作进行中PSLVERR信号拉高,表明此次写/读操作有误,所写入/读取的数据未正确写入/读取。

3.3 APB4和APB3以及APB3和APB2的兼容性问题

以APB4的slave和APB3的master为例,这个时候应该把PSTRB信号固定为全1,PPROT信号则取决于Slave是如何使用该信号的,根据不同的场景固定为不同的值。

而APB3的slave和APB4的master相连接,这个时候实际上需要一个转接桥,因为本身可能只想写某一个字节,而slave此时不支持也不知道,那就需要一个中间逻辑将pwdata变成想要的值。(比如读回来时32’h2345,想将最高字节改写为6,此时只写一个32’h6000,PSTRB为1000,标志别的字节不要动。这个时候就需要一个中间逻辑将写的数据变成32’h6345)。实际上写起来也很麻烦,因此此时最好将APB3的slave改成APB4协议。

至于APB3和APB2不建议一起用,因为APB2没有PREADY反压机制,因此实际使用起来完全不一样,强行一起用会有巨大的坑

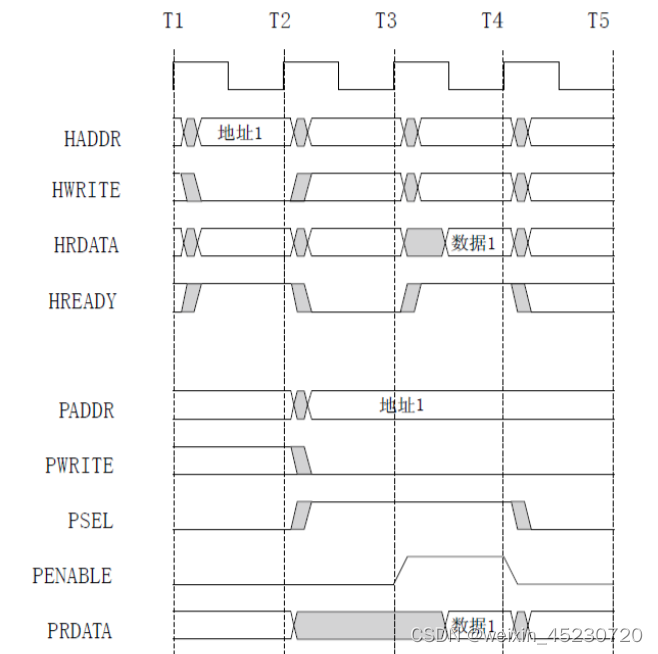

4APB到AHB接口

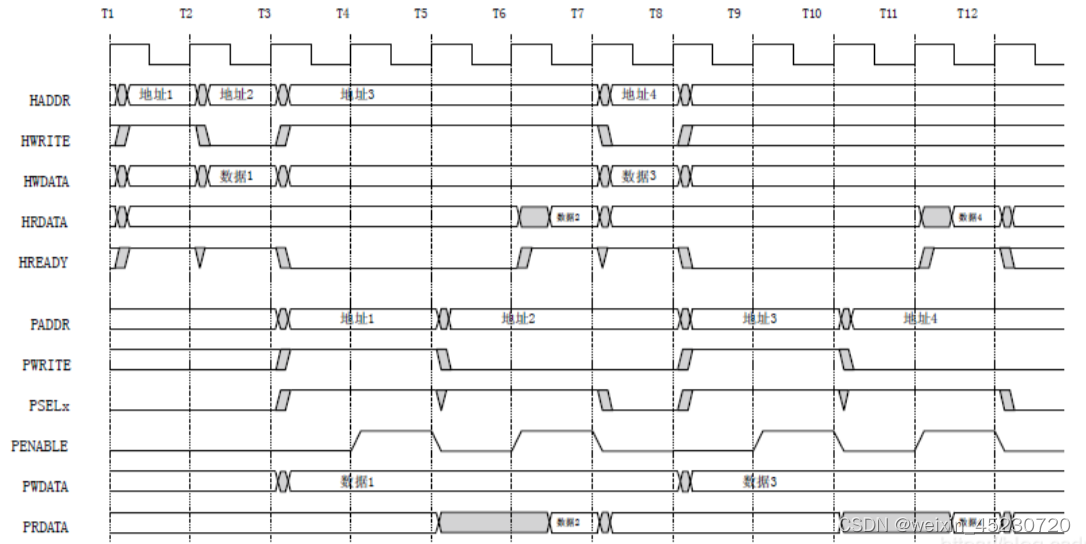

4.1读操作

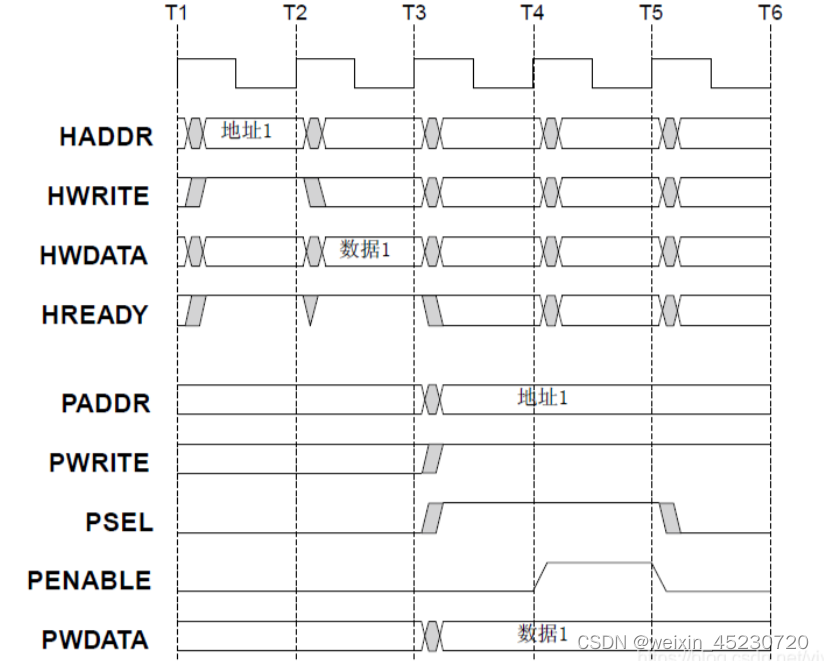

4.2写操作

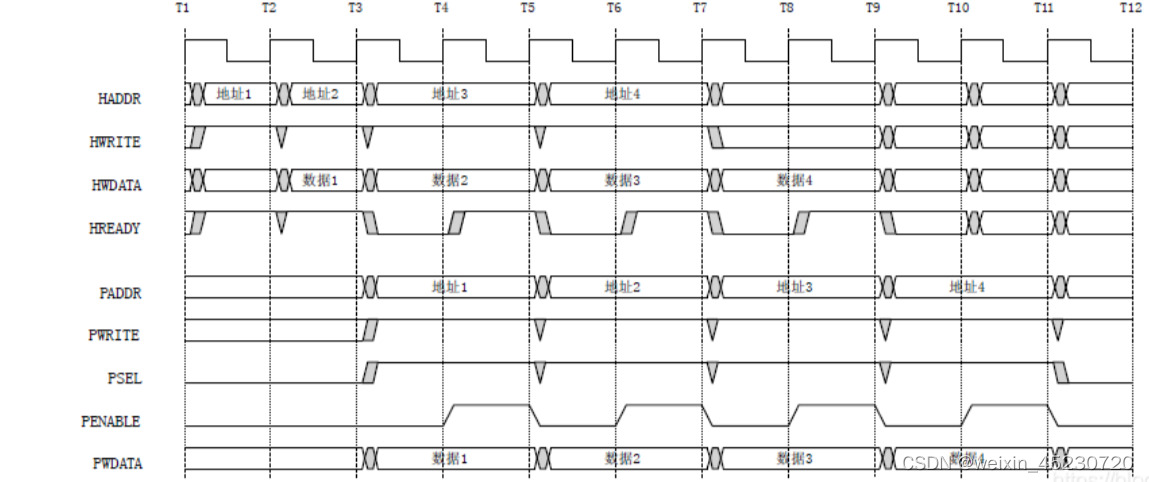

4.3 背靠背操作

下图给出了背靠背传输的时序,分别写,读,写,读

如果写操作之后跟随着读操作,那么需要 3 个等待周期来完成读操作。通常的情况下,不会有读操作之后紧跟着写操作的发生,因为两者之间 CPU 会进行指令读取。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/109727.html