大家好,欢迎来到IT知识分享网。

三炮儿每周二早七点

分享/更新一篇硬件开发学习笔记

学习分享以助能力增长♥经验交流以期跻身一流

目录

一、自举电容的作用

二、自举电容的工作原理/过程

三、自举电容选型

✍

本周的笔记是关于BUCK电路中自举电容的工作原理与作用、选型应用方面相关的。

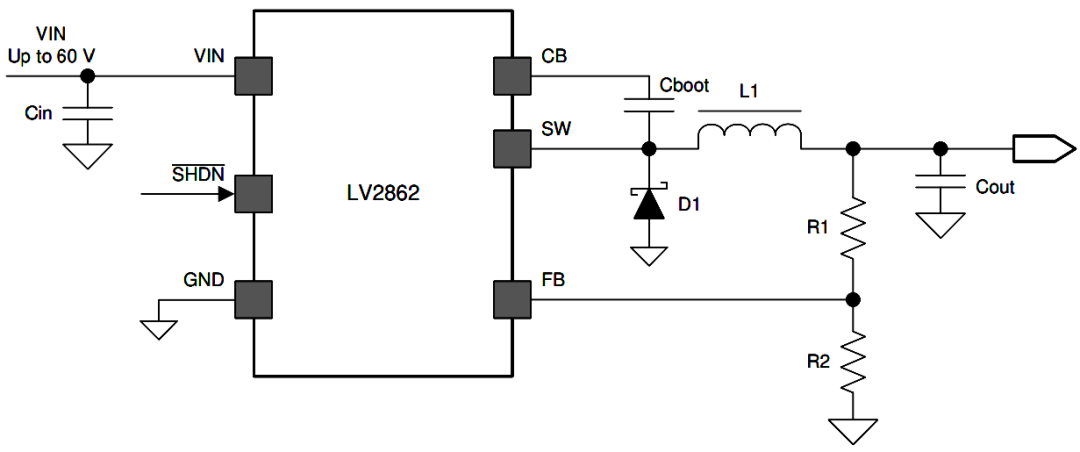

在BUCK电路设计中,一般在CB(BST)和SW管脚之间会放置一颗0.1uF的陶瓷电容Cboot,这颗电容被叫做自举电容;

有的设计中BST和SW之间串接的是一颗电阻和一颗电容,他们分别被叫做自举电阻、自举电容。

LV2862 Simplified Schematic

一、自举电容的作用

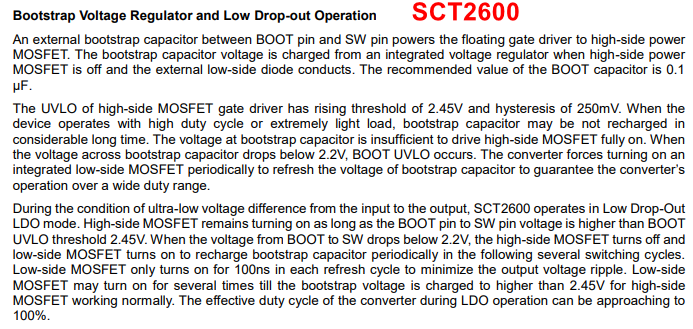

CT2600 Step-down DCDC Converter S规格书中有如下说明:

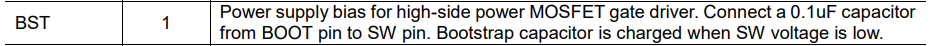

BST Pin用于高侧功率MOSFET栅极驱动器的电源偏置;

将0.1uF电容从BOOT引脚连接到SW引脚;SW电压低时,自举电容器充电。

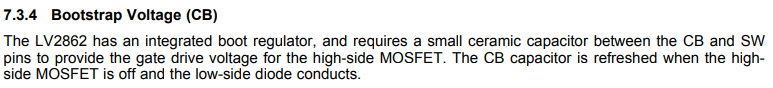

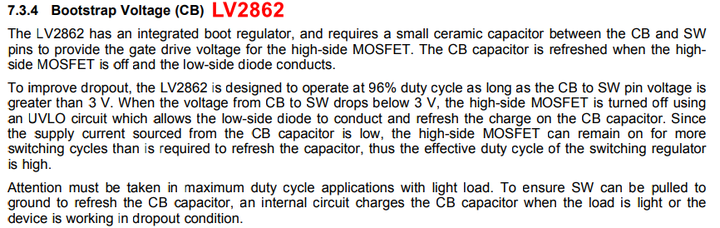

LV2862规格书中有如下说明:

开关FET栅极偏置电压。Cboot电容连接在CB和SW之间。

LV2862内部有启动调节器,

需要CB和SW引脚之间的小陶瓷电容器为高侧MOSFET提供栅极驱动电压。

当高侧MOSFET关断并且低侧二极管导通时,Cboot电容被刷新。

自举电容的作用总结

自举电容连接在CB和SW引脚之间; 用于驱动高侧MOS管的栅极;在高侧MOS管关断并且低侧二极管导通时,自举电容被刷新(充电)。

为充分理解自举电容的作用原理,需要深入到Buck芯片内部去探究。

二、自举电容的工作原理/过程

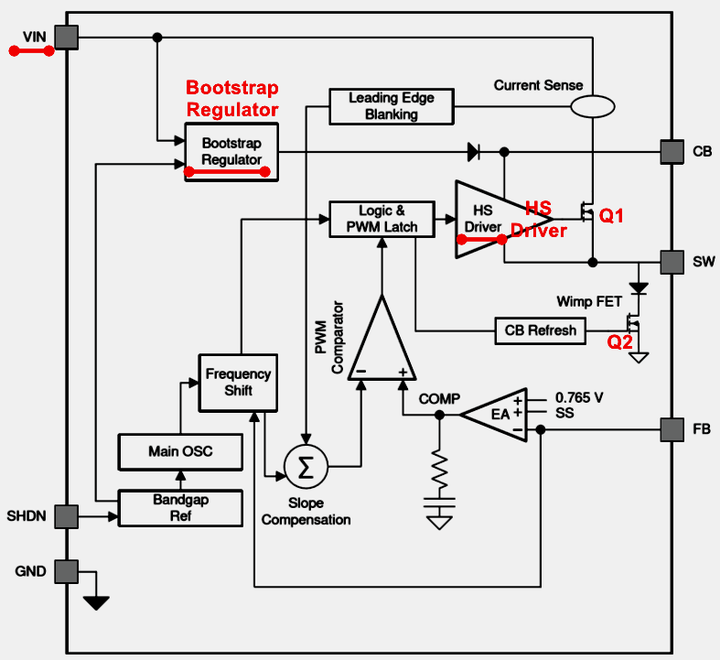

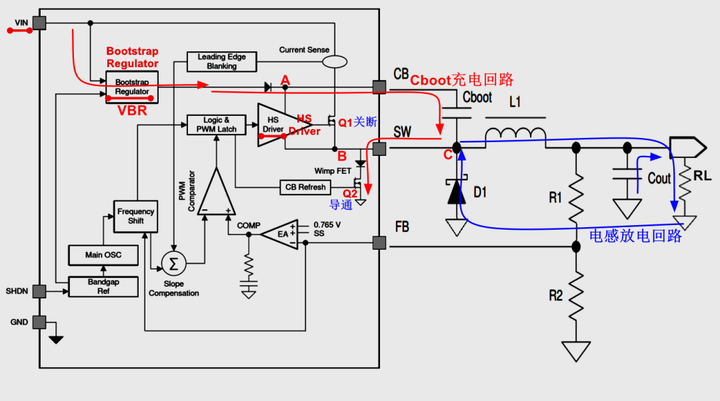

LV2862的功能拓扑框图如下,其中

Q1:Buck电路的高侧NMOS开关管;

HS Driver:高侧MOSFET Q1的栅极驱动电路;

Q2:NMOS管,用于刷新Cboot电容,提供充电回路。

1、Cboot电容充电

当高侧MOS管Q1关断并且低侧二极管导通时,Cboot电容开始充电;

Cboot电容充电回路,以及此时Buck中电感的放电回路如下图

当MOS管Q1关断,Q2导通时,由储能电感L1放电为负载提供能量,如上图蓝色回路;

同时,自举电容Cboot开始充电,充电回路如上图红色回路,忽略Q2、二极管的导通压降,Cboot完成充电后的电压可认为是自举调整器(Bootstrap Regulator)的输出电压VBR。

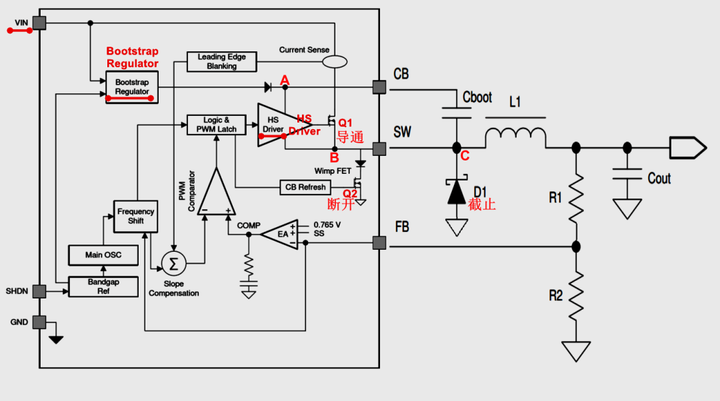

2、驱动高侧MOS管Q1导通

储能电感L1放电到一定程度时,二极管D1反向截止,

此时需要用HS Driver驱动高侧MOS管Q1导通,同时Q2关断。

假设没有自举电容Cboot,Q1的S极没有与GND连接,是浮空的,栅极输出高电平时Q1也无法导通;

当引入Cboot后,从图中可以看出Cboot并联在HS Driver电源两侧,HS Driver和高侧MOS管Q1共参考点B。

当HS Driver前端的Logic&PWM Latch模块控制HS Driver输出高电平(相对于参考点B为高)时,

MOS管Q1的栅源极电压Vgs为Cboot两端的电压,其值大约为VBR,Vgs(VBR) >Vth,MOS管Q1导通。

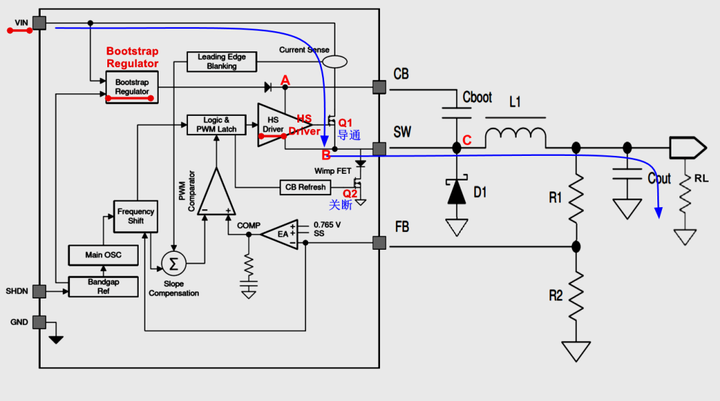

当高侧MOS管Q1导通,Q2关断时,由VIN为负载提供能量、对电感L1充电储能,如下图蓝色回路;

3、关于自举电压(Bootstrap Voltage)

当Buck芯片在高占空比或极轻负载下工作时,自举电容可能在相当长的时间内不会再充电;

自举电容两端的电压会到下降不足以驱动高侧MOSFET完全导通。

当自举电容两端的电压降至3.0V(LV2862)以下时,BOOT UVLO起作用;

该Buck芯片强制集成在其内部低侧的MOSFET(即Q2)周期性地导通,给自举电容充电,提升自举电容两端的电压,从而保证该Buck芯片在宽占空比范围内的操作。

可以理解为,

只要BOOT引脚到SW引脚的电压高于BOOT UVLO阈值,高侧MOSFET Q1就保持导通;

当BOOT到SW的电压降至3.0V以下时,高侧MOSFET Q1截止,低侧MOSFET Q2导通,以周期性地对自举电容充电。

以上为LV2862、SCT2600规格书中关于自举电压(Bootstrap Voltage)介绍的简述,详细介绍见下图或查阅器件规格书。

三、自举电容选型

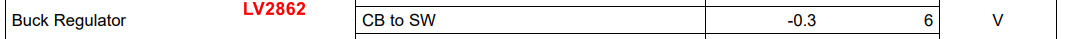

自举电容的容值,在原厂规格书的参考设计中一般是直接给出的,通常是0.1uF,耐压需要根据CB to SW的电压差来确定。

LV2862规格书中给出的CB to SW的电压差最大为6V,可以选10V/16V耐压的陶瓷电容

- 自举电阻

自举电阻主要是防止首次对自举电容充电时电流太大,起到限流作用;

自举电阻太大,高侧MOS管开启变慢;

自举电阻太小,高侧MOS管开启过快,会使SW有尖峰,EMI变差。

有些芯片的规格书中会明确给出自举电阻的计算方式,这里不再赘述,

三炮儿也没对自举电阻进行过具体的计算选型;

很多芯片已经将自举电阻内置,不需要工程师再额外选型。

更多笔记

LDO和DCDC有什么异同?

一文搞懂DCDC基础知识

LDO基础知识一文搞懂

上下拉电阻有啥研究的

为什么总是习惯将 1uF和 0.1uF 的两个电容并联摆放在电路中

这里是软磨硬泡公众号,号主三炮儿的硬件开发学习笔记、经验分享

学习分享以助能力增长,经验交流以期跻身一流

同名微信公众号:软磨硬泡

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/114943.html