大家好,欢迎来到IT知识分享网。

前言:上一讲完成了基本时钟和生成时钟的约束,确定了整个工程的时钟频率,本次内容要添加合理的 input 和 output delay, 把接口时序调整到一个最佳状态。

这里写目录标题

一、 I/O常用约束分类:

IO约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时(InputDelay 、OutputDelay)、上下拉电阻、驱动电流强度等。

1.input delay

–set_input_delay :设置管脚输入延迟

set_input_delay -clock clk0 5 [get_ports din]

含义:是din 端口与 clk0 关联,输入延迟约束为 5ns。

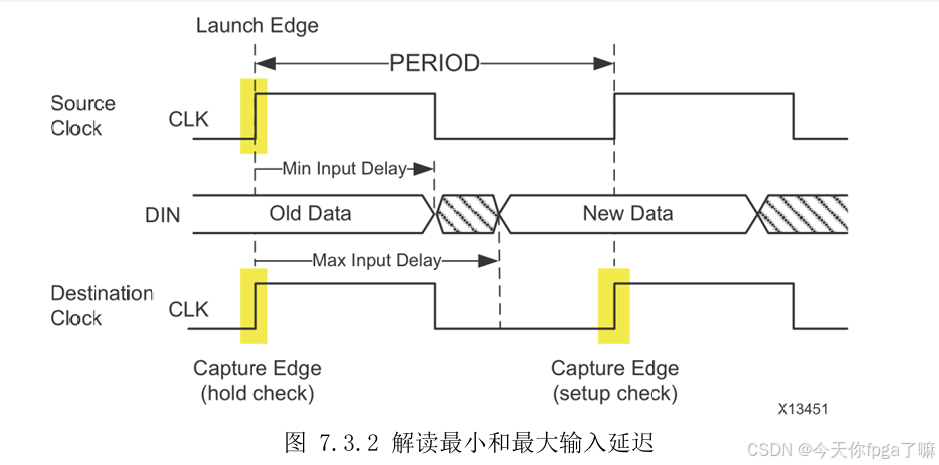

一般分为两类(MAX MIN):

set_input_delay -max -clock sysClk 5.4 [get_ports DIN]

含义:设定最大建立时间为5.4ns,即设计工具将确保数据在时钟边沿到来之前的 5.4 ns 期间保持稳定。

set_input_delay -min -clock sysClk 2.1 [get_ports DIN]

含义:设定最小保持时间为2.1ns,即设计工具将确保数据在时钟边沿到来之后的 2.1 ns 期间继续保持稳定。

2.output delay

set_output_delay :设置管脚输出延迟

set_output_delay -min -0.5 -clock CLK [get_ports DOUT]

含义:表示设计内部直到DOUT 管脚的延迟必须至少超过0.5ns,才能满足保持时间

的需要。

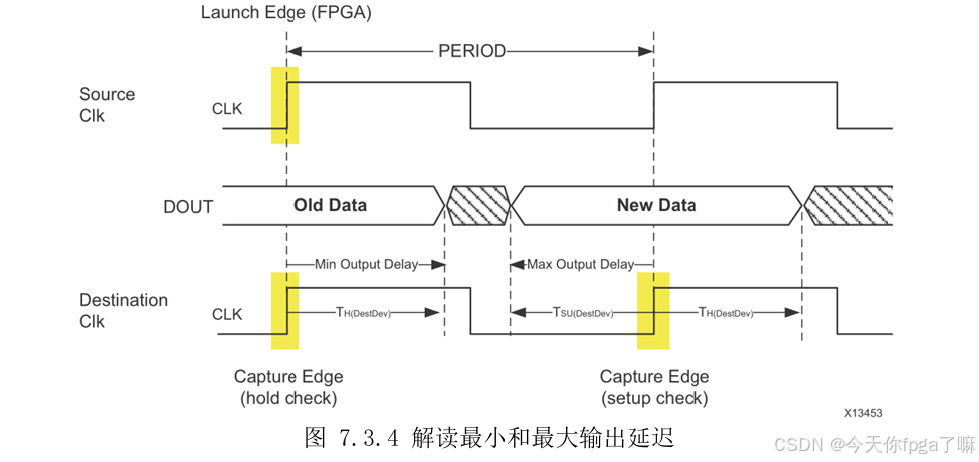

一般分为两类(MAX MIN):

set_output_delay -max -clock sysClk 2.4 [get_ports

DOUT] 含义:设定最大建立时间为2.4ns,即设计工具将确保输出信号 DOUT 从时钟边沿起,最多延迟 2.4 ns

才变为有效。set_output_delay -min -clock sysClk -1.1 [get_ports DOUT]

含义:设定最小保持时间为1.1ns,-1.1 ns 表示数据可能在时钟边沿之前最多 1.1 ns 就变为有效。

一、项目回顾

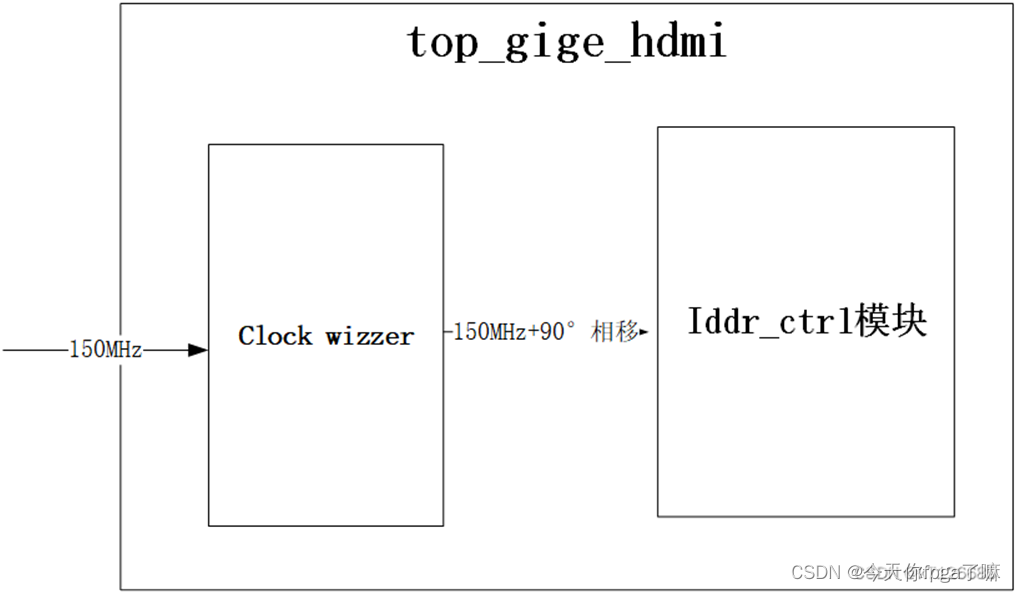

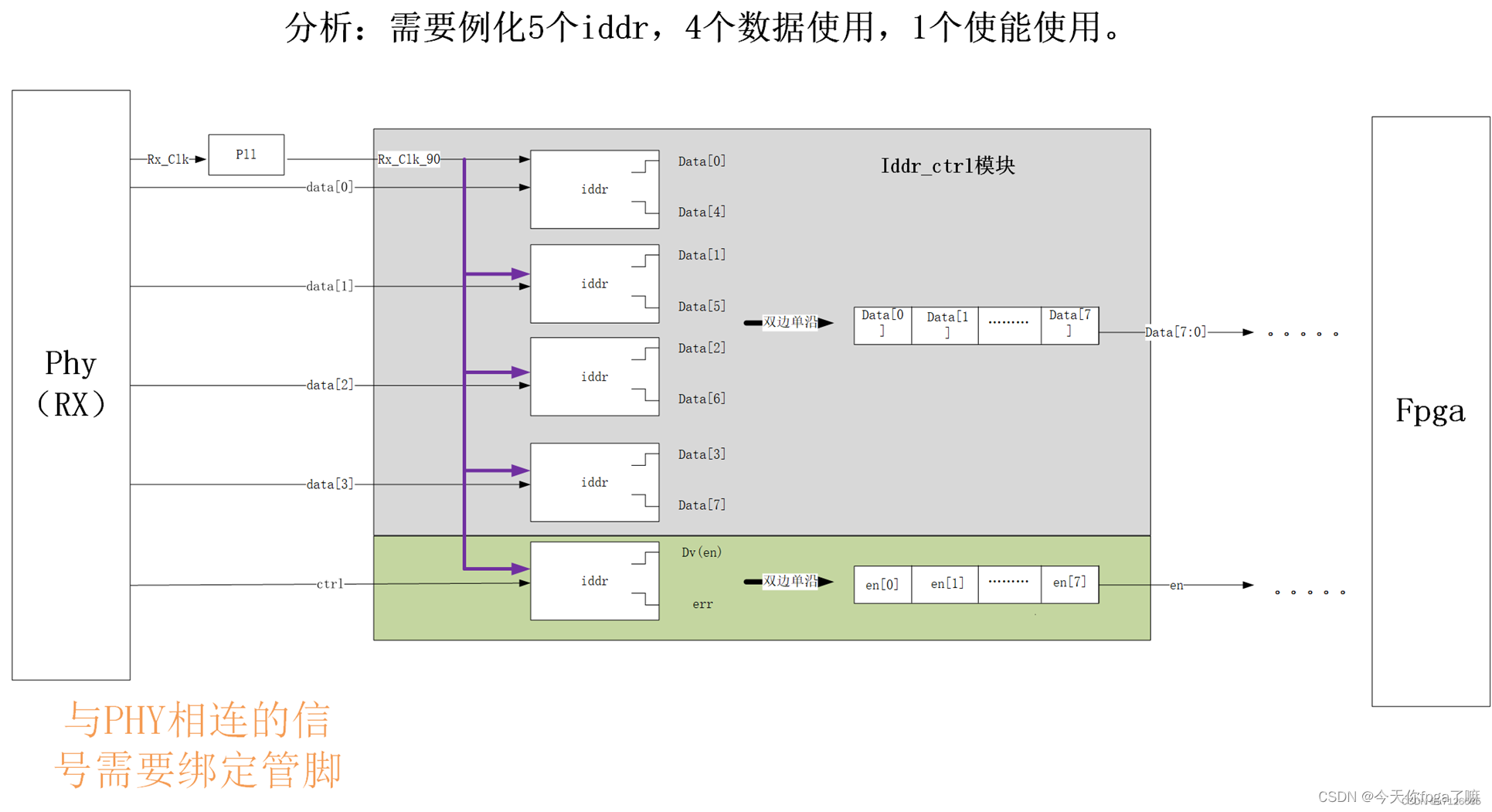

本次使用的项目案例中,时钟关系如下:

150Mhz的主时钟,采用DDR双沿采样的方式进行数据传输。

二、input delay 约束

1.基础理论

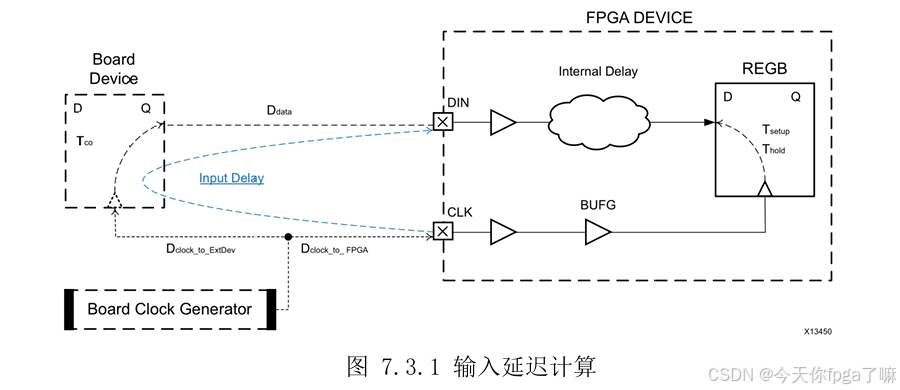

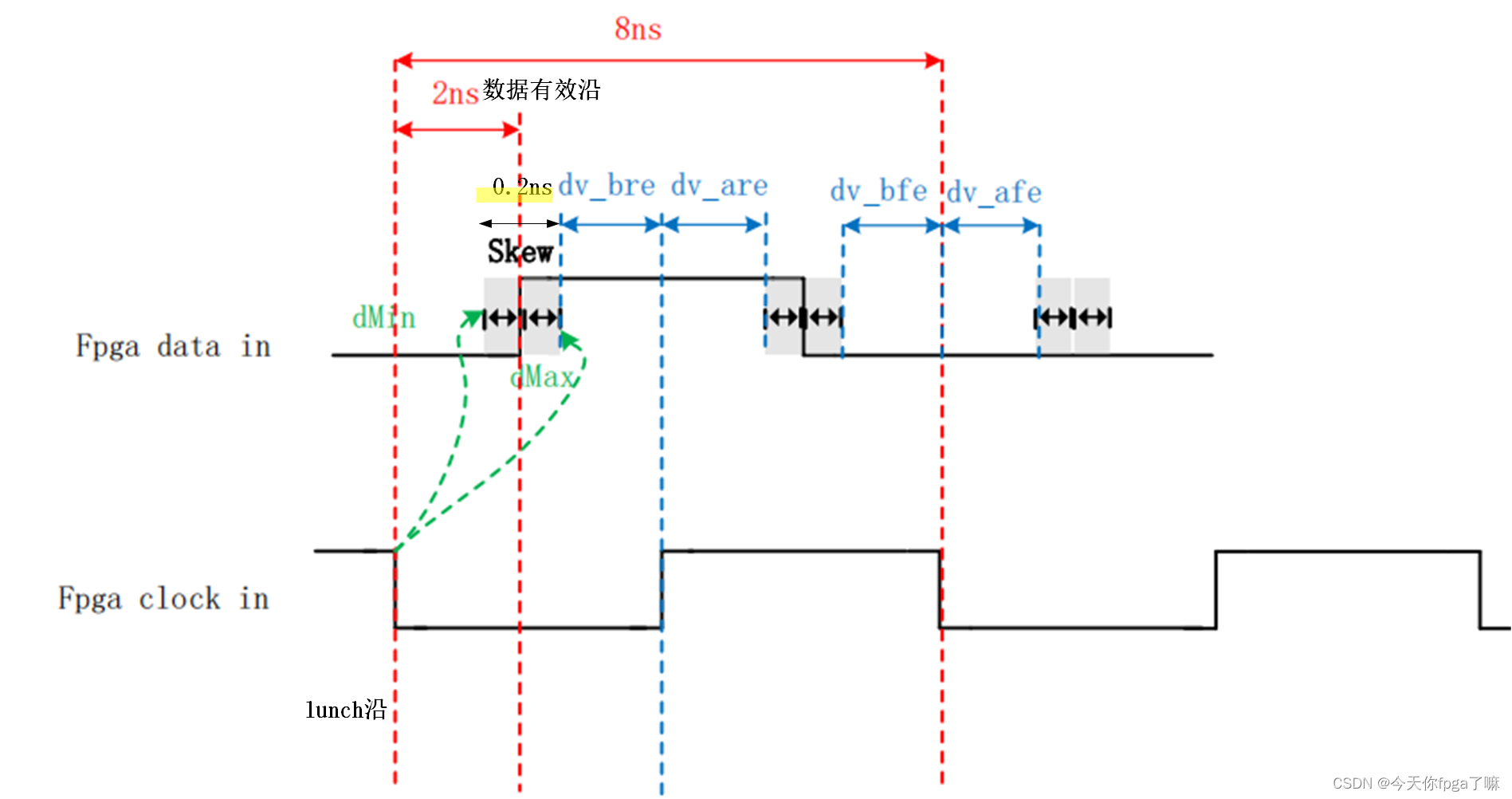

Input delay 需要约束的是发射沿 lunch 沿到数据有效的延迟

计算公式如下:

2.实操方法一:输入时钟经过PLL后调整相位。

关于input delay约束,有两种操作方式:

1.输入时钟经过PLL后调整相位。

2.输入数据延时

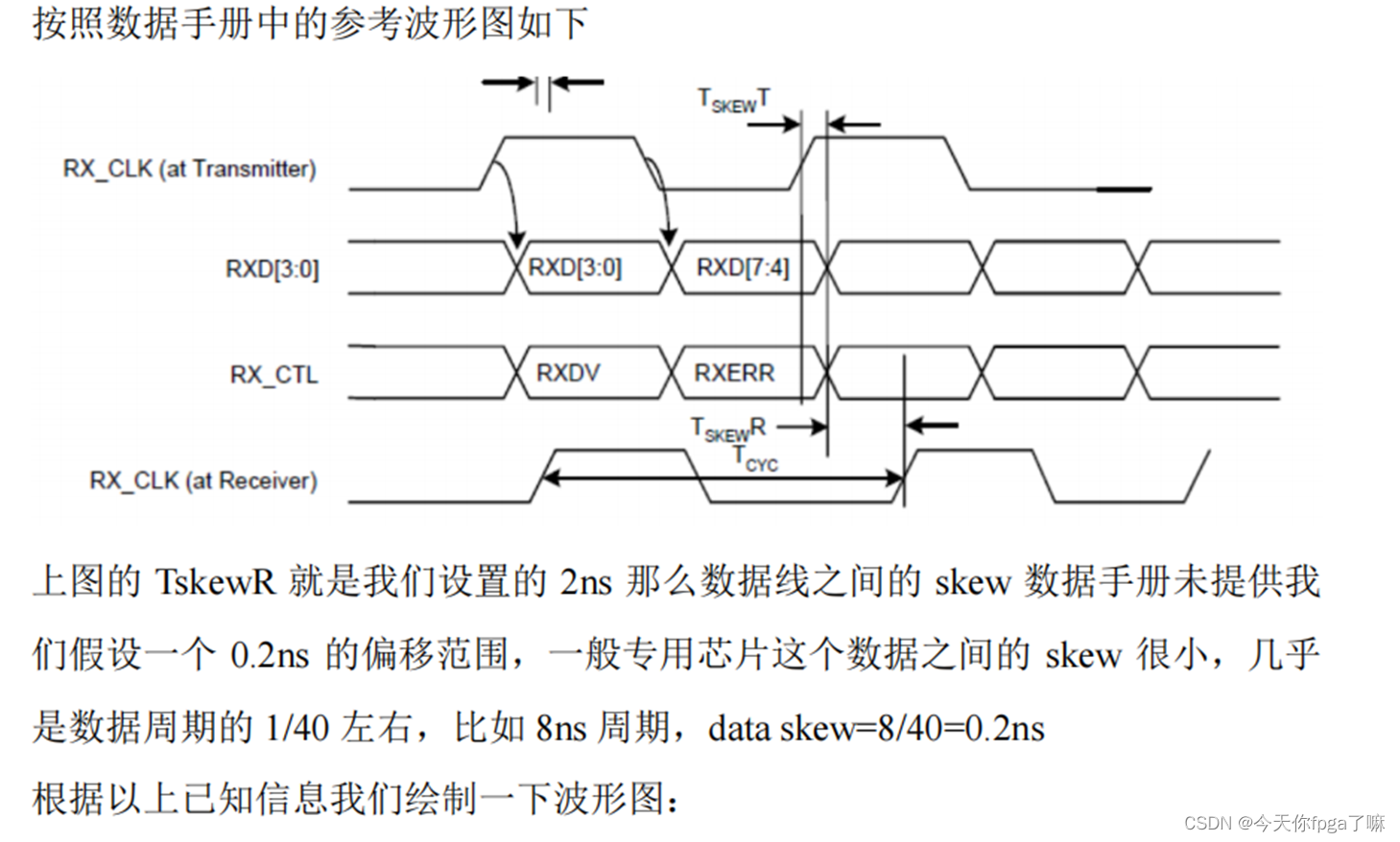

且:本项目中是DDR双沿采样方式,因此需要双沿(上升沿,下降沿都需要)进行约束设置。

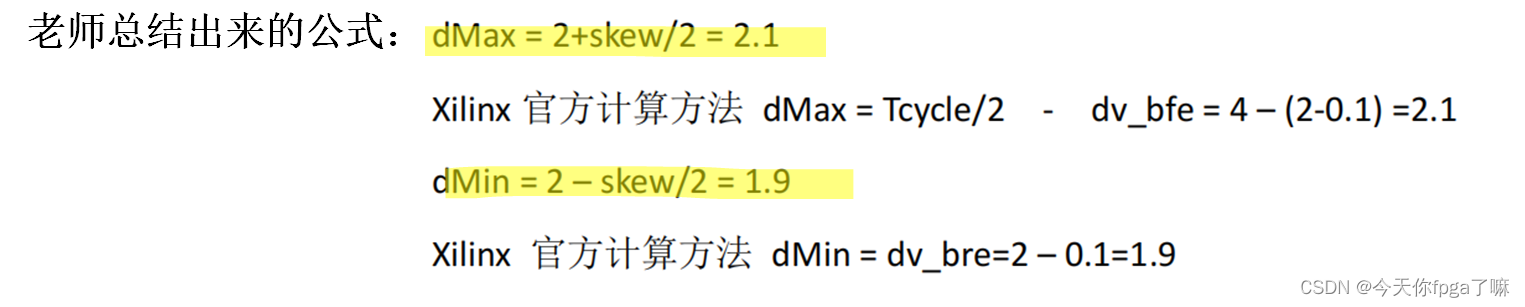

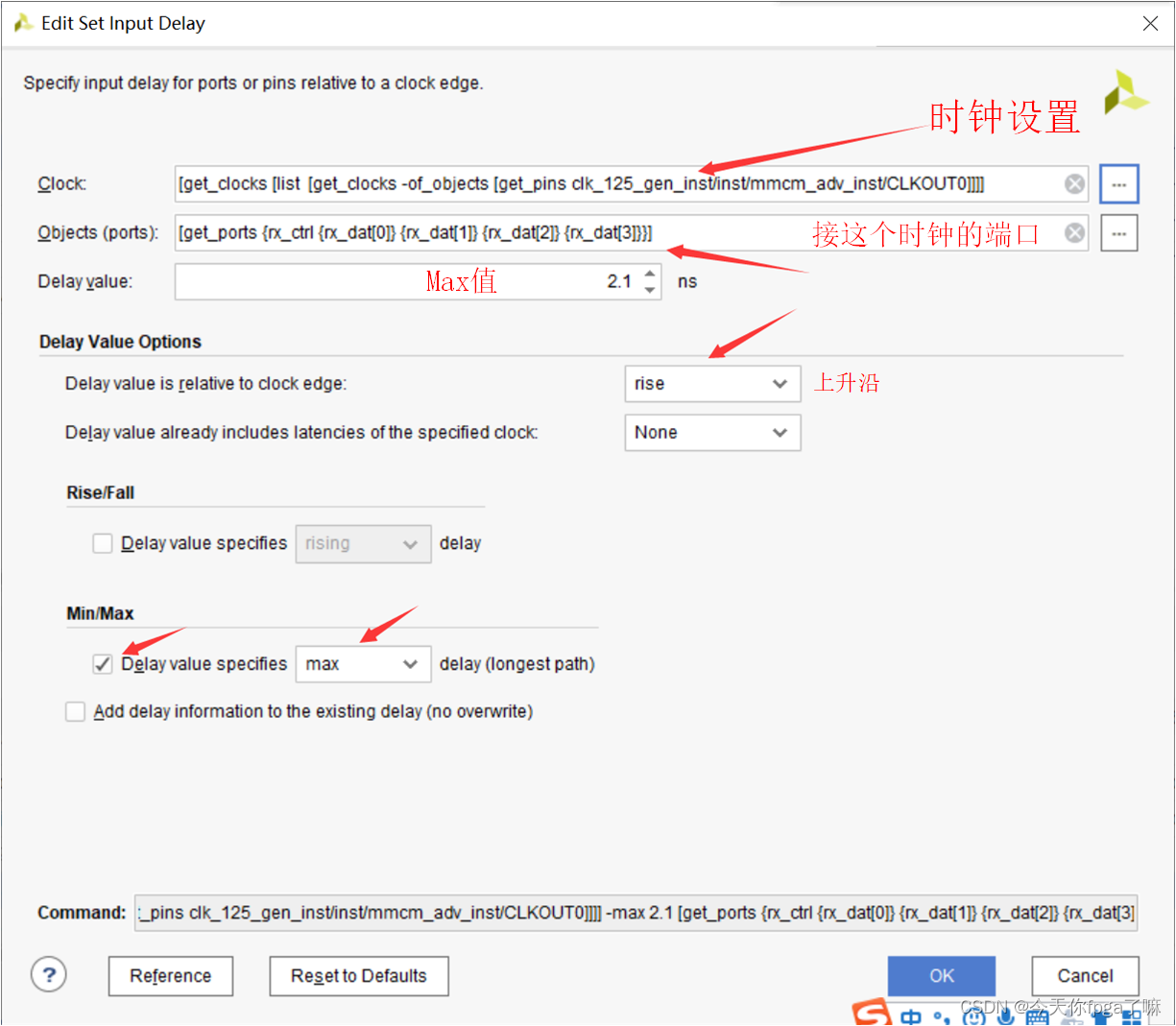

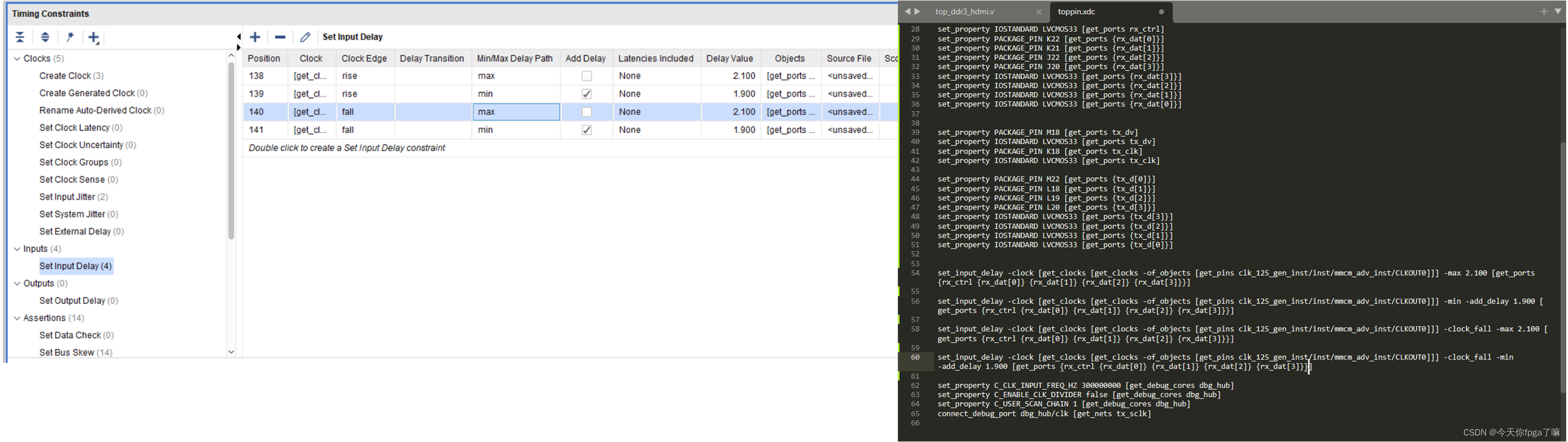

上面得到参数设置: max = 2.1 min =1.9

1.上升沿设置:

- 先设置上升沿的 max delay 用于建立时间分析

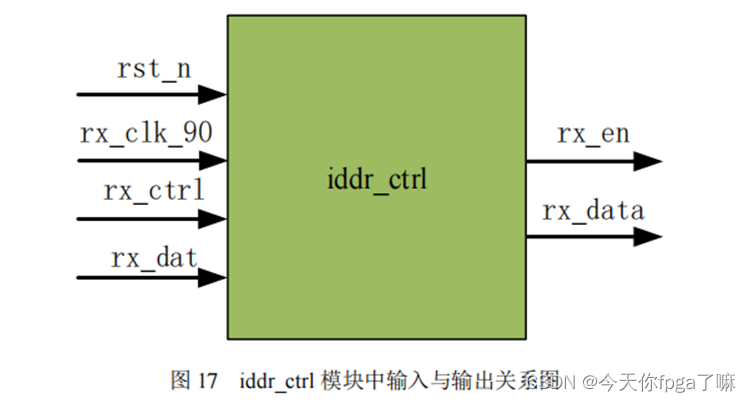

(这里要设置时钟和数据源端口,时钟为 PLL 移相之后的时钟 rx_clk_90.)

- 再设置上升沿的 min delay 用于保持时间分析

(同样这里要设置时钟和数据源端口,时钟为 PLL 移相之后的时钟 rx_clk_90.)

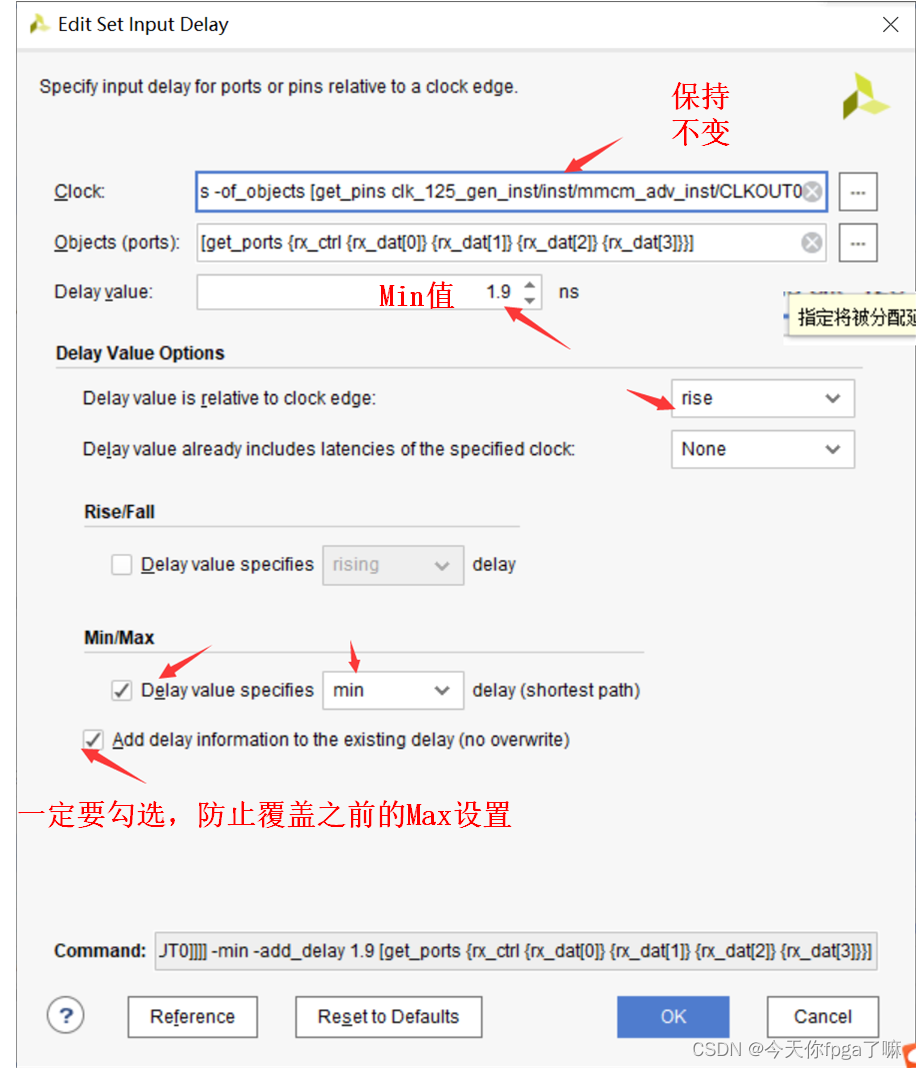

2.下降沿设置:

将上升沿改为下降沿即可,其余操作与上述一致。

3.查看效果

- 完成设置后要保存设置文件,自动更新到XDC文件,效果如下:

(这里需要注意:打开 xdc 文件看看是否把之前的管脚约束覆盖了,如果覆盖了需要手动补充上之前的管脚约束)

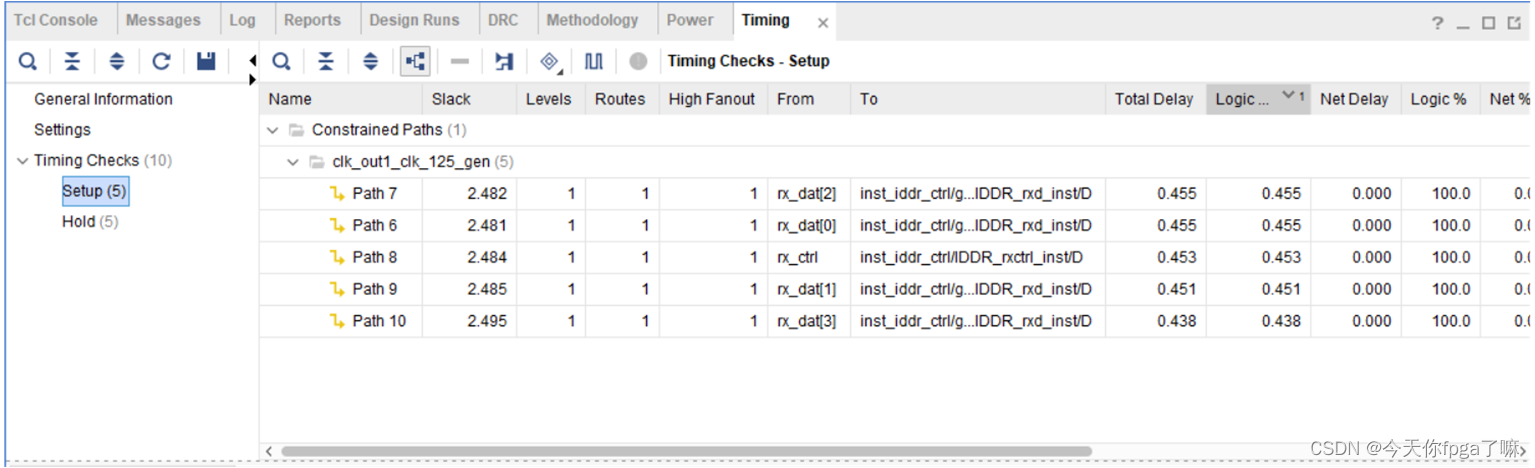

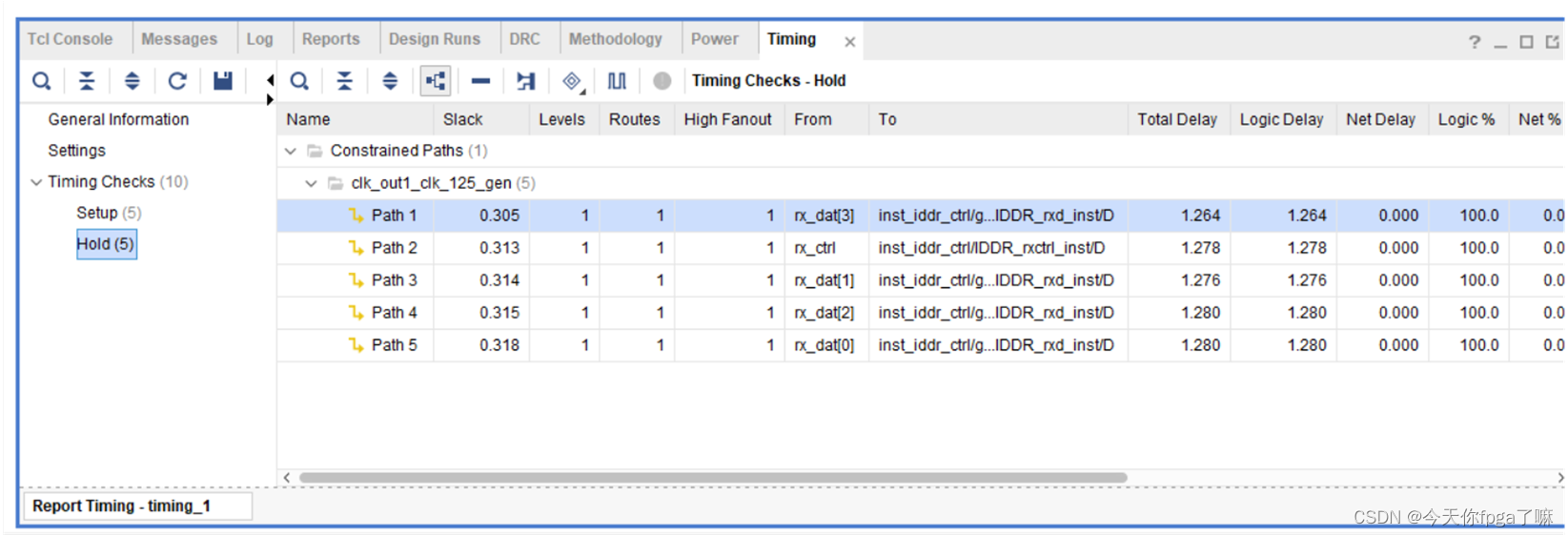

时序分析报告如下:

- 需要重新综合工程和布局布线工程,分析时序分析报告。(此处忘记保存图了)

分析目前的时序特点是:建立时间余量较大,但保持时间余量较小,有时序违例的风险。

问: 那如何进一步进行优化呢?

答:目前我们是通过输入时钟 PLL 调整相位达到的时序要求,此外,我们还可以进行数据延时(input

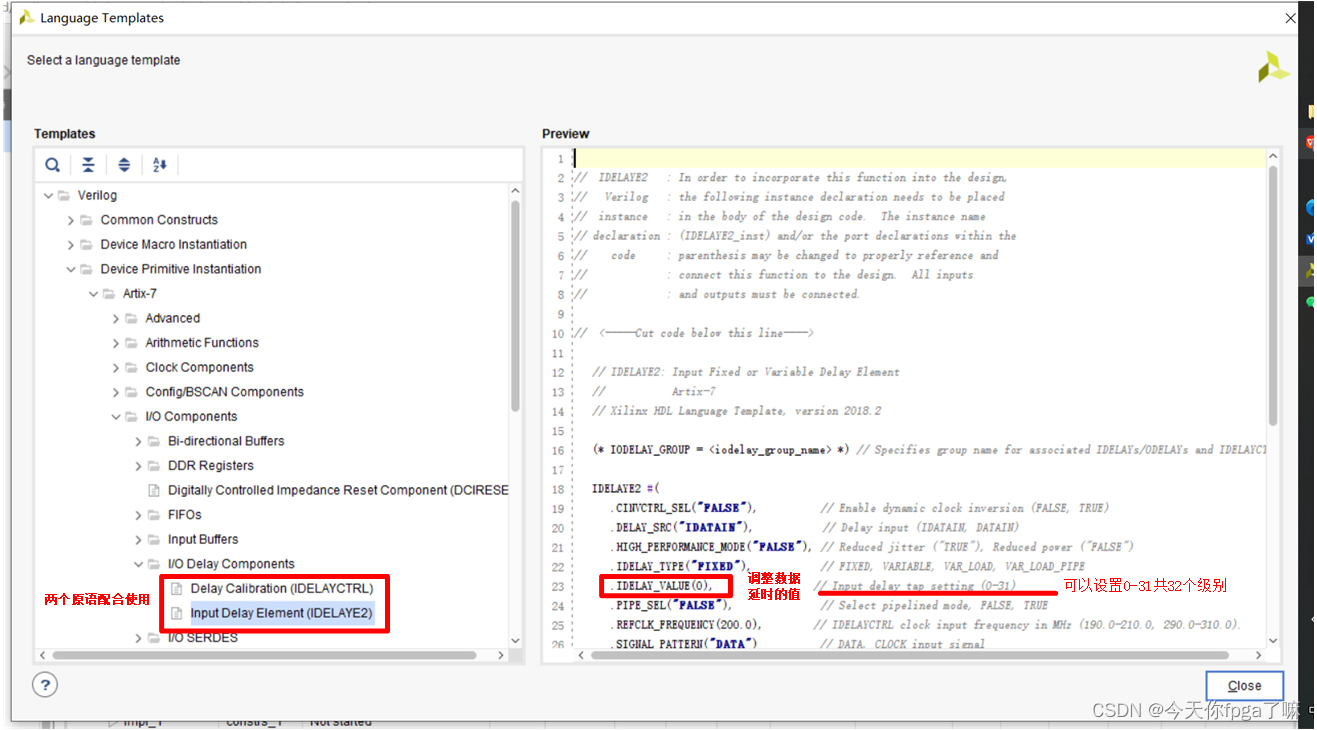

delay control)。 需要用到IDELAYE2原语。 IDELAYE2原语有两种配置模式:1.动态(自动调整匹配)2.静态(固定的延迟值)

3.实操方法二:数据延时

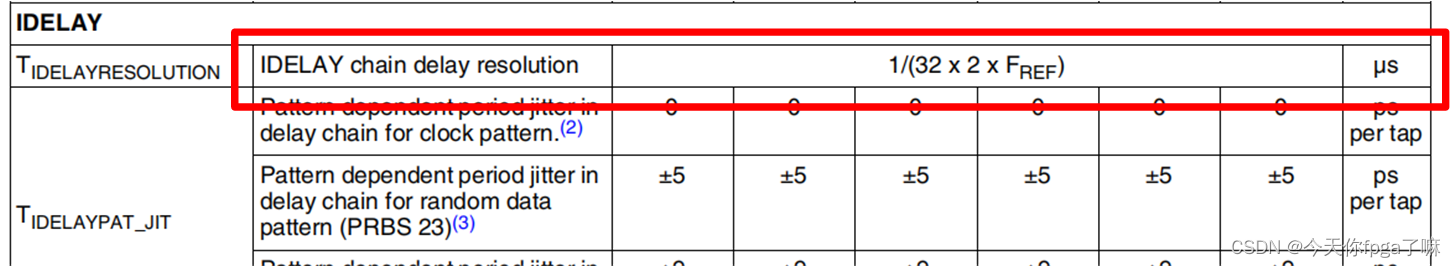

注意:每单位增加的延时值需要具体查看手册

本项目的F(REF) =200mHZ,则每单位增加78.125ps

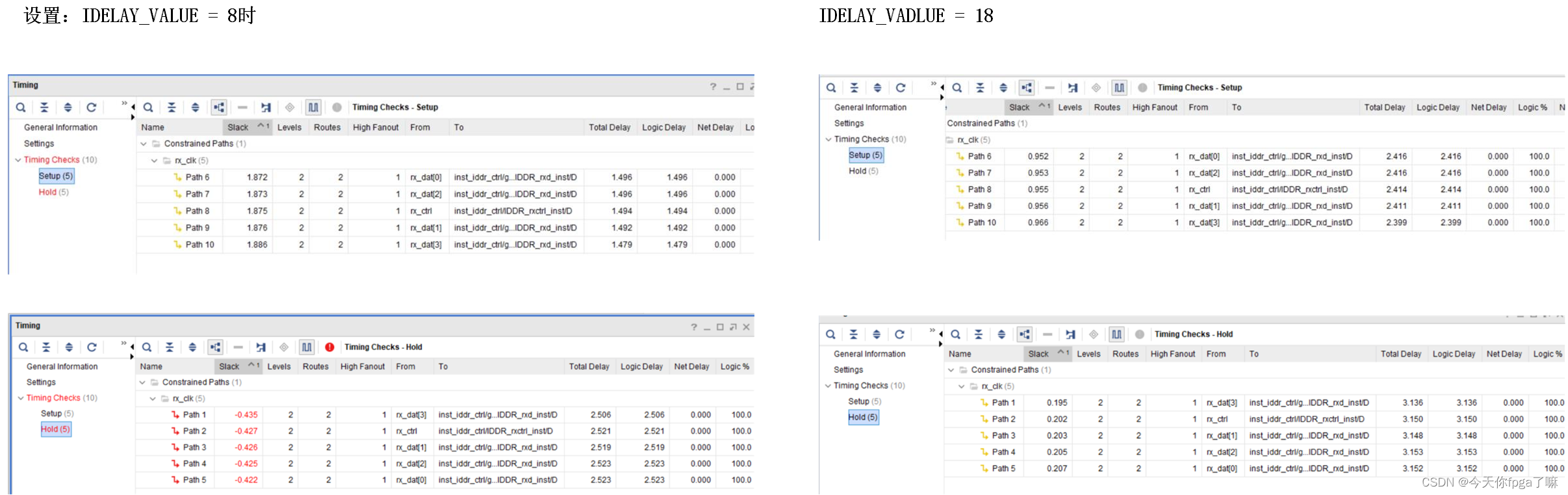

对比不同value值的时序报告:

结论:可以看到IDELAY_VALUE增大,建立时间余量减小,保持时间余量增大

二、output delay 约束

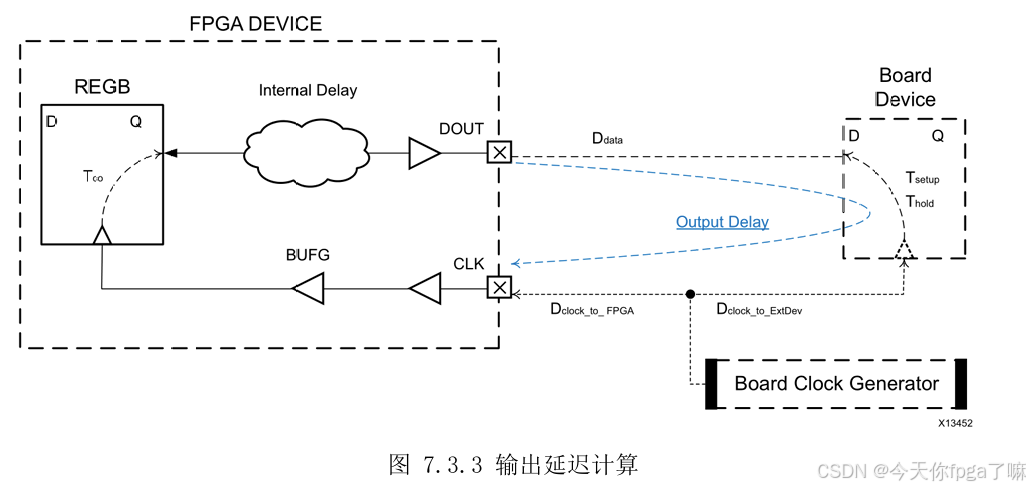

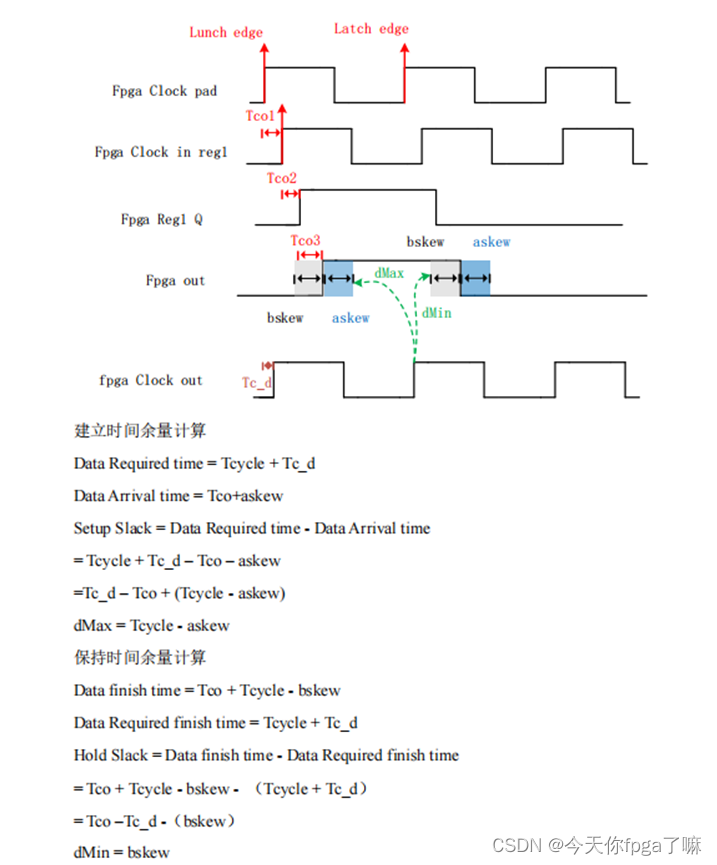

1.基础理论

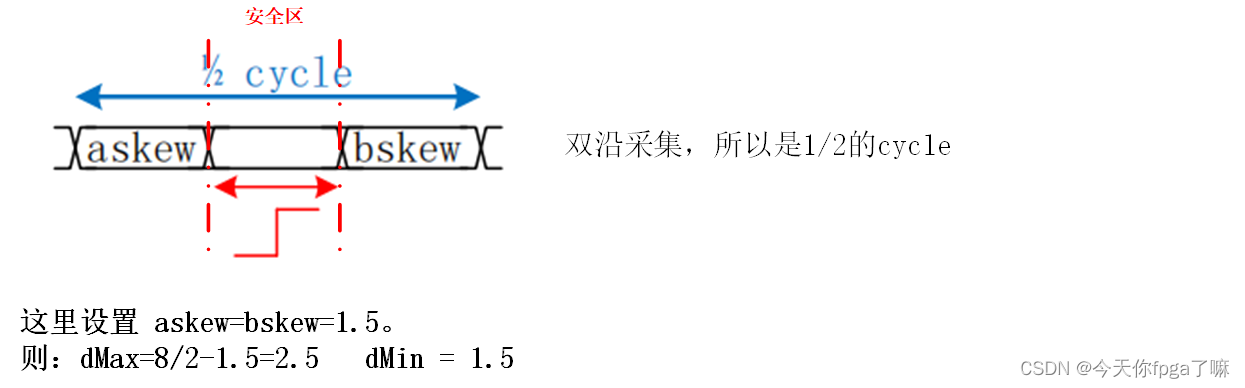

首先回顾之前讲的output delay一些关键参数的计算方式:

注意:这里设置的 bskew 和 askew 和 input delay 是不一样的思想。 input delay 是根据上游器件的参数决定的。 而 output delay 是我们设置约束使得我们的时钟不要落到 skew的区间内,这样我们可以通过调整skew 的值使时钟在一个中心位置。

2.实操方法一:输入时钟经过PLL后调整相位。

和input delay一样,output delay也包括PLL时钟相移和数据延迟两种。

PLL时钟相移的具体操作和input delay一致,关键在于找对output delay的源时钟。

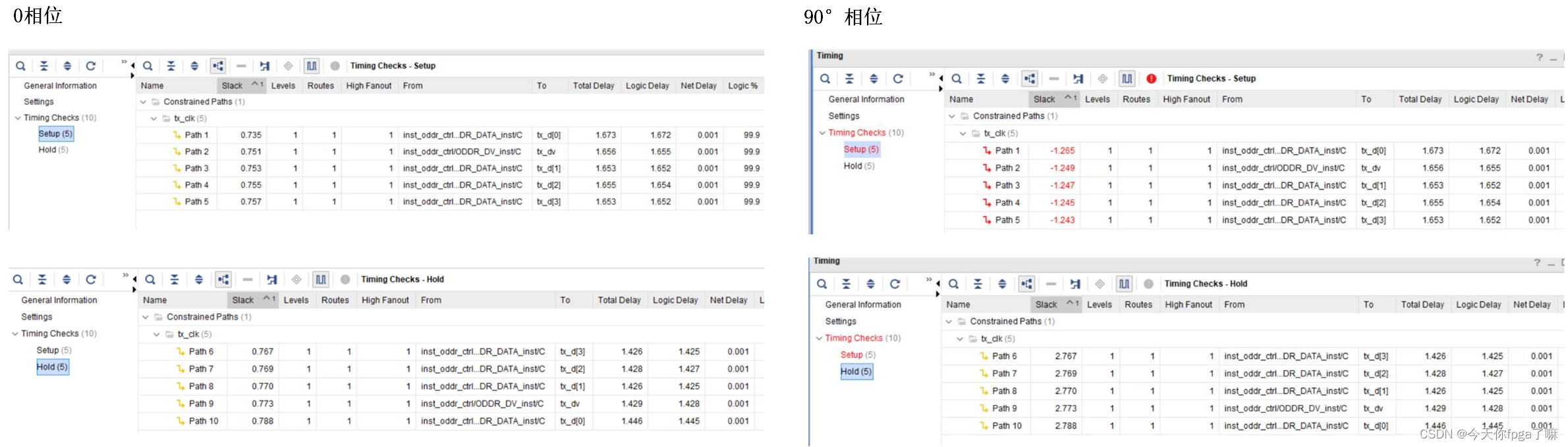

这里对比一下0相位时钟和90°相位时钟的时序报告

3.实操方法二:数据延迟

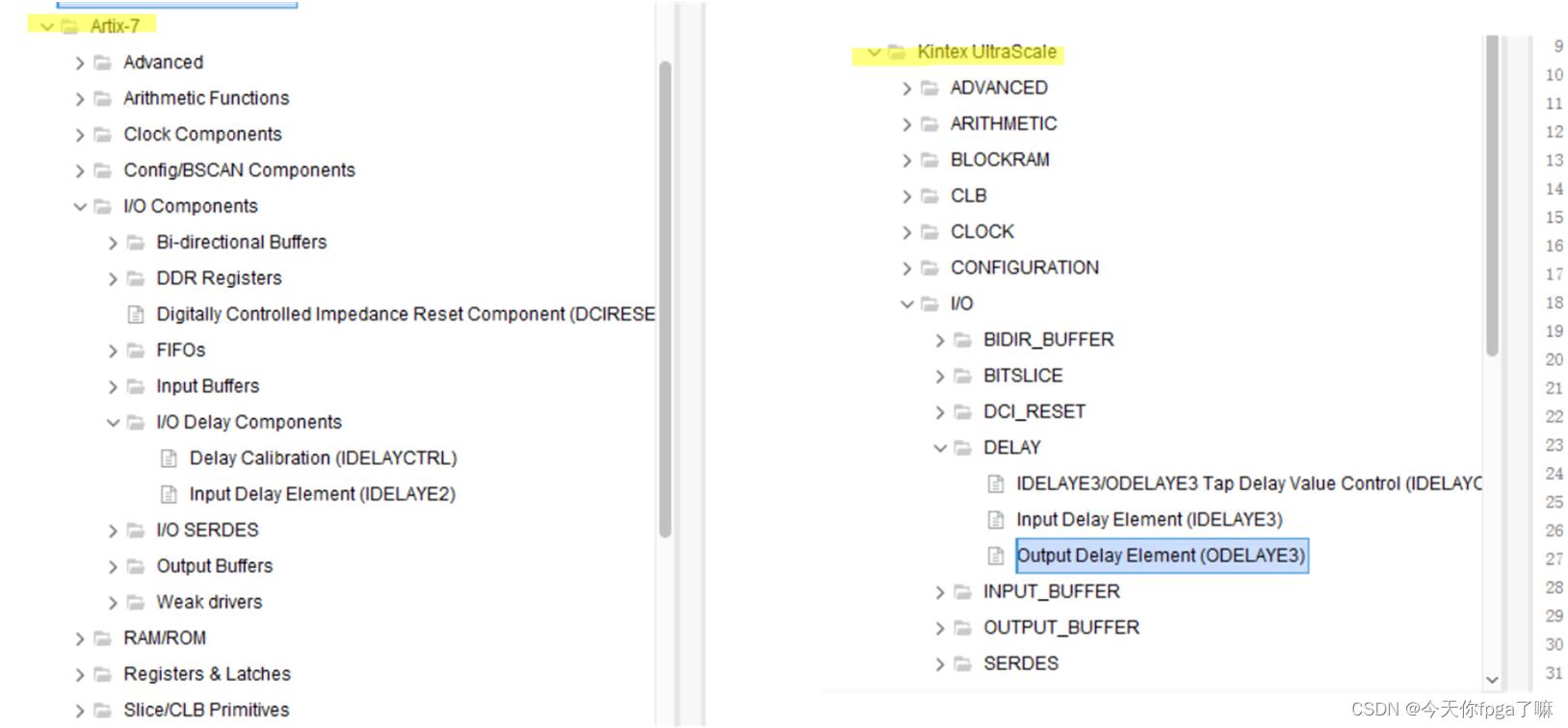

但output delay使用数据延迟的方式需要看具体使用的bank类型,例如下图中ARTIX-7没有output delay的原语,而Kintex UltraScale就有。

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/146213.html