大家好,欢迎来到IT知识分享网。

系列文章目录

1.元件基础

2.电路设计

3.PCB设计

4.元件焊接

5.板子调试

6.程序设计

7.算法学习

8.编写exe

9.检测标准

10.项目举例

11.职业规划

1、何为EMC整改

EMC整改就是指产品在功能调试或EMC测试过程中出现问题后所采取的弥补手段。

首先我们从EMC认证测试项目说起,EMC认证测试主要包含两大项:EMI(干扰)和EMS(产品抗干扰和敏感度)。

通过这些测试项我们可以看出EMC测试主要围绕产品的电磁干扰和敏感度两部分,一旦产品不符合安全认证标准需要EMC整改时,我们就需要通过一些措施和方法来进行整改。

2、EMC整改流程

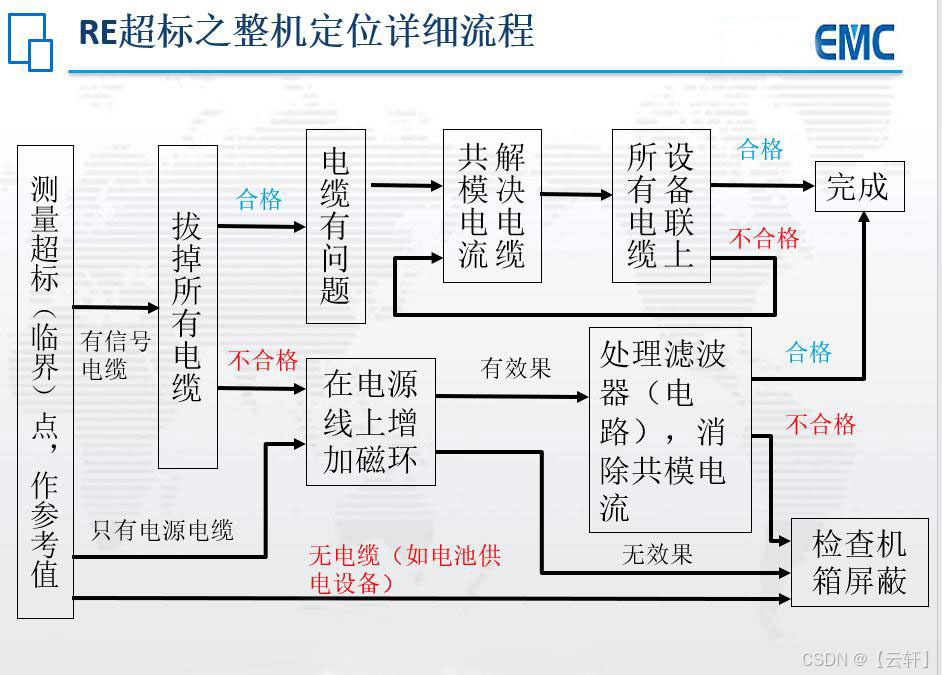

①、RE超标整改流程

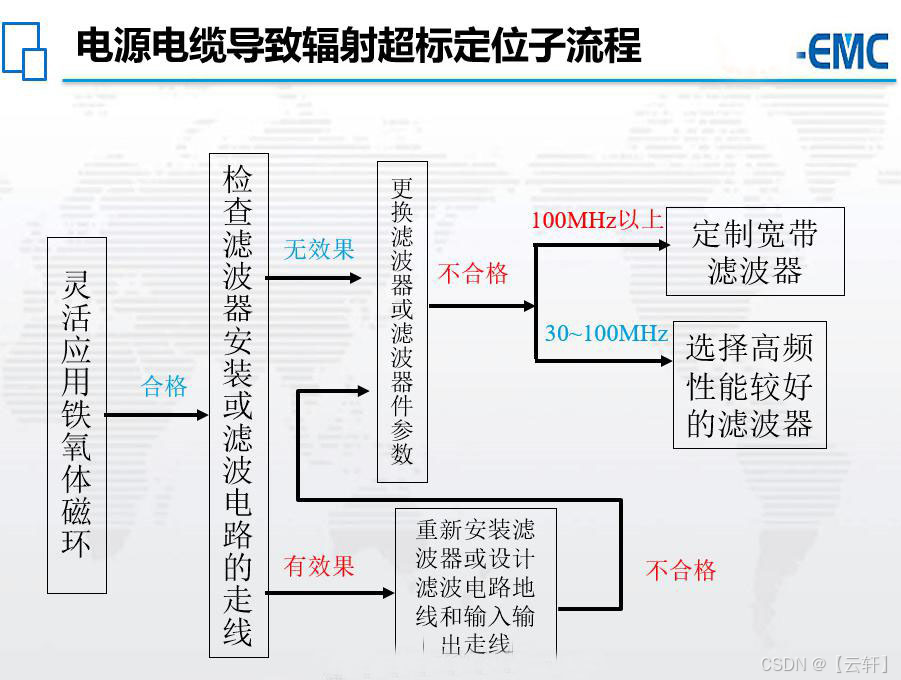

②、电源电缆导致辐射超标定位子流程

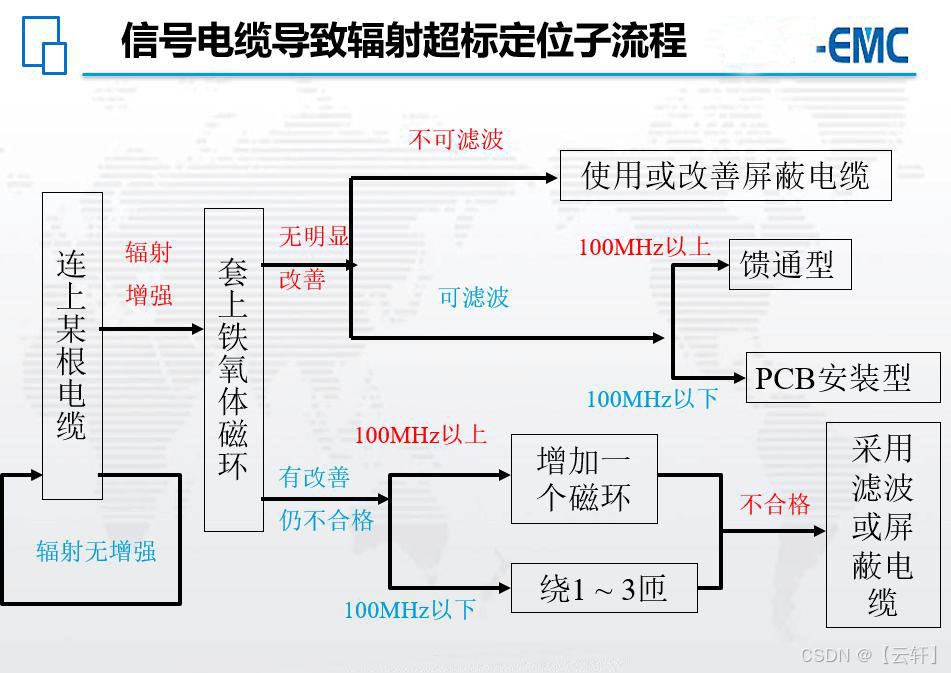

③、 信号电缆导致辐射超标定位子流程

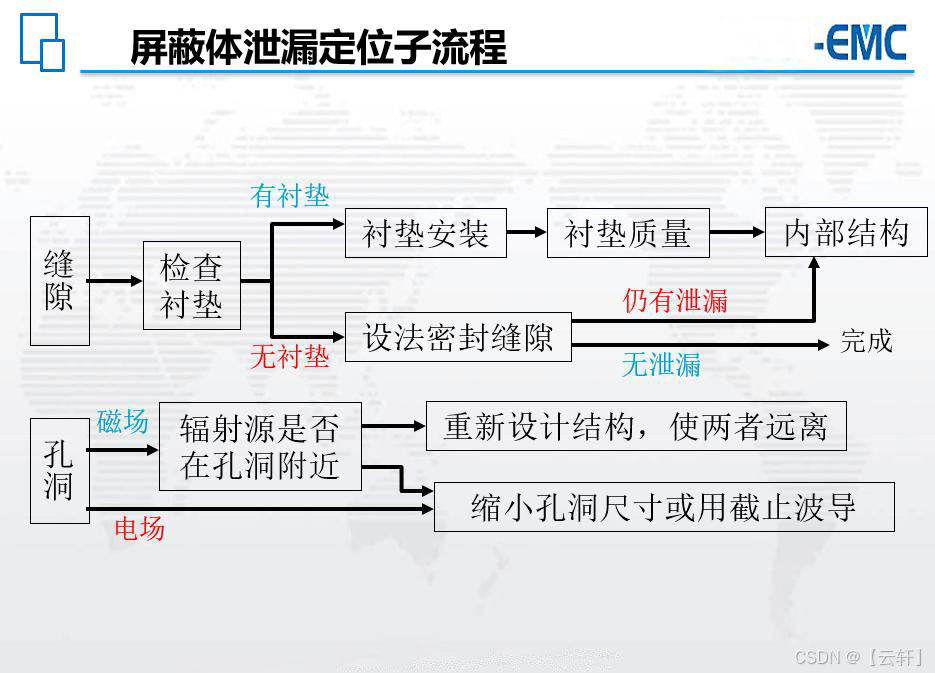

④、屏蔽体泄漏整改流程

3、整改方向

谈到EMC整改,我们常说的是EMC三要素,即敏感设备,耦合路径和干扰源。干扰源往往可以通过近场探头,排除法确认,干扰路径往往较难判定,干扰通常分为共模干扰和差模干扰。

共模干扰又分为电压驱动型,电流驱动型和磁场耦合型这三种类型,电压驱动型最典型的案例是干扰通过耦合到散热器向外辐射,电流驱动型典型案例是通过公共阻抗耦合到别的回路中,磁场耦合型较为常见,任何一个电流回路都会形成耦合,不同的是,恒定的电流形成的恒定的磁场,恒定的磁场不会再形成电场,变化的电流形成变化的磁场,干扰更为明显,后者也是电路中常见的。

差模干扰可以按照SIf*f/D进行排公式仅作参考,整改可以按照这个方向进行,其中,S-回路面积,I-电流大小,f-干扰频率,D-干扰源到被干扰源的距离。

根据多年EMC整改经验,针对以上分析,可以用“消除干扰源”,“堵”,“疏”确定整改方向,作为技术指引。

①、“除”

个人认为,消除干扰源是EMC整改最简便的方法,可以达到一劳永逸,消除干扰源通常分为:展频,“跳频”,有源钳位吸收,无源RC吸收电路,展频即将频率通过扩展频差,将能量分散,需要注意的是,对于基频,随着谐振倍数的增加,效果会越来越明显,展开的宽度会更宽,即如果对100KHz的频率进行展频处理,那么500KHz的谐振展频效果会比100KHz的展频效果更加明显。“跳频“即通过调整干扰频率,避开测试的频段,但是需要注意的是需要重新测试完整的频段,防止出现别的频段超标的现象出现,常见的有在测试低频段时,因开关电源导致辐射超标,通过增加开关电源的频率,从而避开该频段。RC吸收电路主要应用于吸收LC谐振电路。

②、“堵”

“堵”,抛开干扰源的部分,我们接下来需要注意的整改方向是“堵”还是“疏”,这个看似简单,但是可以为我们确定整改方向,避免出现胡乱使用各种整改方法,到头来还是思绪全无,EMC整改本身就是极大考验个人综合能力的,可能会出现花了一个月甚至更长的时间,但仍然全无进展,所以整改时确定方向是极其重要的。对于“堵”,实质就是堵干扰路径,干扰路径通常有公共阻抗干扰&感性耦合&容性耦合&空间辐射,堵公共阻抗干扰即增大干扰源对外路径的阻抗,通常有电源输出串联磁珠,电感,信号输出支路串联电阻,典型案例有对待晶振的地处理,通过可以采取在元器件层,挖孔该区域同时单点接地,避免该干扰流入大地,同时在对应的其他层留下地平面提供回路:“堵“容性耦合措施包括增加干扰源和被干扰源距离,减小干扰源和被干扰源的有效耦合面积,选择介电常数较小的材料隔在干扰源和被干扰源之间;“堵”感性耦合措施包括增加干扰源和被干扰源距离,减小干扰源和被干扰源之间的耦合有效面积,调整干扰源和被干扰源的方向,比如两者产生的磁场方向彼此垂直可达到“堵“感性耦合的效果;”堵“空间辐射,目前最为有效的即是用金属屏蔽罩接地的方法,实质上电磁屏蔽也属于消除干扰源,因为电磁屏蔽实质是引起阻抗失配,从而形成反射损耗,插入损耗,插入再反射损耗。

③、“疏”

4、常见EMC整改方法

①、排除外界因素

(2)确认测试布置是否满足标准要求。

②、 宽带噪声抑制方法

③、滤波器是否良好接地

(1)如果设备有一体化滤波器,检查滤波器的接地是否良好,接地线是否尽可能短;

④、单层板或双层板中电源走线的处理

增加电容为电源去耦。

⑤、多层板中电源平面层的处理

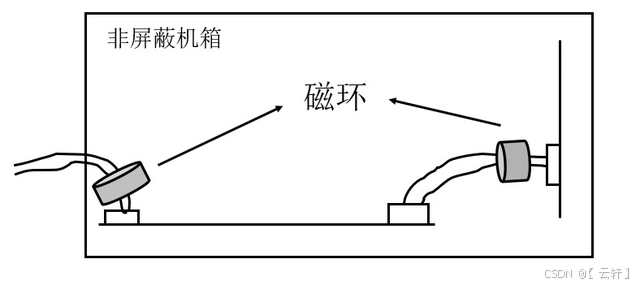

⑥、非屏蔽设备内电源线的处理

在电源线上套磁环进行比对验证,以后可以通过在单板上增加共模电感来实现,或者在电缆上注塑磁环。

⑦、独立窄带尖峰噪声抑制方法

问题整改:有针对性地处理确定的目标时钟源。

⑧、时钟源外壳是否接地

⑨、时钟输出匹配设计

时钟的输出根据信号质量的要求使用始端匹配,适当变换时钟沿,减小发射。

需要注意的是,使用时钟驱动器时,时钟驱动的时钟输出同样需要匹配。

⑩、时钟源的电源滤波设计

⑪、单层板或双层板上时钟线的处理

5、EMC整改的一些小建议

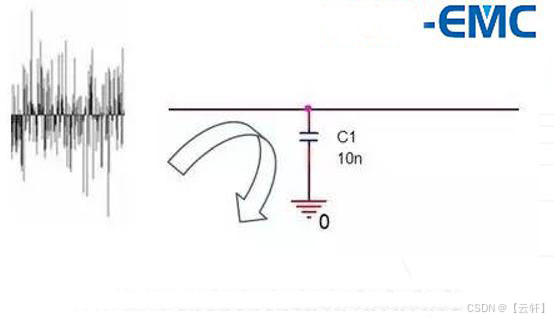

①、电容的滤波作用

即频率f越大,电容的阻抗Z越小。当低频时,电容C由于阻抗Z比较大,有用信号可以顺利通过;当高频时,电容C由于阻抗Z已经很小了,相当于把高频噪声短路到GND上去了。

②、电容滤波在何时会失效

③、LC滤波何时使用

④、PWM频率到底是多少

⑤、如何将原理图和PCB对应起来

由于细分工种的问题,原理图和PCB被割裂开来,由两组人进行分工作业:

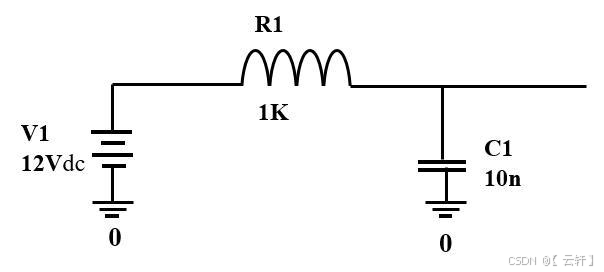

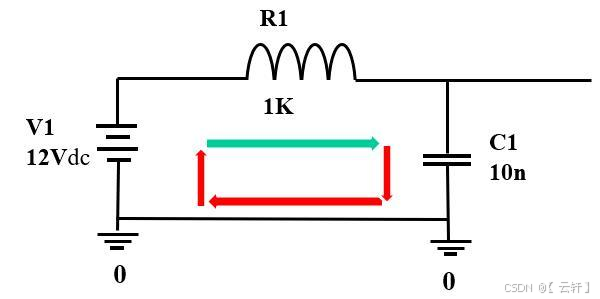

例如在原理图上有如下的电路:

其隐含一个问题就是在PCB上其实V1的负极和C1的负极是有一条线(PCB layout工具软件中用的词比较准确,Trace,踪迹/轨迹)。往往在设计阶段A->B->C是都会关注的。如果EMC出现问题,除了要在原理图上查找电路参数的问题,还需要特别关注C->D,即回流路径。

如果回流路径不顺畅,会造成信号的畸变。

比如在EMC试验时,MCU的ADC采集到的信号被干扰到了,则除了在原理图上分析外,在PCB上讲该信号高亮出来,然后再耐心寻找该信号的回流路径是否有不顺畅的地方:对着信号线头脑中想象回流路径,有点意识流的感觉。

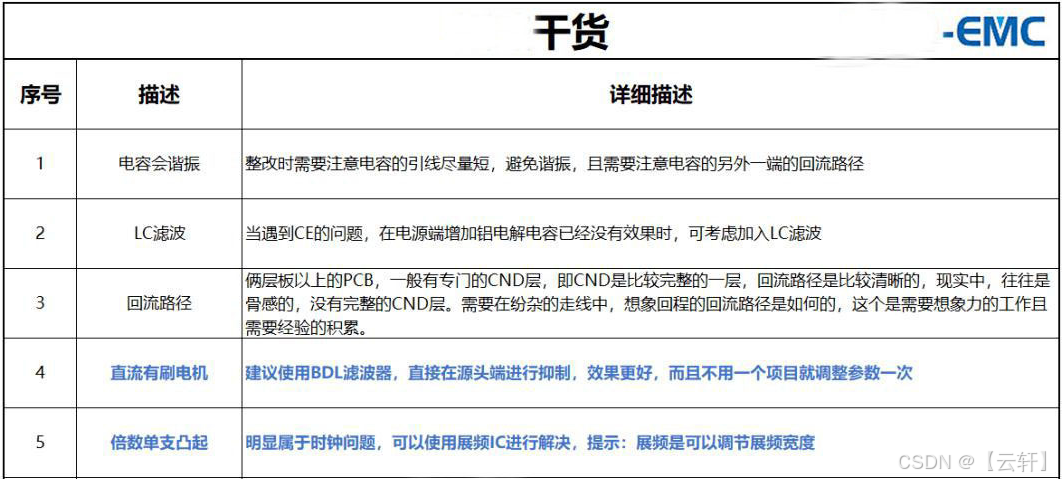

⑥、总结

免责声明:本站所有文章内容,图片,视频等均是来源于用户投稿和互联网及文摘转载整编而成,不代表本站观点,不承担相关法律责任。其著作权各归其原作者或其出版社所有。如发现本站有涉嫌抄袭侵权/违法违规的内容,侵犯到您的权益,请在线联系站长,一经查实,本站将立刻删除。 本文来自网络,若有侵权,请联系删除,如若转载,请注明出处:https://haidsoft.com/111315.html